# **Measurement of Fractional Impedance using Switched Capacitor Circuits**

By

Shashank Kalvacharla

Submitted in partial fulfilment of the requirements

For the degree of Master of Applied Science

at

Dalhousie University

Halifax, Nova Scotia

2017

© Copyright by Shashank Kalvacharla, 2017

# Dedicated to my cute little niece Sanvi, my Parents, Family, Friends and Well wishers

## TABLE OF CONTENTS

| List of Tables                                                       | vii  |

|----------------------------------------------------------------------|------|

| List of Figures                                                      | vii  |

| Abstract                                                             | ix   |

| List of abbreviations used                                           | xi   |

| Acknowledgements                                                     | xiii |

| Chapter 1 Introduction                                               | 1    |

| 1.1 Motivation                                                       | 1    |

| 1.2 Fractional Order Systems and Circuits                            | 1    |

| 1.2.1 Fractional order systems.                                      | 2    |

| 1.2.2 Fractional order circuits                                      | 3    |

| 1.3 The Cole-Cole Impedance Model                                    | 4    |

| 1.3.1 Integrator based Setup of Cole-Cole Impedance Model            | 7    |

| 1.4 Thesis Contribution                                              | 9    |

| 1.4.1 Implementation of CPE using low voltage SC-BDI                 | 9    |

| 1.4.2 Implementation of CPE using low voltage SC-CDI                 | 9    |

| 1.4.3 Minimizing the CPE errors using optimizing technique           | 9    |

| 1.5 Thesis Organization                                              | 10   |

| Chapter 2 Literature Review                                          | 11   |

| 2.1 Constant Phase Element (CPE)                                     | 11   |

| 2.2 Existing Realizations of Constant Phase Element                  | 12   |

| 2.2.1 CPE realization using passive elements                         | 12   |

| 2.2.2 CPE realizations using operational transconductance amplifiers | 14   |

| 2.2.3 CPE realizations using current feedback operational amplifier  | 16   |

| 2.3 Rational Approximations                                          | 18   |

| 2.3.1 Continued Fraction Expansion (CFE)                         | 19 |

|------------------------------------------------------------------|----|

| 2.4 Various schemes of Switched-capacitor (SC) based integrators | 20 |

| 2.4.1 Lossless Discrete Integrator (LDI)                         | 20 |

| 2.4.2 Bilinear Discrete Integrator (BDI)                         | 21 |

| 2.4.3 Composite Discrete Integrator (CDI)                        | 22 |

| Chapter 3 Implementation of Low voltage SC integrator            | 25 |

| 3.1 Introduction                                                 | 25 |

| 3.2 The operational-amplifier (Opamp)                            | 25 |

| 3.2.1 Two-stage operational-amplifier                            | 26 |

| 3.3 MOSFET Switches                                              | 34 |

| 3.4 Clock Signal Generator                                       | 36 |

| 3.5 Sample and Hold (S/H) circuit                                | 37 |

| 3.6 SC Integrator                                                | 38 |

| 3.6.1 Parameters of SC integrator                                | 40 |

| 3.6.1.1 Supply Voltage                                           | 40 |

| 3.6.1.2 Power Consumption                                        | 40 |

| 3.6.1.4 Power Supply Rejection Ratio (PSRR)                      | 42 |

| 3.6.1.1 Noise Analysis                                           | 43 |

| Flicker Noise                                                    | 43 |

| Chapter 4 Implementation of CPE using SC biquads                 | 46 |

| 4.1 Approximation of CPE using CFE                               | 46 |

| 4.2 Realization of CPE using BDI-based SC biquad                 | 51 |

| 4.3 Realization of CPE using CDI-based SC biquad                 | 66 |

| Chapter 5 Simulating SC circuit                                  | 78 |

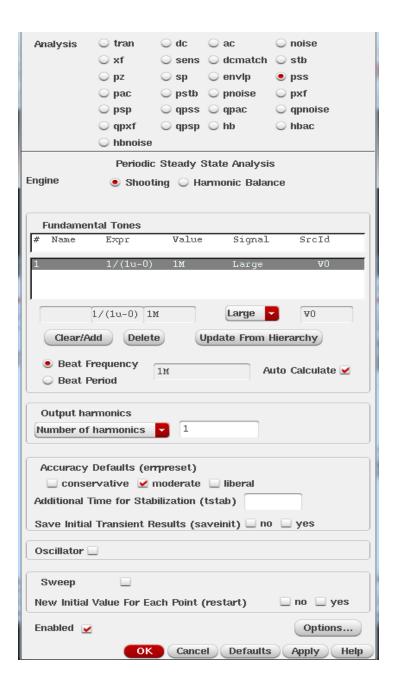

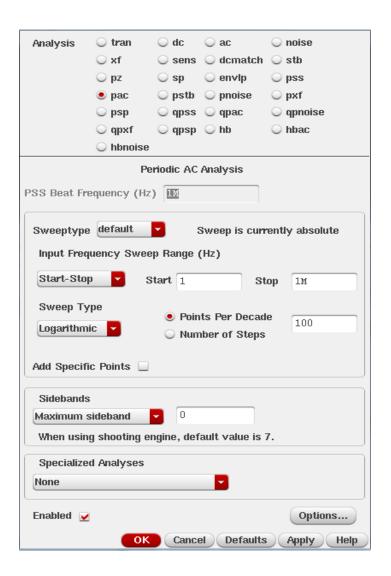

| 5 1 Simulating SC Circuits using Cadence                         | 78 |

| 5.2 Monte Carlo Analysis                                                       | 79 |

|--------------------------------------------------------------------------------|----|

| 5.3 Optimization of the Normalized Approximation using Steepest Descent Method |    |

|                                                                                | 82 |

| Chapter 6 Conclusions                                                          | 86 |

| 6.1 Summary of thesis                                                          | 86 |

| 6.2 Performance Comparison Table                                               | 88 |

| 6.3 Future work                                                                | 89 |

| Appendix                                                                       | 91 |

| References                                                                     | 96 |

|                                                                                |    |

# **List of Tables**

| Table 1 Comparison of errors for various integration schemes                                                       | 24 |

|--------------------------------------------------------------------------------------------------------------------|----|

| Table 2 Comparison of various topologies of operational amplifiers                                                 | 26 |

| Table 3 Parameters for the designed Operational amplifier                                                          | 31 |

| Table 4 Performance Parameters of designed Operational amplifier                                                   | 34 |

| Table 5 Performance Parameters of SC integrator                                                                    | 45 |

| Table 6 Approximated CPE component values                                                                          | 48 |

| Table 7 Parameters of BDI based SC bi-quad circuit for 2nd order approximation of CP                               |    |

| Table 8 Parameters of cascaded BDI based SC bi-quad circuit for 4th order approximation of CPE.                    | 67 |

| Table 9 Parameters of CDI based SC bi-quad circuit for 2nd order approximation of CP                               |    |

| Table 10 Performance parameters of CPE through BDI and CDI based S.C bi-quads                                      | 77 |

| Table 11 Monte Carlo Analysis Values for 4 <sup>th</sup> order approximation of CPE                                | 82 |

| Table 12 The initial and optimized parameters of the 2 <sup>nd</sup> order approximated S-domain transfer function |    |

| Table 13 The initial and optimized parameters of the 4 <sup>th</sup> order approximated S-domain transfer function | 84 |

| Table 14 A detailed performance comparison of the novel CPE design through SC circuits with other existing designs | 88 |

# **LIST OF FIGURES**

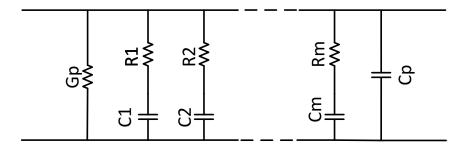

| Figure 1 Theoretical representation of single dispersion Cole-Cole impedance model  | 4    |

|-------------------------------------------------------------------------------------|------|

| Figure 2 Theoretical representation of double dispersion Cole-Cole impedance model. | 6    |

| Figure 3 Impedance loci to extract parameters of single dispersion Cole-Cole model  | 7    |

| Figure 4 Integrator setup for extracting Cole-Cole impedance model parameters       | 9    |

| Figure 5.Basic RC network for realizing a CPE                                       | . 13 |

| Figure 6.Modified RC network for realizing a CPE                                    | . 13 |

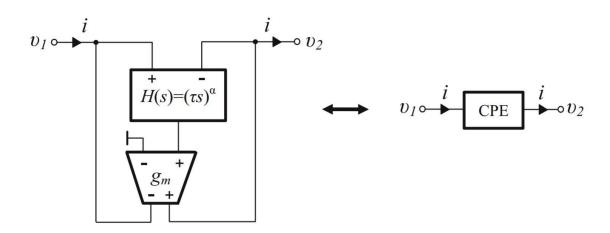

| Figure 7. Realizing a CPE using OTA                                                 | . 15 |

| Figure 8. Functional block diagram for CPE emulation                                | . 16 |

| Figure 9 CPE emulation using CFOAs                                                  | . 18 |

| Figure 10 LDI                                                                       | . 20 |

| Figure 11 BDI                                                                       | . 22 |

| Figure 12 Magnitude errors for LDI, BDI and CDI.                                    | . 23 |

| Figure 13 Two-stage Operational amplifier                                           | . 27 |

| Figure 14 Small signal model of two-stage operational amplifier                     | . 27 |

| Figure 15 NMOS Configuration to Obtain Threshold Voltage                            | . 32 |

| Figure 16 I <sub>ds</sub> vs V <sub>th</sub> Plot for NMOS Transistor               | . 32 |

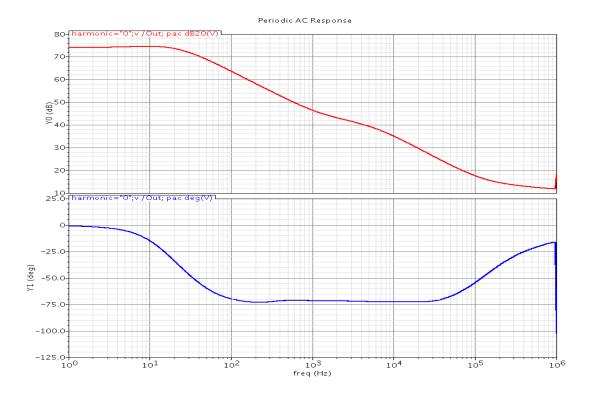

| Figure 17 Frequency response of Operational amplifier                               | . 33 |

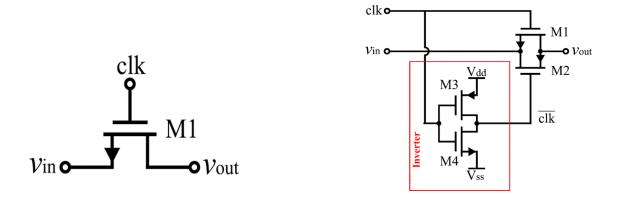

| Figure 18 NMOS Transistor as switch and transmision gate as switch                  | . 35 |

| Figure 19 Transmission gate as switch in cadence                                    | . 36 |

| Figure 20 Sample clock signal generator                                             | . 37 |

| Figure 21 Non-overlapping clock signal                                              | . 37 |

| Figure 22 Sample and Hold circuit                                                   | 38   |

| Figure 23 SC integrator                                                                                           | 38 |

|-------------------------------------------------------------------------------------------------------------------|----|

| Figure 24 Output sine wave of SC integrator                                                                       | 39 |

| Figure 25 Frequency response of SC integrator                                                                     | 39 |

| Figure 26 Static Current Measurement from a Supply Voltage of 0.7 V                                               | 40 |

| Figure 27 Slew rate of SC integrator                                                                              | 41 |

| Figure 28 Frequency verses PSRR Plot of SC integrator                                                             | 42 |

| Figure 29 Input referred Noise of SC integrator                                                                   | 44 |

| Figure 30 RC ladder structure to realize Nth order integer approximation of CPE with pseudo-capacitance $C\alpha$ |    |

| Figure 31 Frequency response for 2nd order approximation for $\alpha = 0.2, 0.5, 0.8$                             | 49 |

| Figure 32 Frequency response for 4th order approximation for $\alpha = 0.2, 0.5, 0.8$                             | 51 |

| Figure 33 General SC biquad.                                                                                      | 53 |

| Figure 34 Forward-Euler and Backward-Euler discrete integrators                                                   | 54 |

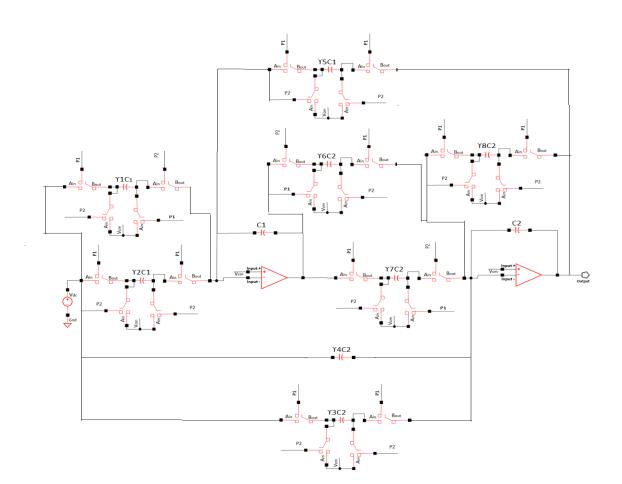

| Figure 35 BDI-based SC biquad circuit                                                                             | 55 |

| Figure 36 second order approximation of CPE using BDI-based SC biquad circuit                                     | 57 |

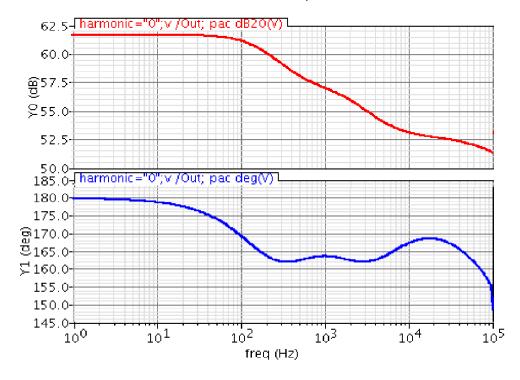

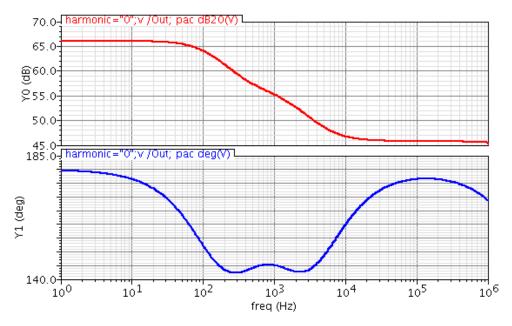

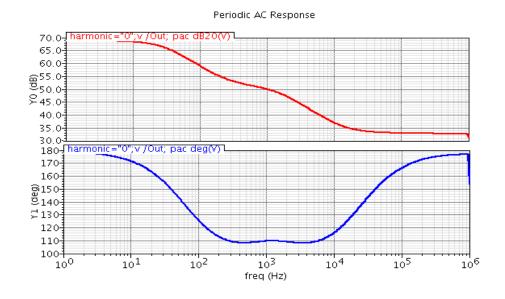

| Figure 37 Magnitude and phase response of CPE for $\alpha$ = 0.2                                                  | 58 |

| Figure 38 Magnitude and phase response of CPE for $\alpha$ = 0.5                                                  | 59 |

| Figure 39 Magnitude and phase response of CPE for $\alpha$ = 0.8                                                  | 59 |

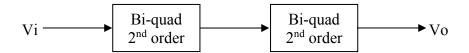

| Figure 40 Fourth order approximation using cascading two biquad SC circuit                                        | 62 |

| Figure 41 Fourth order approximation of CPE using cascading SC biquad                                             | 63 |

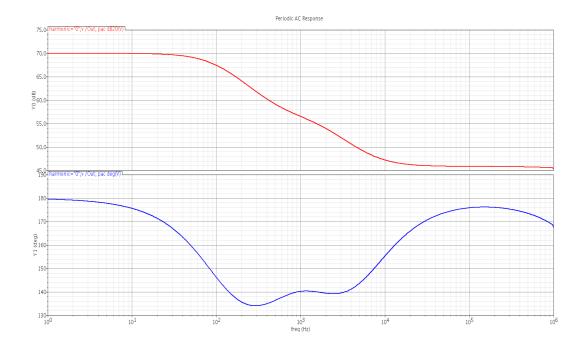

| Figure 42 Magnitude and phase response of CPE for $\alpha$ = 0.2                                                  | 65 |

| Figure 43 Magnitude and phase response of CPE for $\alpha$ = 0.5                                                  | 65 |

| Figure 44 Magnitude and phase response of CPE for $\alpha$ = 0.8                                                  | 66 |

| Figure 45 Stray insensitive CDI based SC integrator                                                               | 67 |

| Figure 46 CDI based SC biquad                                                                                     | 68 |

| Figure 47 CDI based SC configuration                                                                              | 69 |

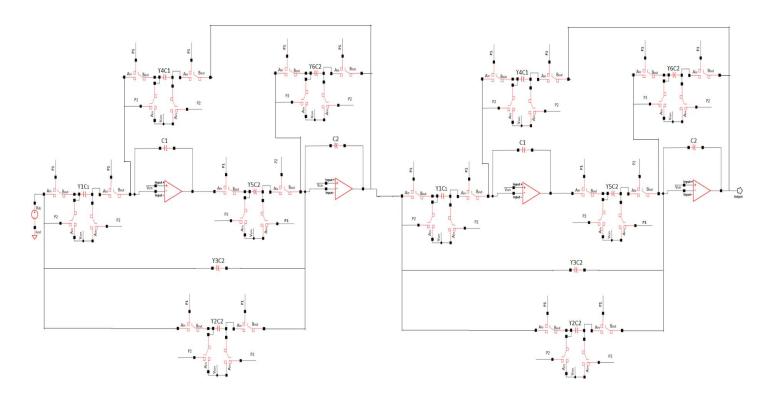

| Figure 48 Second order approximation of CPE using CDI-based SC biquad circuit                                                        | 72 |

|--------------------------------------------------------------------------------------------------------------------------------------|----|

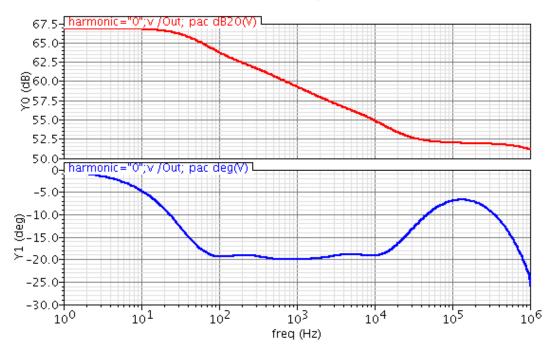

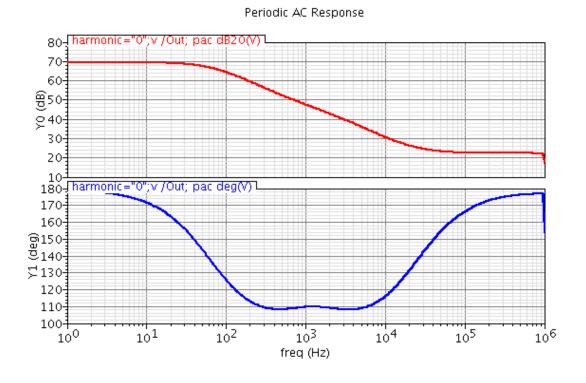

| Figure 49 Magnitude and phase response of CPE for $\alpha$ = 0.5                                                                     | 75 |

| Figure 50 Magnitude and phase response of CPE for $\alpha$ = 0.8                                                                     | 75 |

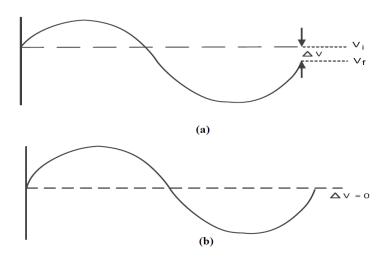

| Figure 51 Non-periodic and periodic signal                                                                                           | 78 |

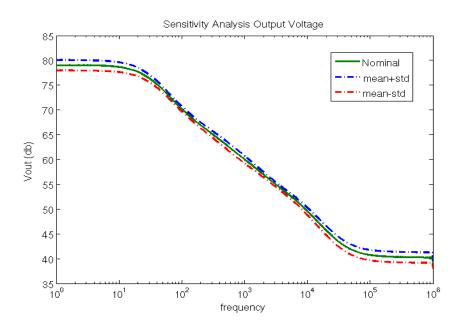

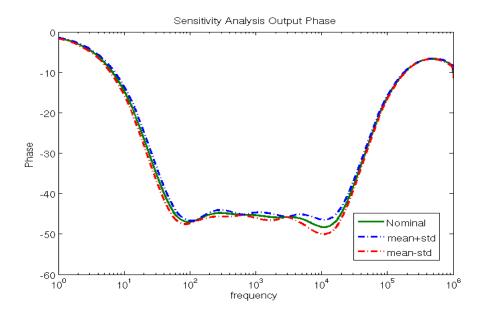

| Figure 52 Sensitivity Analysis for CPE magnitude implemented through 4 <sup>th</sup> order approximated cascaded SC biquad for α=0.5 | 81 |

| Figure 53 Sensitivity Analysis for CPE phase implemented through 4 <sup>th</sup> order approximated cascaded SC biquad for α=0.5     | 81 |

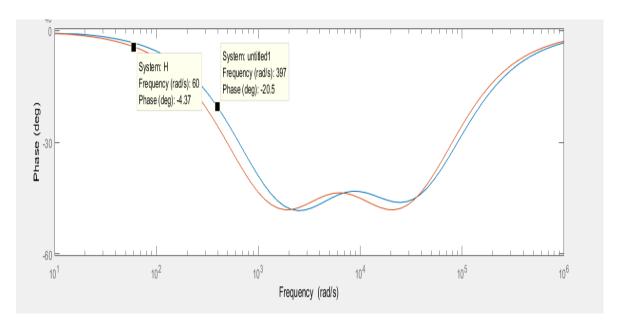

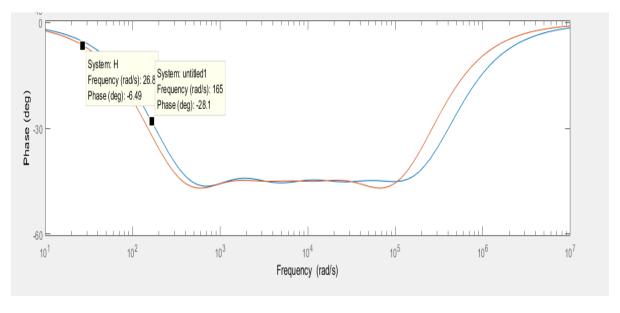

| Figure 54 The phase responses of the original and optimized 2 <sup>nd</sup> order approximation                                      |    |

| Figure 55 The phase responses of the original and optimized 4 <sup>th</sup> order approximation                                      | 85 |

#### **ABSTRACT**

This work provides, switched-capacitor (SC) realizations of the constant phase element (CPE) using the TSMC 65 nm CMOS technology that could potentially be used in circuits for measuring fractional impedances. Two versions of the SC realizations are developed; using the bilinear discrete integrator (BDI) and composite discrete integrator (CDI)-based SC biquads. The realized CPE exhibits a constant phase in the frequency range 200 Hz to 3 KHz in its 2<sup>nd</sup> order approximation, 80 Hz to 10 KHz in its 4<sup>th</sup> order approximation using BDI and over the frequency range 200Hz to 3 KHz for 2<sup>nd</sup> order approximation when realized using CDI. The total power consumption of the designed 2<sup>nd</sup>, 4<sup>th</sup> order approximated CPE using BDI are 5.95mW, 10.11mW and for 2<sup>nd</sup> order approximation of CPE using CDI is 7.12mW, which are very low in discrete circuit design. The normalized transfer functions obtained through continued fraction expansion (CFE) is further optimized through steepest descent technique for minimum phase errors. These SC realizations also have exhibited high linearity, high dynamic range and are also much tunable compared with traditional RC ladder realizations. These SC realizations are simulated with low supply voltage of 0.7 V, the proposed realizations can be implemented for bio-medical applications that demand low voltage inputs and low power consumption (LVLP).

#### LIST OF ABBREVIATIONS USED

AC Alternating Current

BD Bulk Driven

BDI Bilinear Discrete Integrator

BEDI Backward Euler Discrete Integrator

Cc Compensating Capacitor

CDI Composite Discrete Integrator

CFE Continued Fraction Expansion

CFE Continued Fraction Expansion

CFOA Current Feedback Operational Amplifier

CMOS Complementary-Metal-Oxide-Semiconductor

CPE Constant Phase Element

DC Direct Current

FC Fractional Capacitor

FD Fractional Derivative

FEDI Forward Euler Discrete Integrator

FI Fractional Inductor

FLF Follow the Loop Feedback

FO Fractional order

GBP Gain Bandwidth Product

GIC Generalized Impedance Converter

GRG Generalized Reduced Gradient

ICMR Input Common Mode Range

IFLF Inverse Follow the Loop Feedback

LDI Loss less Discrete Integrator

LVLP Low Voltage Low Power

MLF Multiple Loop Feedback

MOSFET Metal-Oxide-Semiconductor Field Effect Transistor

NMOS N-type Metal-Oxide-Semiconductor

OPAMP Operational Amplifier

OTA Operational Trans-Conductance Amplifier

PAC Periodic Alternating Current

PM Phase Margin

PMOS P-type Metal-Oxide-Semiconductor

PSRR Power Supply Rejection Ratio

PSS Periodic Steady State

RC Resistor and Capacitor

S/H Sample and Hold

SC Switched Capacitor

SR Slew Rate

V/I Voltage to Current

#### **ACKNOWLEDGEMENTS**

Firstly, I would like to express my very great appreciation to my supervisor **Dr. Ezz. El-Masry**, for his excellent support, patience, caring and the motivation that helped me to complete this research. I couldn't imagine completing this thesis without his esteemed guidance and valuable suggestions.

I would like to thank **Dr. Jason Gu** and **Dr. William Philips** of my supervisory committee.

I am very much thankful to the technical support team **Mark Le Blanc**, **Tyler Seize** and **Jordan Wright** for their continuous support in software related issues. My sincere thanks to graduate secretary **Nicole Smith** for her extensive support throughout my studies at Dalhousie University which was remarkable.

I would take this opportunity to thank my parents Kalvacharla Narsimha Chary, Kalvacharla Parijatham for their love and support in all consequences. I must express my very gratitude to my Brother-In-Law Dr. Prashanth Maroju, my loving sister Indu Maroju for their continuous love and support, I would like to thank my family, friends for their encouragement and best wishes.

#### CHAPTER 1 INTRODUCTION

#### 1.1 Motivation

Several physical characteristics and properties of many biological materials such as tissues and cancer cells can be estimated through the measurement of their impedances. There are two common methods to analyze bio-impedances, direct method and indirect method. The direct method is to simply compare changes in impedance at certain frequencies, while indirect method compares changes in the circuit parameters that represent wide-band frequency measurements using an equivalent electrical circuit. Several studies have proved that fractional order (FO) models can characterize real-world physical systems more effectively using differential operators of an arbitrary order. Therefore, components with FO impedances have been widely used through indirect methods [1]. A fractional model called Cole-Cole model is the most successful model in describing the measured impedance of a biological material. Although simple integrator based circuit designs exist to realize this Cole-Cole model, these circuits rely on the design of a constant phase element (CPE) of FO. All the existing realizations of the CPE use Passive elements such as RC ladders and this research thereby aims towards providing alternative realization using tunable and scalable active elements that can be fabricated in integrated circuits form.

#### 1.2 Fractional Order Systems and Circuits

Fractional calculus, is a branch of mathematics that has been introduced more than 200 years ago. It considers differentiations and integrations at non-integer orders, which has become a popular tool for modeling and characterizing complex behaviors of physical systems during the past decades and has found many applications in different fields of science and engineering. A fractional derivative (FD) of order  $\alpha$  is given by Riemann-Liouville as [2]

$${}_{a}D_{t}^{\alpha}f(t) = \frac{d^{n}}{dt^{n}} \left[ \frac{1}{\Gamma(n-\alpha)} \int_{a}^{t} \frac{f(\tau)}{(t-\tau)^{\alpha+1-n}} d\tau \right]$$

(1.1)

where  $\Gamma(.)$  is the gamma function, a denotes the lower terminal and  $n-1 \le a \le n$ .

Although, this definition plays an important role in the development of the theory of fractional derivatives and integrals as well as their applications in pure mathematics, but the demands of modern technology require definitions of FD which allows for the utilization of physically interpretable initial conditions. Therefore, another definition of FD is given by the Caputo fractional derivative as [2]

$$_{a}D_{t}^{\alpha}f(t) = \frac{1}{\Gamma(n-\alpha)} \int_{a}^{t} \frac{f^{n}(\tau)}{(t-\tau)^{\alpha+1-n}} d\tau$$

(1.2)

The Caputo definition benefits from the initial conditions in a similar form as the integer order differential equations.

Although, fractional calculus and mathematical model of FO systems have been presented for more than 200 years, it was only treated as an interesting abstract mathematical concept [2]. Therefore, the FO dynamical systems were limited in the theory and margin practice of control systems [4]. The ambition to implement a dynamical system of FO whose mathematical model has been in use for many years provided the motivation for an electronic realization of FO dynamical systems. Hence, the concepts of fractional calculus and FO systems have been slowly migrating into circuit theory and design [2].

#### 1.2.1 Fractional order systems

Applying the Laplace transform to the Caputo definition of fractional derivatives (FD) with a = 0 gives

$$\mathcal{L}\left\{a=0D_{t}^{\alpha}f(t)\right\} = s^{\alpha}F(s) - \sum_{k=0}^{n-1} s^{\alpha-k-1}f^{(k)}(0)$$

(1.3)

Although, the Laplace transform has been traditionally applied to integer order systems, but it has been proved to be mathematically valid for non-integer order of  $s^{\alpha}$  where  $n-1 < \alpha < n$  [5]. This can effectively represent a fractional order (FO) system. Hence, general

fractional order elements with impedances proportional to  $s^{\alpha}$  can be defined. The traditional integer order circuit elements such as resistors, capacitors and inductors are special cases of the general fractional order elements where the order  $\alpha$  is equal to 0, -1, and 1, respectively.

Constant Phase Element (CPE) is another special case of the general fractional order elements which has the impedance of  $Z_{CPE} = 1/s^{\alpha}C$ , where C is the capacitance and  $0 < \alpha < 1$  denotes its order. These elements are also called fractional order capacitors as the value of their order is between the corresponding value of the traditional circuit components of a resistor and capacitor.

FO systems can be realized using fractional order elements and have many applications in different fields including control systems [2, 4], electronic circuits [7-12], electromagnetic [6], stability analysis [13], mechanics [6] and bioengineering [14] to name a few.

#### 1.2.2 Fractional order circuits

Analog and discrete electronic circuits realized using FO elements such as constant phase element (CPE) can simplify the solution of many practical problems. Common application of the analog models mainly covers the FO dynamical systems [4, 6], FO controllers [7,16], FO filters [16-20] as well as FO oscillators [6,20]. FO element as the basic element of analog circuit is theoretically realized based on the combination of RC components in the form of infinite cross RC ladder network or domino ladder, where the latter demonstrates more flexibility in providing different values of fractional exponent [14].

Utilizing FO elements to realize FO systems is steadily increasing in various fields of electrical engineering. Constant phase element (CPE) have been broadly used in the field of bio-impedance to measure the passive electrical properties of biological materials. These measurements provide useful information about the electrochemical processes in tissues in order to characterize the tissue or monitor for physiological changes [21-26]. Several fractional impedance models currently exist in literature. Cole-Cole impedance model [27-30], fractional plant model [28], electrode tissue interface model [33], fractional respiratory model [7,33] and fractional supercapacitor model [33] are among the most famous ones.

These fractional impedance models can be used to model biological tissues, electrode tissue interfaces, respiratory impedance and supercapacitors for several different applications.

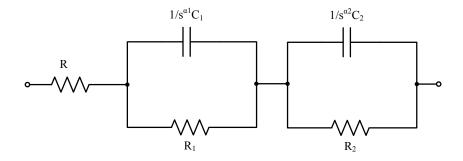

#### 1.3 The Cole-Cole Impedance Model

While several fractional models to characterize biological tissues and biochemical materials have been addressed in literature, Cole-Cole impedance model, introduced by Kenneth Cole [29], is the most famous one. The equivalent circuit of this model is given in Figure 1. This model consists of three hypothetical circuit components including 1) resistor  $R_I$ , 2) high-frequency resistor  $R_{\infty}$ , and 3) a CPE  $C_I$ . Knowing that CPE has the equivalent impedance of  $Z_{CPE} = I/s^{\alpha}C$ , the impedance of Cole-Cole impedance model is given by

$$Z(s) = R_{\infty} + \frac{R_1}{1 + s^{\alpha_1} R_1 C_1}$$

(1.4)

As  $s^{\alpha} = (j\omega)^{\alpha}$  can be rephrased as  $\omega^{\alpha}[\cos(\alpha\pi/2) + j\sin(\alpha\pi/2)]$ , the above equation can be simplified as Z(s) = Z' + j Z''.

Figure 1 Theoretical representation of single dispersion Cole-Cole impedance model [29]

The resistances in Cole-Cole impedance model physiologically represent various intracellular, extracellular and cellular membrane resistances within the tissue. The membrane capacitances of different tissues can be characterized by a capacitance. The parameter  $\alpha$  can be also considered as a distribution of relaxation times due to heterogeneity

of sizes and shapes of different cells. This may denote a measure of deviation from an ideal capacitor in the equivalent circuit.

Simplicity, being a good fit with measured data as well as demonstrating the impedance behavior as a function of frequency are among features, which have made the Cole-Cole impedance model quite popular in efficiently characterizing experimentally collected bio-impedance data. However, this model does not provide an explanation of the underlying mechanisms.

The application of Cole-Cole impedance model in several fields of biology and biomedicine has been broadly investigated. Several studies explored various applications in biomedicine for single dispersion representation of this model (Figure 1) and its parameters [22-33]. Furthermore, broad research on the relation of parameters of this model to cancer cells have resulted in many applications [22-33].

An expanded version of Cole-Cole impedance model is depicted in Figure 2. This model consists of a single dispersion Cole-Cole impedance model in series with an additional parallel combination of a resistor with a CPE. The equivalent impedance of this double dispersion representation of Cole model can be obtained by

$$Z(s) = R_{\infty} + \frac{R_1}{1 + s^{\alpha_1} R_1 C_1} + \frac{R_2}{1 + s^{\alpha_2} R_2 C_2}$$

(1.5)

The double dispersion representation of Cole model is mostly used to precisely characterize the impedance either within a larger frequency range or more complex materials. Monitoring necrosis of human tumor [29] and investigating age-related changes of human dentine [29-33] are examples of its applications.

Figure 2 Theoretical representation of double dispersion Cole-Cole impedance model [29]

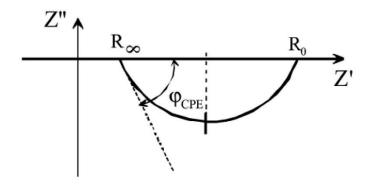

A tissue or biomaterial can be characterized by the fractional impedance parameters which can describe the impedance behavior as a function of frequency. There are either four  $(R_{\infty},$  $R_1$ ,  $C_1$ ,  $\alpha_1$ ) or seven  $(R_{\infty}, R_1, R_2, C_1, C_2, \alpha_1, \alpha_2)$  parameters to be determined in single and double dispersion Cole-Cole impedance models; respectively. These parameters can be extracted graphically from an impedance plot, which relates imaginary part of impedance, Z", to the real part of impedance, Z'. Figure 3 demonstrates an impedance plot which can be used to extract parameters of single dispersion Cole model. The theoretical low frequency resistance,  $R_0$ , and high frequency resistance,  $R_{\infty}$ , can be measured through the circular arc.  $R_I$  can be simply calculated from  $R_I = R_0 - R_\infty$ . The measured angle, as depicted in Figure 3, denotes  $\phi_{CPE}$  through which the order,  $\alpha_I$ , can be calculated from  $\phi_{CPE} = \alpha_I \pi/2$ . The capacitor,  $C_l$ , can be finally obtained using the previously calculated parameters considering the fact that the dispersion time constant,  $\tau$ , is given as  $\tau = (R_I C_I)^{1/\alpha}$  and the frequency at which |Z''| has its maximum is equal to  $1/\tau$ . However, parameters are now mostly estimated using non-linear least squares routines which fits the experimental data to the desired model using powerful numerical fitting software such as LEVM/ LEVMW and MATLAB.

To obtain the impedance plot (Figure 3), the impedance of the desired tissue is required to be measured using an impedance analyzer. A circular arc can be obtained by applying least square regression to the acquired data points. A similar impedance plot with two circular arcs can be used to extract parameters of double dispersion Cole model. It has been clear so far that acquiring Z' and Z'' requires expensive impedance analyzers and post processing

of the data to draw the circular arc. Although using data acquisition cards and custom software modules to implement the required signal processing can be considered as cheap alternatives [33], it is desired to extract parameters without requiring measurement of impedance.

Figure 3 Impedance loci to extract parameters of single dispersion Cole-Cole model [29]

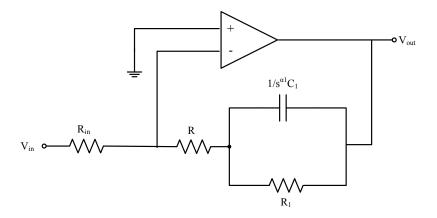

#### 1.3.1 Integrator based Setup of Cole-Cole Impedance Model

A simple integrator setup of Cole impedance model using an inverting op amp integrator is demonstrated in Figure 4 [34]. As the Cole impedance model is in the feedback path, the transfer function of the given filter can be obtained by

$$T(s) = \frac{V_{out}}{V_{in}} = -\frac{G_1 + G_2(\tau s)^{\alpha}}{1 + (\tau s)^{\alpha}}$$

(1.6)

where  $G_1 = (R_1 + R_{\infty})/R_{in}$ ,  $G_2 = R_{\infty}/R_{in}$  and  $s = j\omega$ .

It should be noted that the DC gain of the transfer function can be measured at  $\omega=0$  which yields  $|T(j\omega)| = G_1$  and hence  $R_{in} = (R_1 + R_{\infty}) = R_0$ . The high frequency gain can be measured in a similar way when  $\omega=\infty$ . This results in  $|T(j\omega)| = G_2$  and  $R_{in} = R_{\infty}$ .

The -3dB point where  $|T(j\omega_{3dB})| = G_1/\sqrt{2}$  is given by

$$\omega_{-3dB} = \frac{1}{\tau} \left[ a \left( \sqrt{\frac{(b + \cos(\alpha \pi))}{2}} - \cos\left(\frac{\alpha \pi}{2}\right) \right) \right]^{1/\alpha} = \frac{f_1(\alpha)}{\tau}$$

(1.7)

where

$$a = G_1(G_1 - 2G_2) / (G_1^2 - 2G_2^2)$$

and  $b = G_1(3G_1 - 4G_2) / (G_1 - 2G_2)^2$ .

The frequency at which the phase angle  $\angle T(j\omega)$  obtains its minimum value and the magnitude,  $|T(j\omega_{\phi min})|$  is equal to  $\sqrt{(G_1G_2)}$  is also given by

$$\omega_{\emptyset min} = \frac{1}{\tau} \left( \sqrt{\frac{G_1}{G_2}} \right)^{1/\alpha} = \frac{f_2(\alpha)}{\tau}$$

(1.8)

Hence, it is possible to find the  $\omega_{\phi min}$  from the magnitude response without even plotting the phase of the transfer function. It is also notable that the ratio of  $\omega_{3dB}/\omega_{\phi min} = f_1(\alpha)/f_2(\alpha)$  is only a function of  $\alpha$  and independent of  $\tau$ . Therefore, assuming  $\omega_{3dB}/\omega_{\phi min} = k$ ,  $\alpha$  can be found by solving the following equation:

$$\left(\frac{\sqrt{G_1G_2(G_1 - 2G_2)}}{(G_1^2 - 2G_2^2)}\right) \times \left(\sqrt{\frac{b + \cos(\alpha\pi)}{2} - \cos\left(\frac{\alpha\pi}{2}\right)}\right) = k^{\alpha}$$

(1.9)

After finding  $\alpha$ , the value of  $\tau$  can be found from equation 1-8. This integrator setup can extract all parameters of Cole-Cole impedance model without any need for an impedance analyzer and by plotting only the magnitude response. However, it calls for a high computational cost due to numerically solving equation 1-9 to find  $\alpha$ .

Figure 4 Integrator setup for extracting Cole-Cole impedance model parameters [34]

#### 1.4 Thesis Contribution

#### 1.4.1 Implementation of CPE using low voltage SC-BDI

Realization of the proposed CPE using the bilinear discrete integrator (BDI) based SC circuit operates at a low supply voltage of 0.7 V and thus resulting in lower power consumption with more linearity and dynamic range compared to the existing designs.

#### 1.4.2 Implementation of CPE using low voltage SC-CDI

The proposed CPE design using CDI based SC circuit operates at lower supply voltage of 0.7 V and lower power consumption with more linearity, dynamic range and showed reduction several errors compared to the existing designs.

#### 1.4.3 Minimizing the CPE errors using optimizing technique

The approximated S-domain transfer functions obtained through CFE with one of the traditional optimization technique, steepest descent method, is optimized for minimum total error in the frequency range of 1 Hz to 10<sup>7</sup> Hz by comparing it to an ideal response.

#### 1.5 Thesis Organization

This thesis is organized as follows:

Chapter 2 Briefly describes FO systems, circuits and their importance in various applications. Detail operation of different integration schemes for implementing SC circuits. This section also describes the existing realizations of constant phase element that could be used in the design of FO circuits.

Chapter 3 Presents the detail operation and implementation of circuit elements used for SC realization such as op amp, switches, clock generator and sample and hold circuit. The simulation results obtained from Cadence TSMC 65nm CMOS technology and their performance parameters are tabulated.

Chapter 4 Presents the second and fourth-order approximated CPE designs using BDI-based SC circuit through cascade topology. Provides the detail operation and implementation of second-order approximated CPE design using CDI-based SC circuit along with their simulation results including performance comparison table.

Chapter 5 Provides the details of various simulation analyses required for SC circuits. The sensitivity results for different techniques presented in chapter 4 using Monte Carlo analysis are also presented. Discusses, the optimization technique used to minimize errors of the obtained s-domain approximation of CPE presented in chapter 4.

Chapter 6 Presents conclusions about the realized CPE using BDI and CDI-based SC circuits in this thesis and comparison with other existing CPE realizations. Few suggestions for future work are also discussed.

#### **CHAPTER 2 LITERATURE REVIEW**

#### 2.1 Constant Phase Element (CPE)

There has been growing research interest in the development of FO circuits mainly due to the interdisciplinary nature of fractional calculus which make them a powerful tool for biological [1], biomedicine [21] and electrical engineering applications [6,40,41]. FO capacitors or constant phase element (CPE) is one of the most important element in realizing FO circuits.

Constant phase element (CPE) have been broadly used in the field of bio-impedance to measure the passive electrical properties of biological materials. These measurements provide useful information about the electrochemical processes in tissues in order to characterize the tissue or monitor for physiological changes [24,25].

CPE can be defined as a lossy capacitor with dispersion coefficient of less than unity which results in a current-voltage phase angle less than  $\pi/2$ . Current, voltage and charge in this FO element are related by

$$i(t) = \frac{dq}{dt} = \hat{C}\frac{d^{\alpha}V(t)}{dt^{\alpha}}$$

(2.1)

where  $\widehat{C}$  denotes the pseudo-capacitance with unit Farad/Sec <sup>(1- $\alpha$ )</sup> and  $\alpha$  is the dispersion coefficient or order of the CPE (0 <  $\alpha$  < 1) [34]. The impedance of a CPE is then given as  $Z(s) = 1/\widehat{C}$   $s^{\alpha}$  and the value of the frequency dependent capacitance (in Farad) of FO element is calculated as  $C = \widehat{C} / \omega^{(l-\alpha)}$ . The latter equation indicates that the capacitance of a CPE depends on both frequency and order [34-39].

CPEs can be realized by cross RC ladder network to obtain different values of order  $\alpha$ . However, the circuit suffers from being bulky and impractical. Domino ladder of different structures is another alternative solution which offers more flexibility in designing different order values comparing to an RC ladder network. It is worth mentioning that a Fractional Inductor (FI) can also be realized based on CPEs and the utilization of a Generalized

Impedance Converter (GCI). A simple FO band-pass filters can be achieved through connecting a resistance, an FC and FI in series [39], this is a more generalized approach in realizing a FO band-pass filter. Much complicated band-pass filters for specific applications can also be developed through different combinations of these elements.

#### 2.2 Existing Realizations of Constant Phase Element

There have been many attempts for realizing the CPEs as standalone two-terminal devices. However, there are no commercially available devices due to several obstacles such as stability due to component variations and unstable approximations during realization [39, 41]. Therefore, several techniques for realizing CPEs through proper integer order approximation have been developed.

#### 2.2.1 CPE realization using passive elements

Existing techniques for emulating a CPE is mainly based on approximation of its behavior through passive RC networks of integer order. Previous works mostly expanded  $s^{\alpha}$  into infinite series to lead to a chain fraction which will then be converted into an RC ladder [33, 36-39]. This procedure, however, is usually difficult and simple models with correct phase angles more than  $-45^{\circ}$  cannot be easily achieved. Another model using low number of standard resistors and capacitors have been proposed in [39] with which any phase angle in the range between  $-\pi/2^{\circ}$  and  $0^{\circ}$  can be obtained. This model, shown in Figure 5, composed of parallel connections of m series RC branches where

$$R_{k+1} = aR_k$$

,  $0 < a < 1$

$C_{k+1} = bC_k$  ,  $0 < b < 1$

$k = 1, ..., m - 1$  (2.2)

The value of parameters a and b directly determine the phase angle  $\phi_{av}$  in the following equation:

$$\emptyset_{av} = \frac{\pi}{2} \frac{\log a}{\log a + \log b} \tag{2.3}$$

Figure 5 Basic RC network for realizing a CPE [39]

The input impedance of the network is given by

$$Z(j\omega) = \sum_{k=1}^{m} \frac{1 + j\omega(ab)^{k-1} R_1 C_1}{j\omega b^{k-1} C_1}$$

(2.4)

Although this model can demonstrate any phase angle between  $-90^{\circ}$  and zero, this result cannot be achieved by m < 20. The model has been later modified by adding two parallel branches of a resistor and a capacitor:

$$G_p = \frac{1}{R_1} \frac{a}{1 - a} \tag{2.5}$$

$$C_p = \frac{C_1 b^m}{1 - b} \tag{2.6}$$

Satisfactory results can be obtained using the modified model given in Figure 6 with m having value as small as 4 [39]. Several voltage-mode filter topologies employed similar concept models to approximate a CPE [33,37, 39].

Figure 6 Modified RC network for realizing a CPE [39]

These CPE emulation techniques lack flexibility and tunability as all the values of the passive components of RC ladder should be changed in case of any alteration of characteristics of the realized CPE.

# 2.2.2 CPE realizations using operational transconductance amplifiers

Active realization of a CPE based on operational transconductance amplifiers (OTAs) and grounded capacitors have been recently proposed by [35]. This technique offered independent tuning of the magnitude, order and bandwidth of the emulated CPE over a certain frequency range through changing the bias currents of the OTA units in contrast to its passive counterparts.

The starting point of the design is to characterize the CPE using a low-pass fractional order filter with the following transfer function:

$$H(s) = -\frac{R_{ex2}}{R_{ex1}} \frac{\omega_p^{\alpha}}{s^{\alpha} + \omega_p^{\alpha}}$$

(2.7)

The order of the CPE can be determined through a phase measurement at the half-power frequency. Hence, the pseudo-capacitance can be calculated using

$$\omega_p = (\frac{1}{R_{ex2}\hat{c}})^{1/\alpha} \tag{2.8}$$

$$\omega_h = \omega_p \cdot \left[ \sqrt{1 + \cos^2\left(\frac{\alpha\pi}{2}\right)} - \cos\left(\frac{\alpha\pi}{2}\right) \right]^{1/\alpha}$$

(2.9)

A functional block diagram of the topology of CPE emulation using OTA is shown in Figure 7. This topology is constructed through a fractional order differentiator with unity-gain frequency and a voltage-to-current converter implemented by an OTA with small-signal transconductance,  $g_m$ . The equivalent impedance is given by:

$$Z_{eq} = \frac{v_1 - v_2}{i} = \frac{1}{g_m(\tau s)^{\alpha}}$$

(2.10)

Comparing the equivalent impedance with the impedance of a CPE, the pseudo-capacitance can be calculated as:

$$\hat{C} = g_m \tau^\alpha \tag{2.11}$$

The capacitance can be also obtained by de-normalizing the calculated pseudo-capacitance:

$$C = \frac{g_m}{\omega_u^{\alpha} \cdot \omega^{1-\alpha}} \tag{2.12}$$

Figure 7 Functional block diagram for CPE using OTA's [35]

Since the FO differentiator should be approximated by an integer order topology, the unity-gain or time constant of the differentiator is required to be chosen such that the differentiator demonstrates phase and magnitude responses with acceptable errors within the operating frequency range. The designed CPE using OTAs is shown in figure 8.

Figure 8 CPE emulation using OTAs [35]

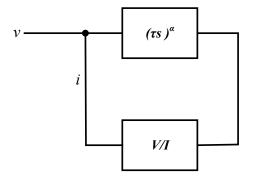

# 2.2.3 CPE realizations using current feedback operational amplifier

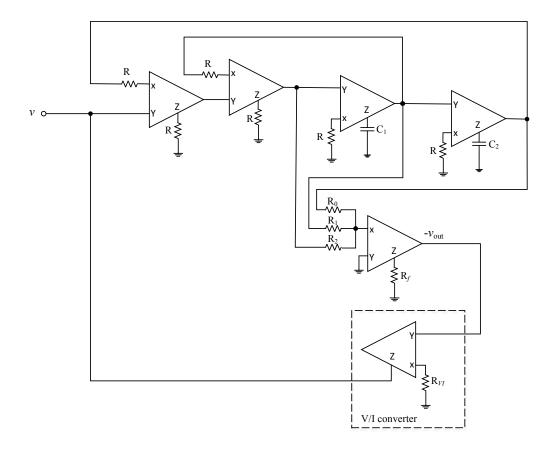

CPE can be realized using a FO differentiator and/or integrator configurations and a V/I converter. The FO differentiator and integrator can be realized using active elements such as current feedback op-amps (CFOAs), which benefit from flexible and versatile design. A key advantage of emulating a CPE using CFOA, as proposed in [36], is the design flexibility it offers as the same circuit can be used for realizing both CPE and FI through an appropriate selection of the values of passive components. The functional block diagram for emulating a CPE is depicted in Figure 8.

Figure 8 Functional block diagram for CPE emulation [36]

The emulated impedance can be easily obtained by algebraic analysis as:

$$Z_{eq} = \frac{R_{VI}}{(\frac{\omega}{\omega_0})^{\alpha}} \tag{2.13}$$

where  $\omega_0$  denotes the unity-gain frequency of the differentiator and integrator and  $R_{VI}$  represents the equivalent resistance of the V/I converter.

The values of the pseudo-capacitance and conventional capacitance are given by:

$$\hat{C} = \frac{1}{R_{VI}\omega_0^{\alpha}} \tag{2.14}$$

$$C = \frac{1}{R_{VI}\omega_0{}^{\alpha}\omega^{1-\alpha}} \tag{2.15}$$

The functional block diagram illustrated in Figure 8 can be realized by CFOAs as active elements. A design based on CFOAs proposed in [36] is shown in Figure 9. As CFOAs can be directly cascaded, this leads to reducing the number of active components. The need of only grounded capacitors is also another advantage of this design due to minimizing the effect of parasitics in high frequencies of operation.

Figure 9 CPE emulation using CFOAs [36]

### 2.3 Rational Approximations

Several recursive structures for a CPE emulation were presented in [37-39, 41], all of which suffer from hardware complexity. An alternative solution for realizing a CPE is to approximate it from the rational approximation to accurately describe its fractional behavior. Therefore, finding the rational approximation of a CPE is the principal step in realizing it.

While irrationality of fractional transfer functions considers the complex s-plane, a rational approximation of the transfer function is described only by poles. Hence, rational functions often demonstrate better results during interpolation compared to polynomials. There are various rational approximation methods based on continued fraction expansion which can be considered equivalent to a certain finite continued fraction, as a ratio of two polynomials

can be given in the form of a finite continued fraction [41]. There are several methods listed in the literature to approximate irrational expansions such as Matsuda's method [41], Carlson's method [41], Charef's method [41], and continued fraction expansion (CFE). This work uses CFE due to its faster convergence and stability when compared to other methods.

#### 2.3.1 Continued Fraction Expansion (CFE)

Continued fraction expansion, on the other hand, is a method for the evaluation of functions and benefits from both faster convergence, larger domain of convergence in complex splane and also offers stable approximation [37, 39]. This approximation of an irrational function can be described by [38]:

$$G(s) \approx a_0(s) + \frac{b_1(s)}{a_1(s) + \frac{b_2(s)}{a_2(s) + \frac{b_3(s)}{a_3(s) + \cdots}}}$$

$$= a_0(s) + \frac{b_1(s)}{a_1(s) + \frac{b_2(s)}{a_2(s) + \frac{b_3(s)}{a_2(s) + \cdots}} \cdots$$

(2.16)

Where  $a'_{i}(s)$  and  $b'_{i}(s)$  are rational functions of variable s, or are constant. Applying the CFE method creates a rational function,  $\hat{G}(s)$ , that approximates the irrational function G(s).

Basically, a rational approximation of a CPE with transfer function  $G(s) = s^{-\alpha} \ 0 < \alpha < 1$  can be achieved by applying the CFE of functions [39]:

$$G_h(s) = \frac{1}{(1+sT)^{\alpha}}$$

(2.17)

$$G_l(s) = (1 + \frac{1}{s})^{\alpha}$$

(2.18)

Where  $G_h(s)$  and  $G_l(s)$  each denotes the approximation for high frequencies ( $\omega T >> 1$ ) and low frequencies ( $\omega << 1$ ), respectively.

#### 2.4 Various schemes of Switched-capacitor (SC) based integrators

There are several numerical integration schemes for realizing SC circuits among which Lossless Discrete Integrator (LDI), Bilinear Discrete Integrator (BDI) and Composite Discrete Integrator (CDI) are the most popular ones. A brief description of each of these integration schemes is presented in the following sections:

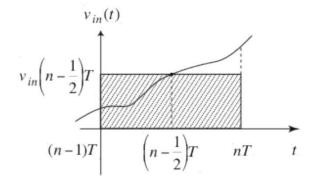

#### 2.4.1 Lossless Discrete Integrator (LDI)

The changes of  $V_{in}(t)$  versus time is illustrated in Figure 10 where the area of the shaded region can be calculated as

$$Area = Tv_{in}(nT - \frac{T}{2}) \tag{2.19}$$

Therefore,

$$v_o(nT) = v_o(nT - T) + Tv_{in}(nT - T/2)$$

(2.20)

Taking z-transform from the above equation, we can obtain the transfer function by [45]

$$H(z) = \frac{V_o(z)}{V_{in}(z)} = \frac{Tz^{-1/2}}{1 - z^{-1}}$$

(2.21)

$$H(s) = \frac{V_o(s)}{V_{in}(s)} = \frac{1}{s}$$

(2.22)

Figure 10 LDI

The corresponding s-to-z transform is further obtained as

$$s = \frac{1}{T} \frac{(1 - z^{-1})}{z^{-1}} = \frac{1}{T} (z - 1)$$

(2.23)

Although ideal integrators have zero magnitude and phase errors, attaining zero errors is not possible in non-ideal integrators due to physical constrains. Assuming a magnitude error of  $\varepsilon$  and phase error of  $\theta$ , the ideal integrator will become

$$H_{NI}(\omega) = \frac{1}{j\omega} (1+\varepsilon)e^{j\theta}$$

(2.24)

For the LDI,

$$H(e^{j\omega T}) = \frac{T}{e^{\frac{j\omega T}{2}} - e^{\frac{-j\omega T}{2}}}$$

(2.25)

Equating equations (2.35) and (2.36) gives the following magnitude and phase errors:

$$\varepsilon = \frac{\omega T}{2} \operatorname{csch}\left(\frac{\omega T}{2}\right) - 1$$

$$\theta = 0$$

(2.26)

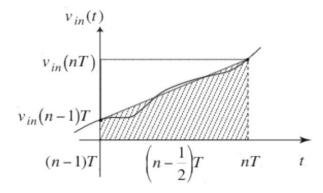

### 2.4.2 Bilinear Discrete Integrator (BDI)

The changes of  $V_{in}(t)$  versus time is illustrated in Figure 11 where the area of the shaded region can be calculated as

$$Area = \frac{T}{2} [v_{in}(nT - T) + v_{in}(nT)]$$

(2.27)

Therefore,

$$v_o(nT) = v_o(nT - T) + \frac{T}{2} [v_{in}(nT - T) + v_{in}(nT)]$$

(2.28)

Taking z-transform from the above equation, we can obtain the transfer function by [44]

$$H(z) = \frac{V_o(z)}{V_{in}(z)} = \frac{T}{2} \frac{1 + z^{-1}}{1 - z^{-1}}$$

(2.29)

Figure 11 BDI

The corresponding s-to-z transform is further obtained as

$$s = \frac{2}{T} \left( \frac{1 - z^{-1}}{1 + z^{-1}} \right) \tag{2.30}$$

Following the same process as for LDI, magnitude and phase errors can be found by:

$$\varepsilon = \frac{\omega T}{2} \cot\left(\frac{\omega T}{2}\right) - 1$$

$$\theta = 0$$

(2.31)

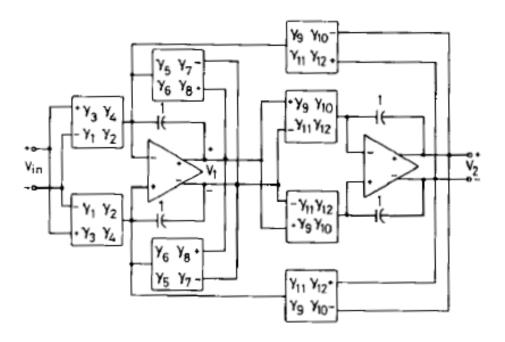

#### 2.4.3 Composite Discrete Integrator (CDI)

LDI and BDI are two most popular discrete integrators, which demonstrate zero phase error. However, both integrators suffer from magnitude errors in comparison to their analog counterparts. Composite discrete integrator (CDI) is formed by the linear combination of LDI and BDI in order to reduce the magnitude error [46]. These integrators are ideal candidates for high frequency applications as they minimize discrete integrator errors at higher frequencies and doubles the normal folding frequency.

Comparing the magnitude errors of LDI and BDI, two errors are opposite in sign. Hence, linear combination of two errors can minimize the magnitude error, yielding an optimal discrete integrator. The transfer function of CDI is obtained by:

$$s = \frac{\sigma T}{2} \left( \frac{1 + z^{-1}}{1 - z^{-1}} \right) + \delta T \left( \frac{z^{-1/2}}{1 - z^{-1}} \right)$$

(2.32)

Where  $0 < \sigma < \delta < 1$  are constants and define the CDI transformation in a way that  $\sigma + \delta = 1$ . The magnitude error of the integrated is calculated as:

$$\varepsilon = \frac{\omega T}{2} \left( \sigma \cot \left( \frac{\omega T}{2} \right) + \delta \csc \left( \frac{\omega T}{2} \right) \right) \tag{2.33}$$

This error can be minimized by using appropriate values for CDI transformation,  $\sigma$  and  $\delta$ . Magnitude error for LDI, BDI, CDI is shown in Figure 12, comparison of the magnitude error for different integrator schemes is shown in table 1

Figure 12 Magnitude errors for LDI, BDI and CDI

Table 1. Comparison of errors for various integration schemes

|     | Magnitude Error                                                 | Phase Error $(\theta)$ |  |

|-----|-----------------------------------------------------------------|------------------------|--|

| LDI | $\frac{\omega T}{2} Co \sec\left(\frac{\omega T}{2}\right) - 1$ | 0                      |  |

| BDI | $\frac{\omega T}{2} Cot \left(\frac{\omega T}{2}\right) - 1$    | 0                      |  |

#### CHAPTER 3 IMPLEMENTATION OF LOW VOLTAGE SC INTEGRATOR

#### 3.1 Introduction

SC circuits have widely been used in the design of integrated circuits due to their high precision, good linearity and dynamic range. Unlike, RC circuits which often requires tuning for proper operation. The frequency response of a SC circuit is dependent on clock frequency and capacitance-ratios, which can be set quiet precisely in an integrated circuit with 0.1% accuracy [48] and [50]. Due to its high precision, linearity, dynamic range SC circuits can be used to realize filters and wide variety of signal processing blocks such as gain stages, voltage controlled oscillators and modulators [48,49,50]. This chapter discuss basic building blocks used in SC circuits such as opamp, switches, clock signal generator, sample and hold circuit, which are implemented with low supply voltage of 0.7v and frequency ranges from dc to 1GHz in Cadence TSMC 65nm technology.

#### 3.2 The operational-amplifier (Opamp)

Opamp is an integral part of many analog and mixed signal systems. Opamp's are voltage amplifiers being used to achieve high gain by applying differential input. Typically, the gain of opamp ranges from 50 to 60 decibels [50]. There are different kind of opamp topologies that exist in literature. The performance of these topologies is compared in the table [2]

Table 2. Comparison of various topologies of operational amplifiers

|                    | Gain   | Output swing | Speed   | Power consumption | Noise  |

|--------------------|--------|--------------|---------|-------------------|--------|

| Two-stage          | High   | Highest      | Low     | Medium            | Low    |

| Telescopic         | Medium | Medium       | Highest | Low               | Low    |

| Folded-<br>cascode | Medium | Medium       | High    | Medium            | Medium |

| Gain boosted       | High   | Medium       | Medium  | High              | Medium |

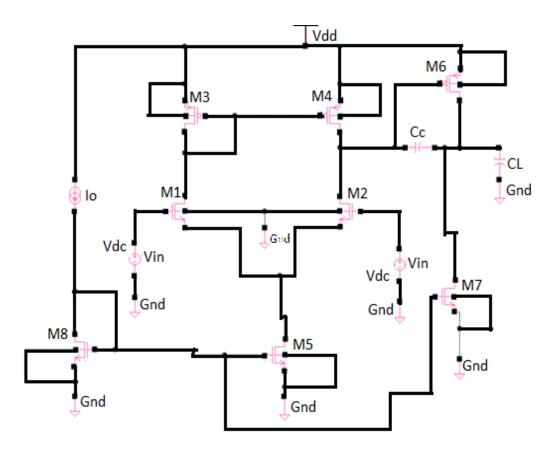

### 3.2.1 Two-stage operational-amplifier

In this work, two-stage opamp was designed with low supply voltage 0.7 V with good performance parameters for a SC circuit. The two-stage opamp can provide high gain and high output swing, the two-stage opamp is constructed using two gain stages the first gain stage is a differential input single ended output stage which is a symmetrical structure, second stage is normally a common source gain stage these two stages include eight MOS transistors and a capacitor Cc, for an amplifier all the MOSFET's should be in saturation region. The first stage has p-channel differential input pair M1, M2 with an n-channel diode connected current mirror active load M3, M4. The second stage is common source gain stage constructed using p-channel with active load M6, M7 for good output swing. The first stage and second stage is combined with a feedback capacitor of second stage serves as compensating capacitor (Cc) also called miller capacitor included for stability. The biasing for the two-stage opamp is provided using transistors M5, M8 and a current source ( $I_0$ ). General structure for two stage opamp is given in Figure 13.

Figure 13 Two-stage Operational amplifier

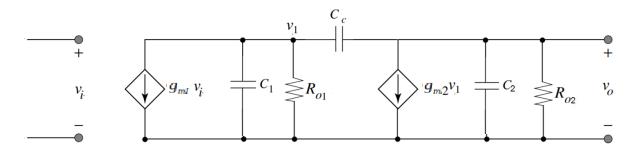

The small signal model for above two stage opamp is given below Figure 14

Figure 14 Small signal model of two-stage operational amplifier

$$V_1 = \frac{V_0 S C_c R_1 - g_{m1} R_1 V_{in}}{1 + S R_1 (C_1 + C_c)}$$

$$V_0\left(S(C_2 + C_c) + \frac{1}{R_2}\right) = V_1(SC_c - gm_2)$$

(3.2)

By combining above equations (3.1), (3.2) the transfer function of the circuit is approximated to

$$\frac{V_{out}}{V_{in}} = \frac{g_{m1}R_1g_{m2}R_2\left(1 - \frac{SC_c}{gm_2}\right)}{S^2\left(R_1R_2(C_1C_2 + C_1C_c + C_2C_c) + S(R_2(C_2 + C_c) + R_1(C_1 + C_c) + C_cR_1R_2gm_2) + C_cR_1R_2gm_2\right)}$$

(3.3)

The above equation is compared with traditional two poles and a zero-system given as

$$\frac{V_{out}}{V_{in}} = \frac{A_{DC} \left(1 - \frac{S}{Z}\right)}{\left(1 - \frac{S}{P_1}\right)\left(1 - \frac{S}{P_2}\right)}$$

(3.4)

From above equations (3.3), (3.4) the poles  $(P_1, P_2)$ , zeros (Z) and DC gain  $(A_{DC})$  is approximated as

$$P_1 \sim \frac{1}{gm_2 R_2 R_1 C_c} \tag{3.5}$$

$$P_2 \sim \frac{gm_2}{C_2} \tag{3.6}$$

$$Z \sim \frac{gm_2}{C_c} \tag{3.7}$$

$$A_{DC} = g_{m1} R_1 g_{m2} R_2 (3.8)$$

The gain band width product (GBP), slew rate (SR), phase margin (PM) are derived from above equations are given as

$Gain\ bandwidth\ product(GBP) = D.\ Cgain*P_1$

$$GBP = \frac{gm_1}{C_c} \tag{3.10}$$

$$SR = \frac{I_0}{C_C} \tag{3.11}$$

$$PM = -tan^{-1} \left( \frac{GBP}{10 * GBP} \right) - tan^{-1} (A_{DC}) - tan^{-1} \left( \frac{GBP}{P_2} \right)$$

(3.12)

After deriving all parameters of a two stage opamp, we derive  $\left(\frac{W}{L}\right)_N$  ratios for all the transistors depending on the specifications given for a switched capacitor circuit the DC gain should be higher than 40 dB, GBP should be greater than five times sampling or clock (switching) frequency (1MHz) and phase margin should be higher than 45 degrees more the phase margin the circuit is more stable [93, 94], Input common mode range ICMR (ICMR+, ICMR-) are 1.2v, 0.6v; load capacitor ( $C_L$ ) is 5pf, power less than 3 $\mu$ W, supply voltage 0.7v.

#### Design of the transistors $M_1$ and $M_2$ :

The approximate value of the current ( $I_D$ ) is given in equation (3.13). To determine the response of the circuit to the ac input we require transconductance parameter ( $g_m$ ) of a transistor. The  $g_m$  equation for a MOS transistor is given in equation (3.14). The  $\left(\frac{W}{L}\right)_N$  ratio for  $M_1$ ,  $M_2$  is given in equation (3.17).

$$I_D \approx \frac{\mu_n c_{ox}}{2} \left(\frac{W}{L}\right) \left(V_{gs} - V_{th}\right)^2 \tag{3.13}$$

$$g_m = \frac{\partial I_D}{\partial V_{gs}} = \mu_n c_{ox} \left(\frac{W}{L}\right) \left(V_{gs} - V_{th}\right)$$

(3.14)

$$g_m^2 = \left[\mu_n c_{ox} \left(\frac{W}{L}\right)\right]^2 \frac{\left(V_{gs} - V_{th}\right)^2}{2} * 2$$

(3.15)

For

$$M_{1}$$

,  $M_{2}$ ;  $2I_{D} = I_{5}$  (3.16)

$$\left(\frac{W}{L}\right)_{1,2} = \frac{gm_1^2}{\mu_n c_{ox} * I_5} \tag{3.17}$$

Design of the transistors  $M_3$  and  $M_{4:}$

$$\left(\frac{W}{L}\right)_{3,4} = \frac{2I_{D3}}{\mu_p c_{ox} \{V_{DD} - (ICMR +) - V_{t3max} + V_{t1min}\}^2}$$

(3.18)

Design of the transistor M<sub>5:</sub>

$$V_{Dsat} \ge (ICMR -) - \frac{2I_D}{\mu_n c_{ox} \left(\frac{W}{L}\right)} - V_{t1max}$$

(3.19)

$$\left(\frac{W}{L}\right)_{5} = \frac{2I_{D5}}{\mu_{n}c_{ox} * (V_{Dsat})^{2}}$$

(3.20)

Design of the transistors M<sub>6</sub>, M<sub>7</sub>:

$$\left(\frac{W}{L}\right)_6 = \frac{I_6}{I_4} \left(\frac{W}{L}\right)_4 \tag{3.21}$$

$$\left(\frac{W}{L}\right)_6 = \frac{gm_6}{gm_4} \left(\frac{W}{L}\right)_4 \tag{3.22}$$

$$\left(\frac{W}{L}\right)_7 = \frac{I_7}{I_5} \left(\frac{W}{L}\right)_5 \tag{3.23}$$

Table 3 Parameters for the designed Operational amplifier

| Device                          | Value      |  |

|---------------------------------|------------|--|

| $M_{1,} M_{2}$                  | 3u/500u    |  |

| M <sub>3</sub> , M <sub>4</sub> | 7u/500u    |  |

| M <sub>5</sub>                  | 6u/500u    |  |

| $M_6$                           | 87u/500u   |  |

| M <sub>7</sub>                  | 37.5u/500u |  |

| C <sub>C</sub>                  | 3.3pf      |  |

| $C_{\mathrm{L}}$                | 5pf        |  |

| $I_0$                           | 20u        |  |

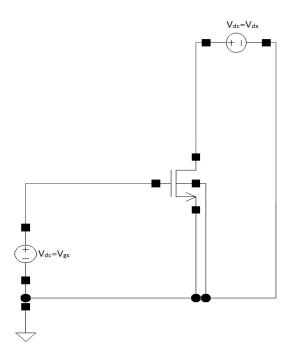

The opamp circuit is designed to operate with a supply voltage of 0.7 V. The circuit in Figure 15 is designed to measure the threshold voltage of the NMOS transistor and similar procedure is followed for the PMOS transistor as well. The threshold voltages of NMOS and PMOS transistors are 0.335 V and |-0.300| V respectively.

Figure 15 NMOS Configuration to Obtain Threshold Voltage

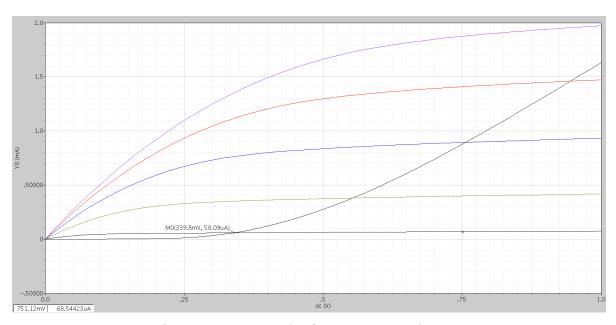

Figure 16  $I_{ds}\,vs\;V_{th}$  Plot for NMOS Transistor

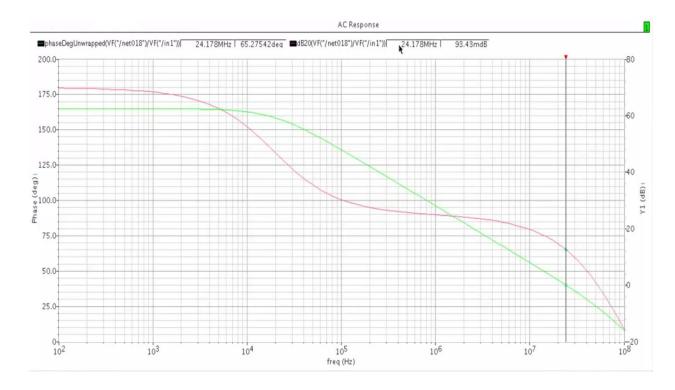

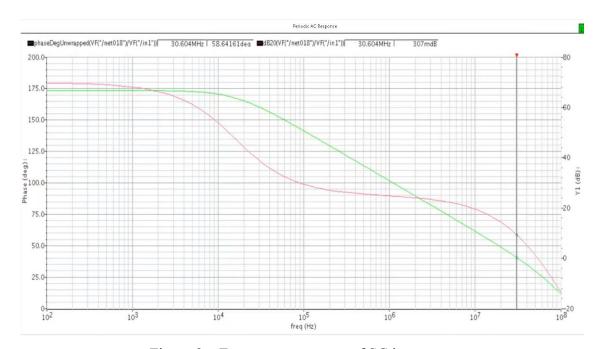

Figure 17 Frequency response of Operational amplifier

From the simulation with AC analysis, we can measure the behavior of the design for different frequencies. The frequency response of operational amplifier is shown in Figure 17 and the parameters are tabulated in Table 4.

Table 4 Performance Parameters of designed Operational amplifier

| Process              | 65nm       |  |

|----------------------|------------|--|

| Supply Voltage       | 0.7 V      |  |

| Gain                 | 62 dB      |  |

| Unity Gain Bandwidth | 24MHz      |  |

| Power Consumption    | 2.25μW     |  |

| Phase Margin         | 65 degrees |  |

| Slew rate            | 3v/μsec    |  |

| ICMR+                | 1.2v       |  |

| ICMR-                | 0.6v       |  |

#### 3.3 MOSFET Switches

Switches are used to control flow of charge in SC circuit. An ideal switch has zero ON resistance which results in lossless charge flow. But, due to non-idealities in MOSFETs the occurrence of resistive loads between capacitors in SC is unavoidable that limits the charge transfer between the capacitors. Generally, switches are implemented using single NMOS or PMOS transistor shown in below Figure 18-a. A single MOSFET operating in triode region when used as switch whose drain to source ON resistance is given in Equation (3.25), these single transistor switch limits the output swing. It is often good to use a transmission gate as switch which is parallel combination of NMOS and PMOS transistors for better output swing is shown in Figure 18-b. The ON resistance of transistor gate is

parallel combination of NMOS and PMOS drain to source resistance is given Equations (3.24, 3.25)

Figure 18-a NMOS Transistor as switch, Figure 18-b Transmission gate as switch [49]

$$R_{on} = R_{DS1} / / R_{DS2} (3.24)$$

$$R_{DS} = \frac{1}{K_n' \left(\frac{W}{L}\right)_N V_{eff}}$$

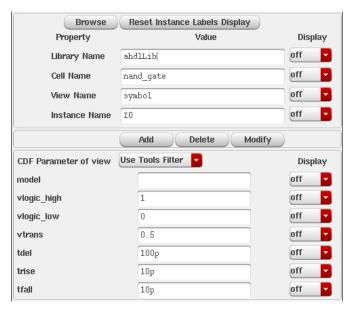

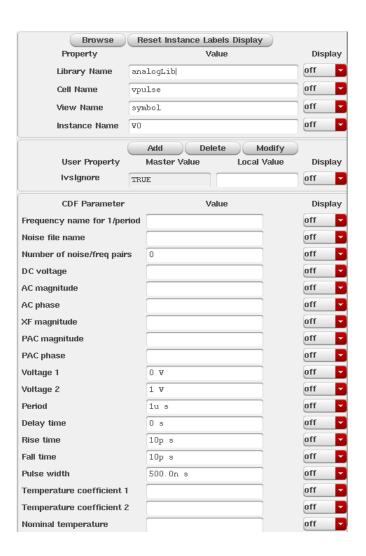

(3.25)

The transmission gate as switch is designed and simulated in cadence TSMC 65nm CMOS technology. The W/L ratios of PMOS and NMOS transistors are 2.6um/130nm and 2.6um/130nm, respectively upon the assumption that all the transistors are identical as shown in below Figure (19).

Figure 19. Transmission gate as switch in cadence

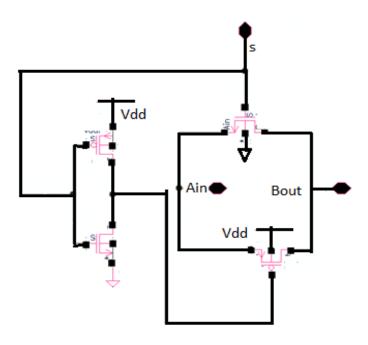

## 3.4 Clock Signal Generator

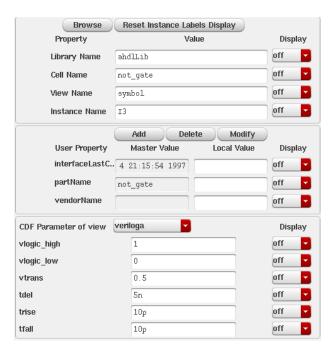

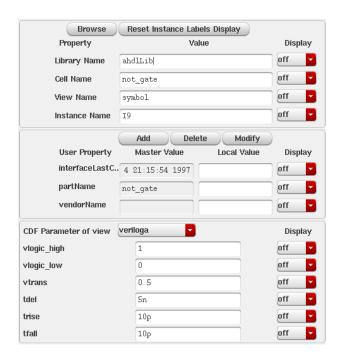

The clock signals are non-overlapping signals, which will drive the charge in SC circuits, these non-overlapping signals are separated with a delay of time period 'T' shown in Figure 21. These clock signals are generated using clock generator that is constructed using NAND gates and inverters as shown in Figure 20.

Figure 20. Sample clock signal generator

Figure 21. Non-overlapping clock signal

## 3.5 Sample and Hold (S/H) circuit

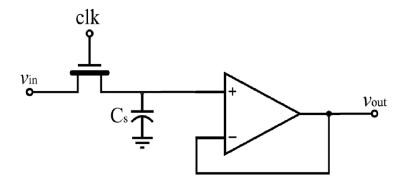

The output of switch capacitor circuit is only valid at end of phase  $(\Phi_1)$ , it is therefore, necessary to sample the SC circuit output at phase  $(\Phi_1)$ . This is done by implementing a simple open loop S/H circuit shown in Figure 22. Where, the single output op-amp designed earlier is used to implement as buffer, the switches are implemented with transmission gate for full output swing, the holding capacitor (Cs) is set to 1pf.

Figure 22 Sample and Hold circuit

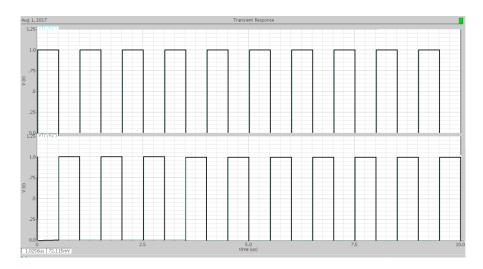

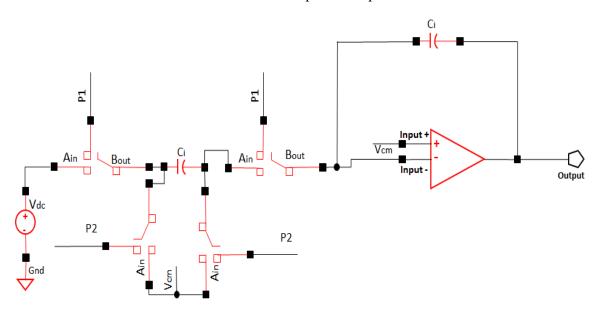

## 3.6 SC Integrator

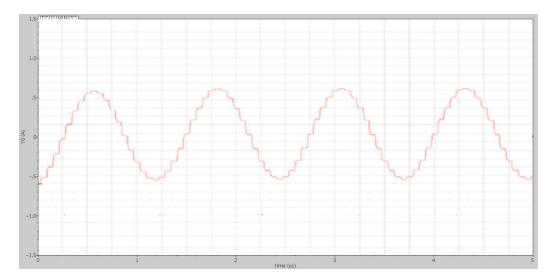

All the parameters designed earlier are used to implement the SC integrator shown in Figure 23 was designed and simulated in Cadence TSMC 65nm CMOS technology. The simulation parameters used for the SC integrator are given below, the output sine wave for designed SC integrator is shown in Figure 24, the frequency response is shown in Figure 25 and parameters are tabulated in Table 5.

$$V_{DD} = 0.7 \text{ V Vin} = 600 \text{mV Fin} = 1 \text{MHz Ci} = 1 \text{pF Cs} = 10 \text{pf}$$

Figure 23 SC integrator

$$\frac{V_o}{V_{in}} = \frac{-C_s}{C_i} \left( \frac{Z^{-1/2}}{1 + Z^{-1}} \right) \tag{3.26}$$

Figure 24. Output sine wave of SC integrator

Figure 25. Frequency response of SC integrator

#### 3.6.1 Parameters of SC integrator

#### 3.6.1.1 Supply Voltage

The SC integrator is designed to provide high slew rate with low power dissipation, which is achieved by the low supply voltage  $V_{dd} >= V_{tn} + |V_{tp}|$ . The  $V_{tn}$  and  $V_{tp}$  of the gate-driven transistors in TSMC 65nm technology are 0.335 V and |-0.300|V respectively. Hence a supply voltage of 1 V or 0.7 V can be used to operate all the transistors in their saturation region. As the SC circuit is designed in the voltage-mode, a small change in the voltage can produce a large output swing. Thus, making the circuit operable efficiently with a small supply voltage of 0.7v.

## 3.6.1.2 Power Consumption

In general, the total power consumption of the circuit depends on the static when the input is not switching and dynamic power. The static power consumption is the product of leakage current and the supply voltage when the input signal is not switching. In this design, the static power consumption is due to the leakage current in the transistors along with the consumption due to sub-threshold conduction between source to drain and reverse bias p-n junction between terminals and substrate. To measure the static power consumption, a static supply voltage of 0.7 V is used and is shown in the Figure 26.

Figure 26. Static Current Measurement from a Supply Voltage of 0.7 V

From the Figure, the current drawn by the integrator circuit is 135nA. So, the power consumed for the supply voltage of 0.7 V is

$$P = |V * I| = |0.7 V * 135 nA| = 94.5 nW.$$

(3.27)

Dynamic power is due to the charging and discharging of the load capacitance when a transition takes place at the input from high to low or low to high, and is given by

$$C_L * (Vdd)_2 * f = 5pF * (0.7)_2 * (1/10\mu s) = 2.45 \mu W$$

(3.28)

Hence the total power consumption is  $2.49\mu W$ .

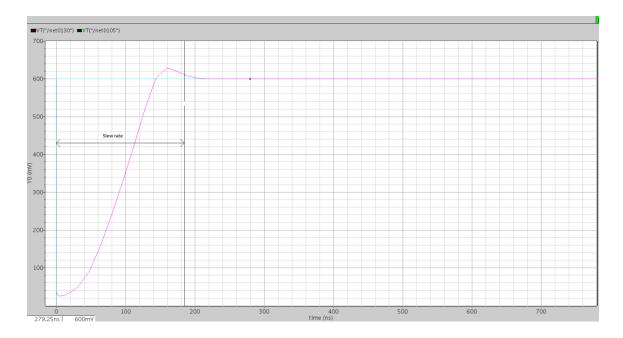

## 3.6.1.3 Settling Time and Slew Rate

Slew rate is the rate at which output changes for a step change in the input, which is how quickly the systems responds to a large signal change. Settling time is the time taken for the output to settle to a final value within the specified error band. It is shown in the Figure 27 that the time taken to reach its maximum value is 25ns with a load capacitor of 5pF. The op-amp based SC integrator has a high slew rate of 3 V/µs and settling time of 25ns.

Figure 27. Slew rate of SC integrator

$$slewrate = \frac{620mv(high) - 20mv(low)}{200ns - 10ns} \approx 3v/\mu sec$$

(3.29)

The settling time at the output depends on the transistor size and the supply voltage, faster settling can be achieved by increasing the size of the transistor and supply voltage.

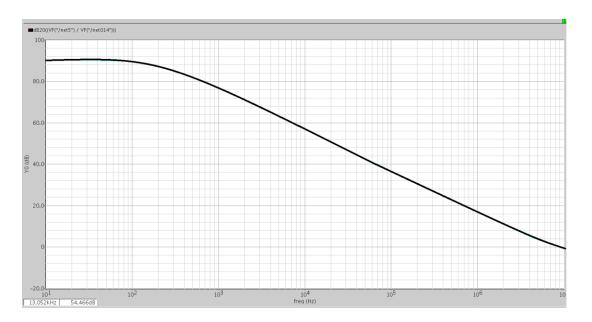

#### 3.6.1.4 Power Supply Rejection Ratio (PSRR)

In general, power supply rejection ratio is an important factor for any circuit to maintain its stability at output to eliminate high noise signals. If there is a change in the supply voltage  $(V_{DD})$  of a circuit, then the output varies accordingly. In this circuit, all the transistors are in the saturation region and the transistor operation region is operated by the gate voltage  $(V_{gs})$  and the supply voltage  $(V_{DD})$ . As the NMOS transistor is directly connected to the supply voltage, any change in the supply voltage can drive the transistor in to the cut-off or active regions. The change in supply voltage tends to change the output voltage. This ratio is generally considered as the power supply rejection ratio (PSRR). The PSRR of the SC integrator is shown in the Figure 28.

Figure 28. Frequency verses PSRR Plot of SC integrator

Here, the PSRR is measured at the negative terminal of the supply voltage. Hence it is considered as PSRR-, which is expressed in "-dB". The "PSRR-" of SC integrator at 1 KHz is 79dB, which has better PSRR.

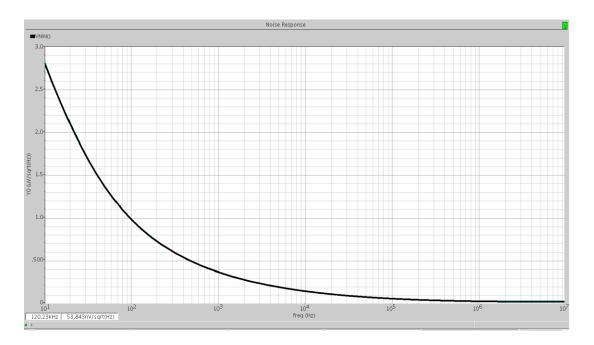

## 3.6.1.1 Noise Analysis

Any MOS transistor consists of two major sources of noise: thermal and flicker noise, the thermal noise is also referred as white noise that occurs primarily at higher frequencies whereas flicker noise dominates the system at lower frequencies because of the increase in spectral density.

Thermal Noise: The channel thermal noise in the saturation region of MOS transistor is given as

$$(I^2)_{thermal\ noise} = 4.K.T. \in g_m [A^2/Hz]$$

(3.30)

Where K is a Boltzmann constant,

T is absolute temperature

g<sub>m</sub> is trans conductance of the device

∈ is complex function of the basic parameter of transistor and bias conditions given as ∈ =2/3 in strong inversion and 1/2 in weak inversion of MOSFET

By substituting all the values in equation (3.30), the thermal noise of a MOS transistor can be calculated

#### Flicker Noise

This is the other dominant source of noise in a MOS transistor that occurs due to the increase in spectral density (1/f) at lower frequencies, which is given as

$$(V^2)_{Flicker\ noise} = \frac{K_f}{C_{ox}^2 \cdot W \cdot L \cdot f} \quad [V^2/Hz]$$

(3.31)

Where  $K_f$  is a process dependent parameter of the device,

W and L are width and length of the transistor

Cox is the gate-oxide capacitance per unit area

f is the frequency

The input referred noise of the SC integrator is shown in the Figure 29

Figure 29 Input referred Noise of SC integrator

Intrinsic noise in an opamp is given as, equation

$$\frac{16KT}{3g_m} + \frac{K}{C_{ox}WLf} \approx \frac{16KT}{3g_m} \tag{3.32}$$

The noise in opamp is inversely proportional to the input trans-conductance. The input trans-conductance of an opamp is low since the input drives a NMOS thereby reducing the total noise in the opamp

From all the performance measurements observed, Table 5 shown below is formulated giving the details of designed SC integrator:

Table 5 Performance Parameters of SC integrator

| Process                        | 65nm                                     |

|--------------------------------|------------------------------------------|

| Supply Voltage                 | 0.7 V                                    |

| Gain                           | 62 dB                                    |

| Unity Gain Bandwidth           | 30MHz                                    |

| Power Consumption              | 2.49μW                                   |

| Settling time                  | 25ns                                     |

| Slew rate                      | 3v/μsec                                  |

| Power Supply Rejection Ratio   | 79db                                     |

| Input Referred noise at 120KHz | 54 nV/Sqrt(Hz) @ V <sub>in</sub> =100 mV |

#### CHAPTER 4 IMPLEMENTATION OF CPE USING SC BIQUADS

#### 4.1 Approximation of CPE using CFE

There are different methods to realize approximations of CPEs including Continued Fraction Expansions (CFEs) and rational approximation methods such as Matsuda's method, Least square method, Chareff's method, Carlson's method. Continued fraction expansion (CFE) is a an approximation method which benefits from both faster convergence, larger domain of convergence in complex s-plane as well as offering stable approximation [38]. Hence, CFE method was selected in this work to model the CPE simulations. This approximation begins with the CFE of  $(1 + x)^{\alpha}$  given as:

$$(1+x)^{\alpha} = \frac{1}{1 - \frac{\alpha x}{1 + \frac{(1+\alpha)x}{2 + \frac{(1-\alpha)x}{3 + \frac{(2-\alpha)x}{5 + \cdots}}}}$$

(4.1)

After substituting x = s - 1 into the equation (4.1), an approximation of  $s^{\alpha}$  with the order determined by the number of terms that are truncated could be realized. For example, truncating at the 9<sup>th</sup> term of equation (4.1) with an  $\alpha$  of 0.5 yields

$$\frac{1}{s^{0.5}} \approx \frac{s^4 + 36s^3 + 126s^2 + 84s + 9}{9s^4 + 84s^3 + 126s^2 + 36s + 1} \tag{4.2}$$

$$\approx 0.1111 + \frac{1.899696037}{s + 7.54632170} + \frac{0.5378392488}{s + 1.420276625} + \frac{0.2962962975}{s + 0.33333333} + \frac{0.2291313787}{s + 0.03109120413}$$

$$(4.3)$$

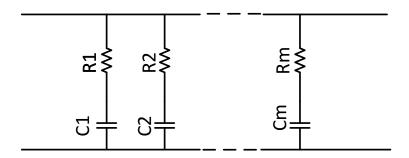

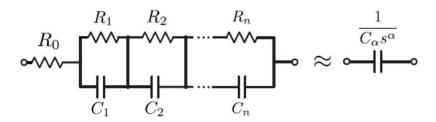

The obtained approximation of a CPE from equation 4.3 gives is centered around a frequency of 1 rad/s. This can be physically realized by the RC ladder network given in Figure 30 using the approximation of the fractional Laplace transform operator. The impedance of this RC ladder network can be given as

$$Z = R_0 + \frac{1/C_1}{S + \frac{1}{R_1 C_1}} + \frac{1/C_2}{S + \frac{1}{R_2 C_2}} + \dots + \frac{1/C_n}{S + \frac{1}{R_n C_n}}$$

(4.4)

Figure 30 RC ladder structure to realize Nth order integer approximation of CPE with pseudo-capacitance Cα [37]

The resistor and capacitor values for the RC ladder in Figure 30 can be obtained through equating terms of equations 4.3 and 4.4. An approximation of CPE with any desired capacitance,  $C_{\alpha}$ , centered around any frequency,  $w_c$ , can be designed by applying magnitude and frequency scaling factors to the component values in the ladder realization. The resistor and capacitor values become

$$R_s = R. K_m$$

$$C_s = \frac{C}{K_f K_m}$$

(4.5)

where  $R_s$  and  $C_s$  denote the scaled resistor and capacitor values, R and C are the unscaled resistor and capacitor values,  $k_m = \frac{1}{C_\alpha w_c^\alpha}$  is the magnitude scaling factor (where  $C_\alpha$  is the CPE pseudo-capacitance) and  $K_f = w_c$  is the frequency scaling factor.

The component values required for the 4th order approximation of the CPE with using the RC ladder network in Figure 30, shifted to a center frequency of 1 kHz with the capacitance values of 173.94  $\mu F$ , 12.6  $\mu F$ , 0.915095  $\mu F$  for  $\alpha$  = 0.2, 0.5, 0.8, respectively, are given in Table 6.

Table 6 Approximated CPE Component Values

| n . | $C = 173.94 \ \mu F$ $a = 0.2$ |             | $C = 12.6 \ \mu F$ $a = 0.5$ |           | $C=0.915095 \ \mu F$<br>a=0.8 |             |

|-----|--------------------------------|-------------|------------------------------|-----------|-------------------------------|-------------|

|     | $R_n(\Omega)$                  | $C_n(nF)$   | $R_n(\Omega)$                | $C_n(nF)$ | $R_n(\Omega)$                 | $C_n(nF)$   |

| 0   | 431.818181818                  | 1           | 111.1                        | -         | 18.3792815                    |             |

| 1   | 285.1913524                    | 53.49972187 | 251.7                        | 83.7      | 92.76920844                   | 301.340646  |

| 2   | 241.4157687                    | 375.4884242 | 378.7                        | 296       | 236.1807585                   | 585.2199857 |

| 3   | 337.1779269                    | 1113.835967 | 888.9                        | 537.16    | 981.5955911                   | 635.3180544 |

| 4   | 1020.186243                    | 2804.277173 | 7369.7                       | 695       | 53080.16637                   | 272.9744084 |

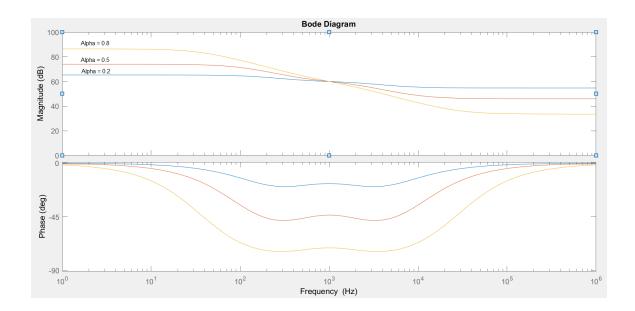

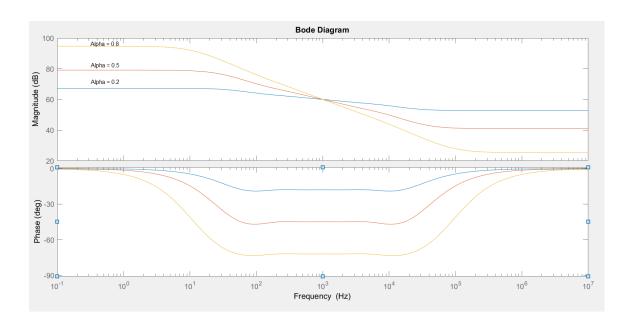

The  $2^{nd}$  order and  $4^{th}$  order transfer functions in S-domain obtained from above table are given in following equations 4.6 to 4.11 and their frequency response obtained from MATLAB are shown in below Figures 31 and 32, for  $\alpha = 0.2, 0.5, 0.8$ , respectively.

$$\frac{V_0}{V_{in}} = \frac{545.4545454*S^2 + 18848999.9*S + 39476088988}{S^2 + 18848.99999 *S + 21532412.16}$$

(4.6)

$$\frac{V_0}{V_{in}} = \frac{200*S^2 + 12565996.5*S + 39476038000}{S^2 + 12565.98248 *S + 7895206.177}$$

(4.7)

$$\frac{V_0}{V_{in}} = \frac{47.6190476 * S^2 + 8377333.334 * S + 39476089011.0}{S^2 + 8377.3333333 * S + 1879813.761}$$

(4.8)

Figure 31 Frequency response for 2nd order approximation for  $\alpha = 0.2, 0.5, 0.8$

$$\frac{V_0}{V_{in}} = \frac{431.8181818*S^4 + 56975386.32*S^3 + 9.546036017*10^{11}*S^2 + 3.141691319*10^{15}*S + 1.558361558*10^{18}}{S^4 + 79584.66658*S^3 + 954603599.8*S^2 + 2.249165357*10^{12}*S + 6.729288516*10^{14}}$$

(4.9)

$$\frac{V_0}{V_{in}} = \frac{111.1 * S^4 + 25145371.44 * S^3 + 5.529527451 * 10^11 * S^2 + 2.315741971 * 10^15 * S + 1.55833369 * 10^18}{S^4 + 58677.49888 * S^3 + 552964598.7 * S^2 + 9.925757646 * 10^11 * S + 1.73146264 * 10^14}$$

(4.10)

$$\frac{V_0}{V_{in}} = \frac{18.3792815 * S^4 + 11085794.48 * S^3 + 3.30847222 * 10^1 * 1 * S^2 + 1.763756566 * 10^1 * 5 * 1.558361602 * 10^1 * 18}{S^4 + 44679.1111 * S^3 + 330847222.1 * S^2 + 4.376238097 * 10^1 * 1 * S + 2.864156647 * 10^1 * 13}$$

$$(4.11)$$

Figure 32 Frequency response for 4th order approximation for  $\alpha = 0.2, 0.5, 0.8$

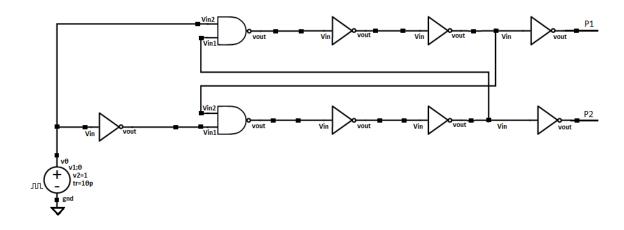

## 4.2 Realization of CPE using BDI-based SC biquad

SC circuits have been widely used in the design of integrated circuits due to their high precision compared to normal RC-circuits which often require a tuning circuit to ensure proper operation. The frequency response of SC circuits is ideally a function of capacitor ratios, whereas the frequency response of RC-circuits is highly dependable on the operating temperature and the fabrication process. Capacitor ratios can be made very precise and almost independent of fabrication errors.

SC circuits operate by charging and discharging capacitors with a predefined switching scheme consisting of two or more non-overlapping clock signals. The total charge transferred during the switching period averaged over time be a current. This makes them possible to emulate resistors.

The charging and discharging of a capacitor ideally acts as a simple sample and hold circuit. This sampling property makes it possible to describe the functionality of SC circuits using

Discrete Time z-domain transfer functions. Hence, the SC circuit can be realized by implementing either LDI, BDI or CDI.

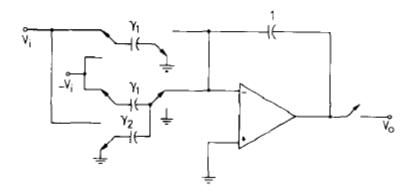

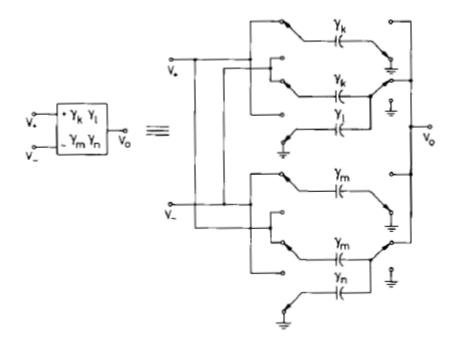

#### 4.2.1 BDI-based SC biquad

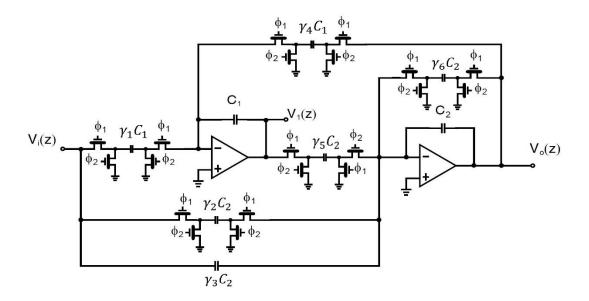

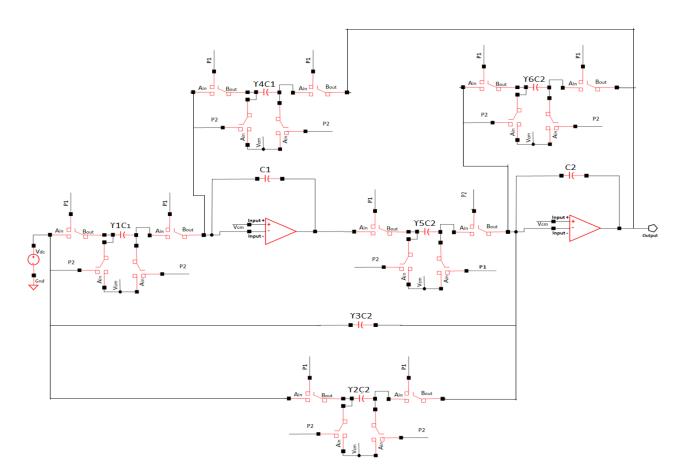

A general bi-quad switched capacitor circuit can be realized through the following discrete time transfer function is demonstrated in Figure 33 [44,51].

$$H(z) = \frac{a_0 + a_1 z^{-1} + a_2 z^{-2}}{1 + b_1 z^{-1} + b_2 z^{-2}}$$

(4.12)

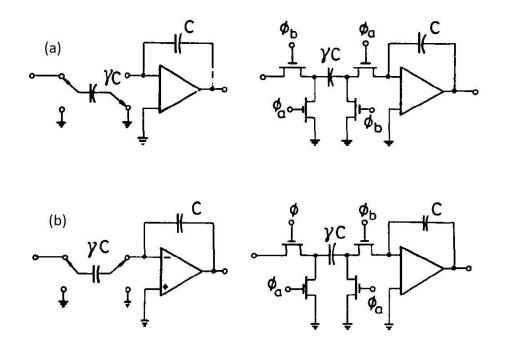

This circuit follows the two-integrator-loop topology and implements the noninverting forward-Euler (FEDI) and backward-Euler discrete integrator (BEDI). The schematics of these two integrators are shown in Figure 34. Transmission zeros can be realized using the feedforward technique. We assume that  $\phi_a$  and  $\phi_b$  are non-overlapping clocks and the output voltage of each block (V<sub>1</sub> and V<sub>2</sub>) are sampled at the end of clock  $\phi_b$ . Therefore, transfer function of each block can be obtained by:

$$T_1(z) = \frac{V_1}{V_{in}} = \frac{A_0 + A_1 z^{-1} + A_2 z^{-2}}{C_0 + C_1 z^{-1} + C_2 z^{-2}}$$

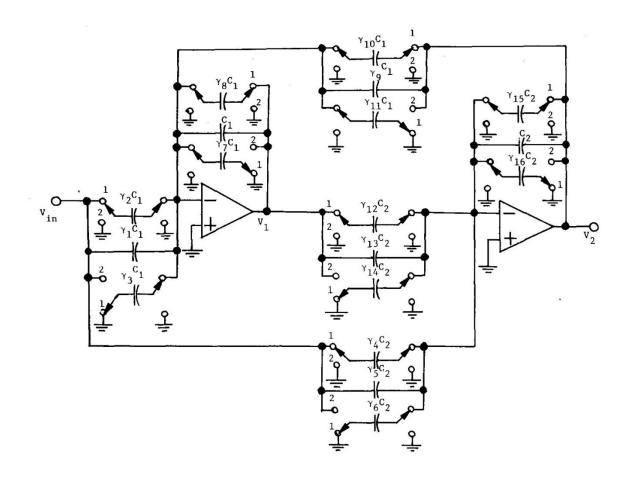

(4.13)

$$T_2(z) = \frac{V_2}{V_{in}} = \frac{B_0 + B_1 z^{-1} + B_2 z^{-2}}{C_0 + C_1 z^{-1} + C_2 z^{-2}}$$

Figure 33 General SC biquad [44]

Figure 34 (a) Forward-Euler discrete integrator, (b) Backward-Euler integrator [44]

Where coefficients can be calculated as