# LOW VOLTAGE CMOS ANALOG CIRCUIT DESIGN USING BODY-DRIVEN TECHNIQUES

by

Xuguang Zhang

Submitted in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

Major Subject: Electrical and Computer Engineering

at

DALHOUSIE UNIVERSITY

Halifax, Nova Scotia

April, 2004

© Copyright by Xuguang Zhang, 2004

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisisitons et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-612-93285-0 Our file Notre référence ISBN: 0-612-93285-0

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats. L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou aturement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this dissertation.

While these forms may be included in the document page count, their removal does not represent any loss of content from the

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de ce manuscrit.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

## Canadä

dissertation.

#### **DALHOUSIE UNIVERSITY**

To comply with the Canadian Privacy Act the National Library of Canada has requested that the following pages be removed from this copy of the thesis:

Preliminary Pages

Examiners Signature Page

Dalhousie Library Copyright Agreement

Appendices

Copyright Releases (if applicable)

To my parents Baohua and Huimin for their profound love and support

#### **Table of Contents**

| List of | Table  | s                                               | ix                     |

|---------|--------|-------------------------------------------------|------------------------|

| List of | Figur  | es                                              | x                      |

| List of | Abbre  | eviations                                       | xiv                    |

| Ackno   | wledge | ement                                           | xiv                    |

| Abstra  | act    |                                                 | $\mathbf{x}\mathbf{v}$ |

| Chapt   | er 1   | INTRODUCTION                                    | 1                      |

| 1.1     | LOW-   | VOLTAGE DESIGN STRATEGIES                       | 1                      |

|         | 1.1.1  | Body-Driven Technique                           | 3                      |

|         | 1.1.2  | Floating-Gate Technique                         | 7                      |

|         | 1.1.3  | Self-Cascode Technique                          | 11                     |

|         | 1.1.4  | Level-Shifting Technique                        | 12                     |

|         | 1.1.5  | Subthreshold Technique                          | 15                     |

|         | 1.1.6  | Dynamic Threshold Voltage MOSFET                | 17                     |

| 1.2     | ORGA   | ANIZATION                                       | 19                     |

| Chapt   | er 2   | BODY-DRIVEN MOSFET MODEL                        | 20                     |

| 2.1     | MOSI   | FET MODELS                                      | 20                     |

| 2.2     | OVEF   | RVIEW OF BSIM3V3 MODEL                          | 22                     |

| 2.3     | THRE   | ESHOLD VOLTAGE MODEL IN BSIM3V3                 | 23                     |

| 2.4     | JUNC   | TION DIODE                                      | 30                     |

| 2.5     | BSIM   | 3V3 DEFICIENCIES IN SIMULATING BODY-DRIVEN MOS- |                        |

|         | FET .  | AND IMPROVEMENTS                                | 31                     |

|            | 2.5.1                                                              | Rody Junation Diada Commant                                                                                                                                                                                                                                                                                                                                                                                |                                                    |

|------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|            |                                                                    | Body Junction Diode Current                                                                                                                                                                                                                                                                                                                                                                                | 32                                                 |

|            | 2.5.2                                                              | Threshold Voltage                                                                                                                                                                                                                                                                                                                                                                                          | 33                                                 |

|            | 2.5.3                                                              | Body Junction Capacitance                                                                                                                                                                                                                                                                                                                                                                                  | 35                                                 |

|            | 2.5.4                                                              | Missing Parameters and Improved Model                                                                                                                                                                                                                                                                                                                                                                      | 37                                                 |

| 2.6        |                                                                    | FET SCALING MODELS                                                                                                                                                                                                                                                                                                                                                                                         | 44                                                 |

| 2.7        | SCAI                                                               | LABILITY OF BODY-DRIVEN MOSFET PARAMETERS                                                                                                                                                                                                                                                                                                                                                                  | 46                                                 |

|            | 2.7.1                                                              | Threshold Voltage                                                                                                                                                                                                                                                                                                                                                                                          | 46                                                 |

|            | 2.7.2                                                              | Driving Capability                                                                                                                                                                                                                                                                                                                                                                                         | 48                                                 |

|            | 2.7.3                                                              | Transconductance                                                                                                                                                                                                                                                                                                                                                                                           | 53                                                 |

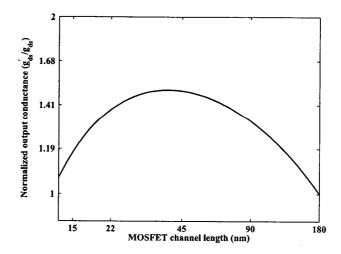

|            | 2.7.4                                                              | Output Conductance                                                                                                                                                                                                                                                                                                                                                                                         | 56                                                 |

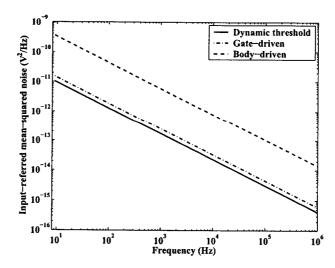

|            | 2.7.5                                                              | Input-Referred Noise Voltage                                                                                                                                                                                                                                                                                                                                                                               | 58                                                 |

| 2.8        | CON                                                                | CLUSION                                                                                                                                                                                                                                                                                                                                                                                                    | 63                                                 |

| Cl 4       | 0                                                                  | DECLY APPROPRIE                                                                                                                                                                                                                                                                                                                                                                                            |                                                    |

| Chapt      | er 3                                                               | REGULATED BODY-DRIVEN CMOS CURRENT MIF                                                                                                                                                                                                                                                                                                                                                                     | <b>t-</b> .                                        |

|            |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                            |                                                    |

|            |                                                                    | ROR FOR LOW-VOLTAGE APPLICATIONS                                                                                                                                                                                                                                                                                                                                                                           | 65                                                 |

| 3.1        |                                                                    | ROR FOR LOW-VOLTAGE APPLICATIONS ODUCTION                                                                                                                                                                                                                                                                                                                                                                  | <b>65</b>                                          |

| 3.1<br>3.2 |                                                                    | ROR FOR LOW-VOLTAGE APPLICATIONS                                                                                                                                                                                                                                                                                                                                                                           |                                                    |

|            | CM U                                                               | ROR FOR LOW-VOLTAGE APPLICATIONS ODUCTION                                                                                                                                                                                                                                                                                                                                                                  | 65                                                 |

| 3.2        | CM U                                                               | ROR FOR LOW-VOLTAGE APPLICATIONS ODUCTION                                                                                                                                                                                                                                                                                                                                                                  | 65<br>69                                           |

| 3.2        | CM U                                                               | ROR FOR LOW-VOLTAGE APPLICATIONS ODUCTION USING LEVEL-SHIFTING TECHNIQUE LE AND CASCODE BODY-DRIVEN CURRENT MIRROR                                                                                                                                                                                                                                                                                         | 65<br>69<br>70                                     |

| 3.2        | CM U<br>SIMP<br>3.3.1                                              | ROR FOR LOW-VOLTAGE APPLICATIONS ODUCTION USING LEVEL-SHIFTING TECHNIQUE LE AND CASCODE BODY-DRIVEN CURRENT MIRROR Simple Body-Driven Current Mirror                                                                                                                                                                                                                                                       | 65<br>69<br>70<br>70                               |

| 3.2        | CM U<br>SIMP<br>3.3.1<br>3.3.2                                     | ROR FOR LOW-VOLTAGE APPLICATIONS ODUCTION USING LEVEL-SHIFTING TECHNIQUE LE AND CASCODE BODY-DRIVEN CURRENT MIRROR Simple Body-Driven Current Mirror Improved Simple Body-Driven Current Mirror Cascode Body-Driven Current Mirror                                                                                                                                                                         | 65<br>69<br>70<br>70<br>70                         |

| 3.2        | SIMP<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4                           | ROR FOR LOW-VOLTAGE APPLICATIONS ODUCTION USING LEVEL-SHIFTING TECHNIQUE LE AND CASCODE BODY-DRIVEN CURRENT MIRROR Simple Body-Driven Current Mirror Improved Simple Body-Driven Current Mirror Cascode Body-Driven Current Mirror Improved Cascode Body-Driven Current Mirror                                                                                                                             | 65<br>69<br>70<br>70<br>70<br>72                   |

| 3.2        | SIMP<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4                           | ROR FOR LOW-VOLTAGE APPLICATIONS ODUCTION USING LEVEL-SHIFTING TECHNIQUE LE AND CASCODE BODY-DRIVEN CURRENT MIRROR Simple Body-Driven Current Mirror Improved Simple Body-Driven Current Mirror Cascode Body-Driven Current Mirror                                                                                                                                                                         | 65<br>69<br>70<br>70<br>70<br>72<br>72             |

| 3.2        | SIMP<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>REGU                   | ROR FOR LOW-VOLTAGE APPLICATIONS ODUCTION USING LEVEL-SHIFTING TECHNIQUE LE AND CASCODE BODY-DRIVEN CURRENT MIRROR Simple Body-Driven Current Mirror Improved Simple Body-Driven Current Mirror Cascode Body-Driven Current Mirror Improved Cascode Body-Driven Current Mirror ULATED BODY DRIVEN CMOS CURRENT MIRROR                                                                                      | 65<br>69<br>70<br>70<br>72<br>72<br>74             |

| 3.2        | SIMP<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>REGU<br>3.4.1          | ROR FOR LOW-VOLTAGE APPLICATIONS ODUCTION USING LEVEL-SHIFTING TECHNIQUE LE AND CASCODE BODY-DRIVEN CURRENT MIRROR Simple Body-Driven Current Mirror Improved Simple Body-Driven Current Mirror Cascode Body-Driven Current Mirror Improved Cascode Body-Driven Current Mirror ULATED BODY DRIVEN CMOS CURRENT MIRROR Input and Output Voltage Characteristics                                             | 65<br>69<br>70<br>70<br>72<br>72<br>74<br>75       |

| 3.2        | SIMP<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>REGU<br>3.4.1<br>3.4.2 | ROR FOR LOW-VOLTAGE APPLICATIONS ODUCTION USING LEVEL-SHIFTING TECHNIQUE LE AND CASCODE BODY-DRIVEN CURRENT MIRROR Simple Body-Driven Current Mirror Improved Simple Body-Driven Current Mirror Cascode Body-Driven Current Mirror Improved Cascode Body-Driven Current Mirror ULATED BODY DRIVEN CMOS CURRENT MIRROR Input and Output Voltage Characteristics Input and Output Resistance Characteristics | 65<br>69<br>70<br>70<br>72<br>72<br>74<br>75<br>77 |

|             | 3.4.6 | Simulation Results                           | 93           |

|-------------|-------|----------------------------------------------|--------------|

|             | 3.4.7 | Experimental Results                         | 98           |

| 3.5         | CON   | CLUSION                                      | 99           |

| 3. <i>A</i> | APPE  | ENDIX: SETTLING ANALYSIS                     | 100          |

|             | 3.A.1 | Scenario 1                                   | 100          |

|             | 3.A.2 | Scenario 2                                   | 101          |

|             | 3.A.3 | Scenario 3                                   | 101          |

| Chap        | ter 4 | DESIGN OF A 1.8 V CMOS LINEAR OTA AND IT     | $\mathbf{S}$ |

|             |       | APPLICATION TO CONTINUOUS-TIME FILTERS       | 102          |

| 4.1         | INTR  | ODUCTION                                     | 102          |

| 4.2         | FUNI  | DAMENTALS OF OTA-C FILTERS                   | 104          |

| 4.3         | THE   | EXISTING OTA LINEARIZATION TECHNIQUES        | 110          |

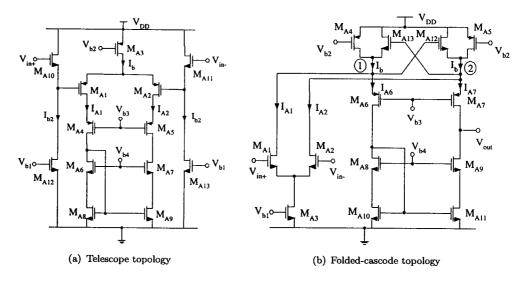

|             | 4.3.1 | Saturation-Based Transconductors             | 110          |

|             | 4.3.2 | Triode-Based Transconductors                 | 117          |

| 4.4         | PRIN  | CIPLE OF THE PROPOSED OTA AND DESIGN CONSID- |              |

|             | ERAT  | TONS                                         | 125          |

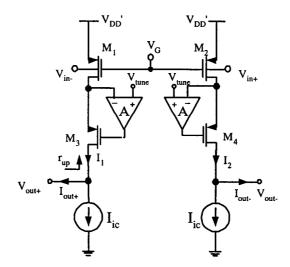

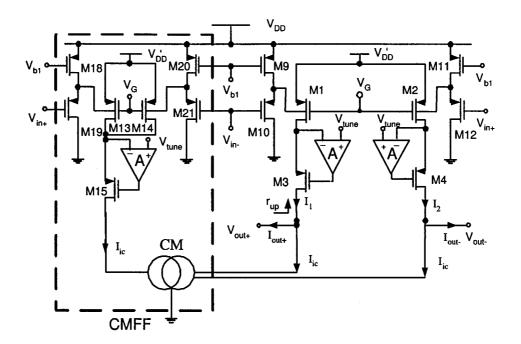

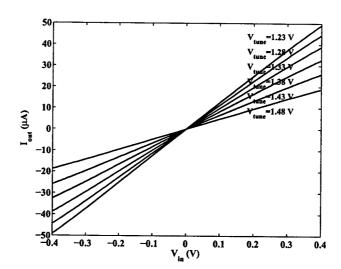

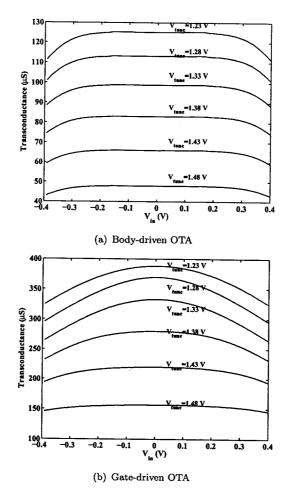

|             | 4.4.1 | The Proposed OTA Core                        | 125          |

|             | 4.4.2 | Nonlinearity Analysis                        | 127          |

|             | 4.4.3 | Input and Tuning Range                       | 128          |

|             | 4.4.4 | Frequency Analysis                           | 129          |

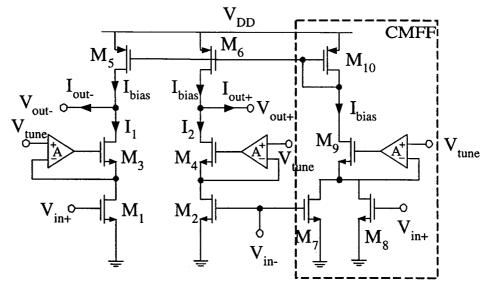

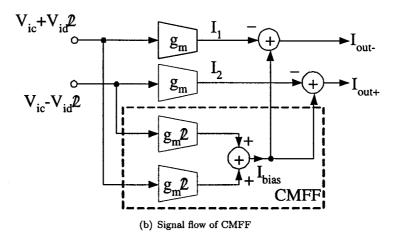

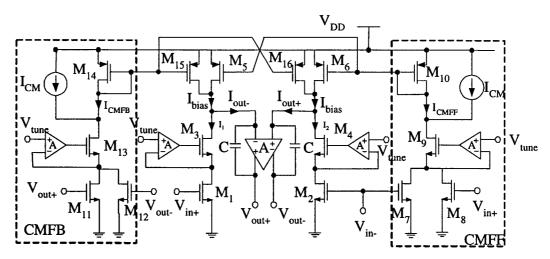

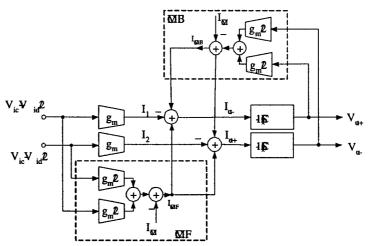

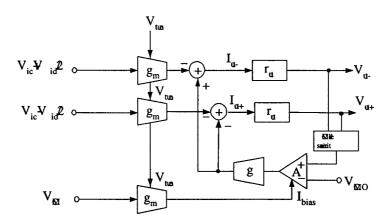

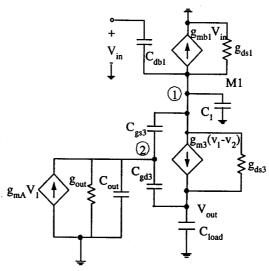

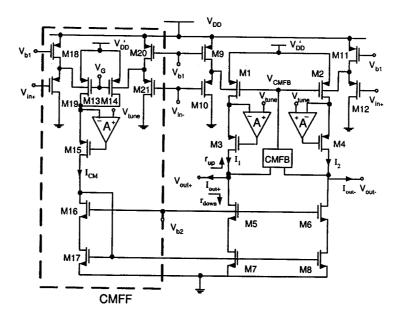

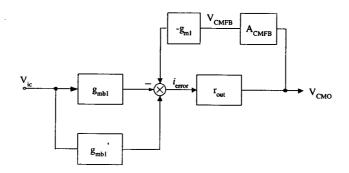

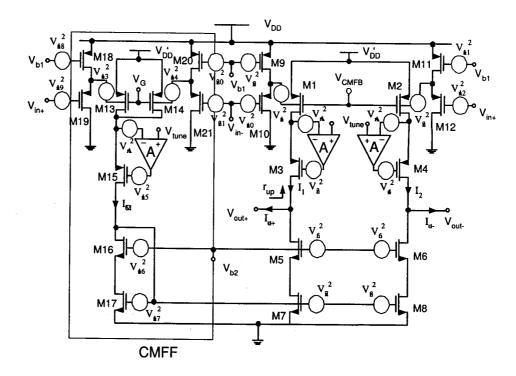

|             | 4.4.5 | Common-Mode Feedforward Design               | 133          |

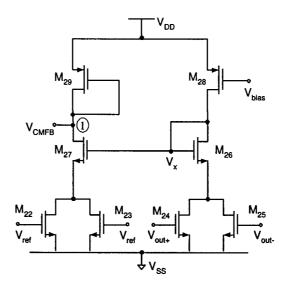

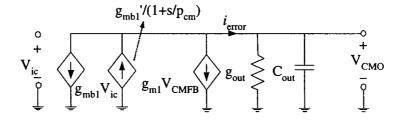

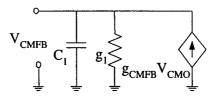

|             | 4.4.6 | Common-Mode Feedback Design                  | 135          |

|             | 4.4.7 | Noise Analysis                               | 140          |

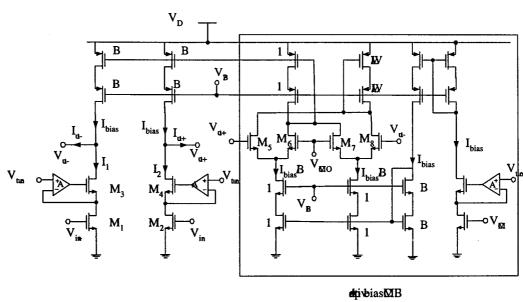

|             | 4.4.8 | Regulate Amplifier Design                    | 142          |

| 4.5         | SIMUI | LATION RESULTS OF THE PROPOSED OTA           | 147          |

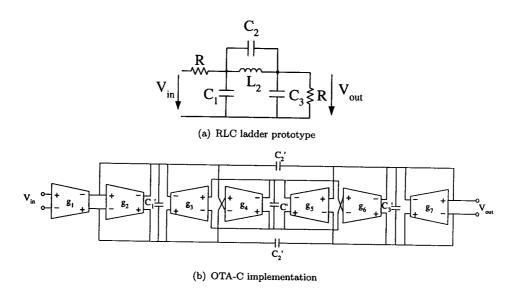

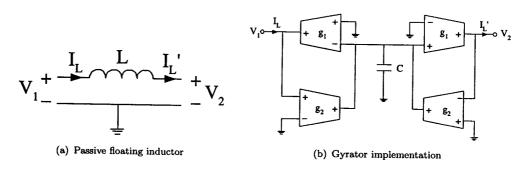

| 4.6         | OTA-C | C FILTER DESIGN                              | 151          |

| 17          | CONO  | IT TICTON                                    |              |

| Chapte  | er 5 CONCLUSION AND FUTURE WORK           | 156 |

|---------|-------------------------------------------|-----|

| 5.1     | SUMMARY                                   | 156 |

| 5.2     | THE ORIGINAL CONTRIBUTIONS OF THIS THESIS | 159 |

| 5.3     | FUTURE WORK                               | 161 |

| Bibliog | craphy                                    | 162 |

|         | or√                                       | 102 |

### List of Tables

| Table 1.1 | Performance comparison of BD and GD MOSFETs                 | 6   |

|-----------|-------------------------------------------------------------|-----|

| Table 1.2 | Comparison of self-cascode and conv. cascode topologies     | 12  |

| Table 1.3 | Parasitic capacitance of SOI MOSFET [1]                     | 18  |

| Table 2.1 | MOSFET scaling schemes                                      | 46  |

| Table 2.2 | CMOS scaling factors                                        | 47  |

| Table 2.3 | Scaling factors of MOSFET parameters                        | 64  |

| Table 3.1 | Performance comparison of simple, cascode, Wilson and high- |     |

|           | swing CMs                                                   | 68  |

| Table 3.2 | MOSFET Dimensions                                           | 93  |

| Table 4.1 | MOSFET dimensions of the CMFB block                         | 140 |

| Table 4.2 | MOSFET dimensions of the regulate amplifier                 | 147 |

| Table 4.3 | MOSFET dimensions of the OTA                                | 148 |

| Table 4.4 | Component values of the filter                              | 153 |

| Table 4.5 | Characteristics of $3^{rd}$ order elliptic LPF              | 154 |

## List of Figures

| Figure 1.1  | Cross section of a PMOS in N-well technology                                              | 3  |

|-------------|-------------------------------------------------------------------------------------------|----|

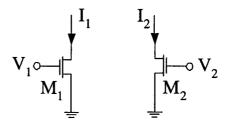

| Figure 1.2  | BD and GD MOSFETs                                                                         | 5  |

| Figure 1.3  | DC performance of BD and GD MOSFETs                                                       | 5  |

| Figure 1.4  | Cross section of a FG MOSFET in double-ploy process                                       | 8  |

| Figure 1.5  | Two-input FG MOSFET                                                                       | 8  |

| Figure 1.6  | MIFG building blocks                                                                      | 10 |

| Figure 1.7  | Self-cascode MOSFET                                                                       | 11 |

| Figure 1.8  | Modified simple CM with level shifting technique                                          | 13 |

| Figure 1.9  | Complementary differential pair input stage                                               | 14 |

| Figure 1.10 | Concept of dynamic level shifting [2]                                                     | 15 |

| Figure 1.11 | SOI DTMOS [1]                                                                             | 17 |

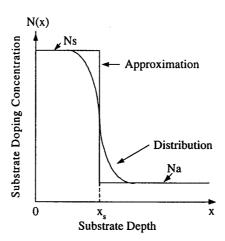

| Figure 2.1  | Substrate doping concentration and its approximation [3]                                  | 24 |

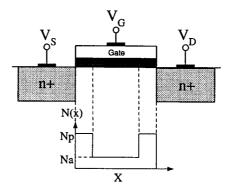

| Figure 2.2  | Schematic depicting non-uniform lateral doping profile                                    | 26 |

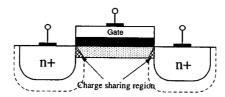

| Figure 2.3  | Schematic depicting charge sharing effect in short-channel device. $ \\$                  | 27 |

| Figure 2.4  | Schematic depicting DIBL effect                                                           | 27 |

| Figure 2.5  | Schematic depicting fringing effect of STI MOSFET                                         | 28 |

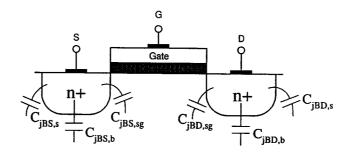

| Figure 2.6  | Schematic of parasitic junction capacitances modeled in BSIM3V3.                          | 30 |

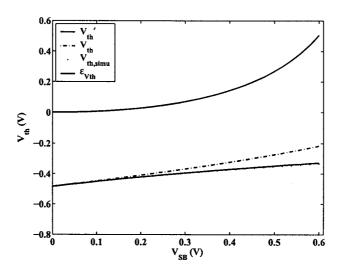

| Figure 2.7  | Comparison of calculated and simulated threshold voltages                                 | 34 |

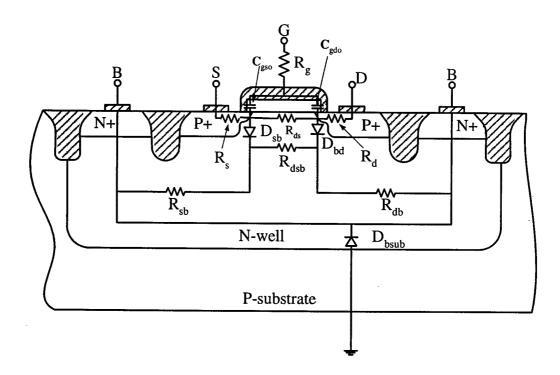

| Figure 2.8  | Comparison of calculated and simulated body-source junction                               |    |

|             | capacitance, $W/L=0.5\mu\mathrm{m}/0.18\mu\mathrm{m},$ $CJ=0.001121\mathrm{F/m^2},$ $MJ=$ |    |

|             | $0.4476,\ PB\ =\ 0.895226\ {\rm V},\ CJSW\ =\ 2.481\ \times\ 10^{-10}\ {\rm F/m},$        |    |

|             | $MJSW = 0.3683619, \ MJSWG = 0.3683619, \ CJSWG =$                                        |    |

|             | $4.221 \times 10^{-10}$ F/m, $PBSW = 0.895226$ V, and $PBSWG =$                           |    |

|             | 0.895226 V                                                                                | 35 |

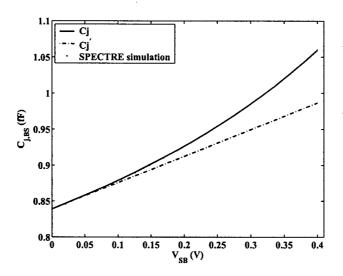

| Figure 2.9  | Cross section of PMOS in N-well                                                           | 38 |

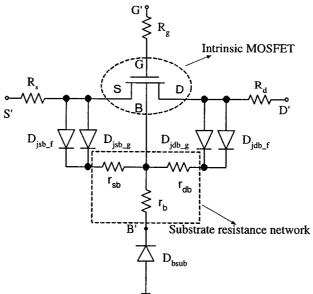

| Figure 2.10 | Suggested model for BD MOSFET                                           | 39 |  |

|-------------|-------------------------------------------------------------------------|----|--|

|             |                                                                         |    |  |

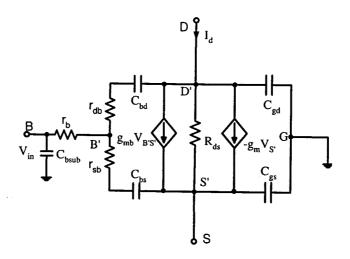

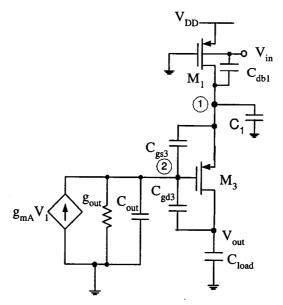

|             | Small signal model of the BD MOSFET                                     | 40 |  |

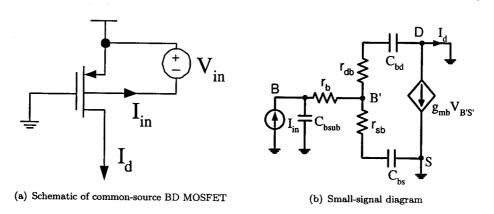

| Figure 2.12 | Common-source BD MOSFET                                                 | 40 |  |

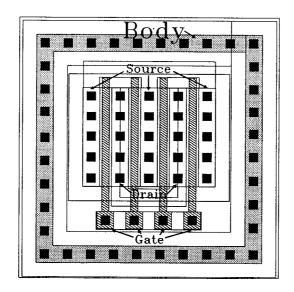

| Figure 2.13 | Layout of 4-finger PMOS with $W/L=10~\mu\mathrm{m}/0.18~\mu\mathrm{m}.$ | 42 |  |

| Figure 2.14 | Cross view of a N-type MOSFET formed on buried P-well (sur-             |    |  |

|             | rounded by deep N-well structure)                                       | 44 |  |

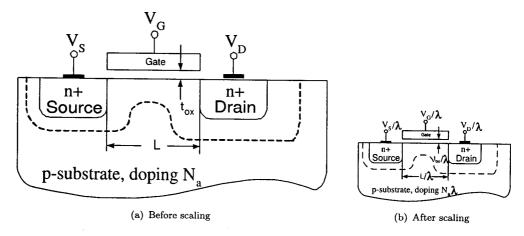

| Figure 2.15 | Principle of MOSFET constant-electric-field scaling                     | 45 |  |

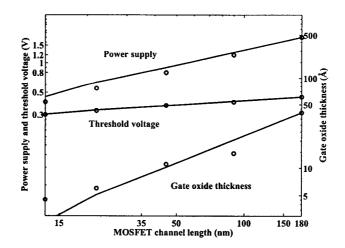

| Figure 2.16 | Scaling trends of power supply voltage, threshold voltage, and          |    |  |

|             | gate oxide thickness versus channel lengths for CMOS technolo-          |    |  |

|             | gies                                                                    | 48 |  |

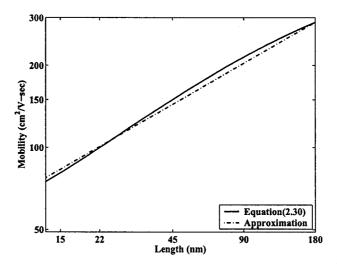

| Figure 2.17 | Scaling trends of MOSFET mobility                                       | 49 |  |

| Figure 2.18 | Drain currents of BD and GD MOSFETs in saturation region.               | 52 |  |

| Figure 2.19 | Drain current versus $V_{BS}$ for BD MOSFET in linear region            | 53 |  |

| Figure 2.20 | Transconductance ratio between BD and GD MOSFETs $(g_{mb}/g_m)$ .       |    |  |

| Figure 2.21 | Transconductances of BD and GD MOSFETs                                  | 55 |  |

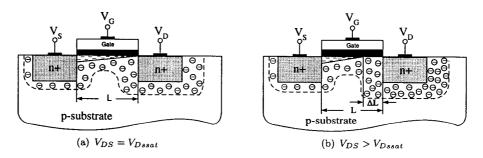

| Figure 2.22 | Diagram of channel length modulation effect                             | 57 |  |

| Figure 2.23 | Scaling of the output conductance for MOSFETs operating in              |    |  |

|             | saturation region                                                       | 59 |  |

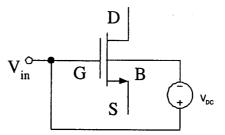

| Figure 2.24 | Schematic diagram of dynamic-threshold MOSFET                           | 61 |  |

| Figure 2.25 | Input-referred noise of BD, GD and dynamic threshold MOS-               |    |  |

|             | FETs                                                                    | 62 |  |

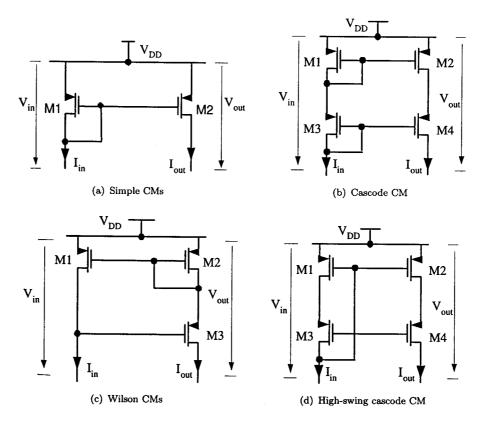

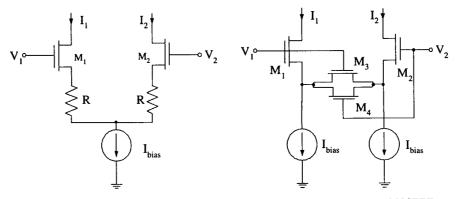

| Figure 3.1  | Conventional CMs                                                        | 66 |  |

| Figure 3.2  | Triode-region CM with level shifting technique                          | 68 |  |

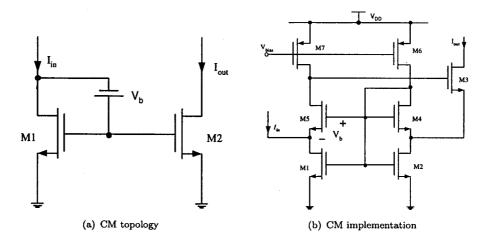

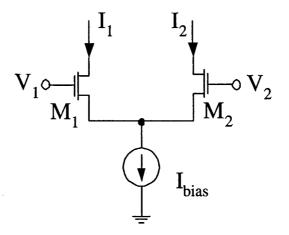

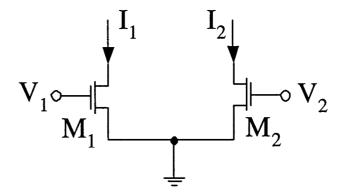

| Figure 3.3  | BD CM                                                                   | 69 |  |

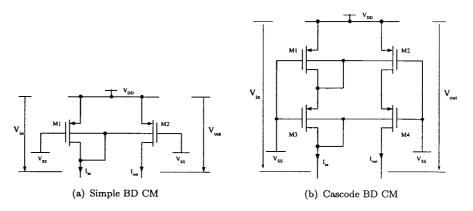

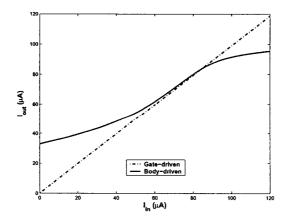

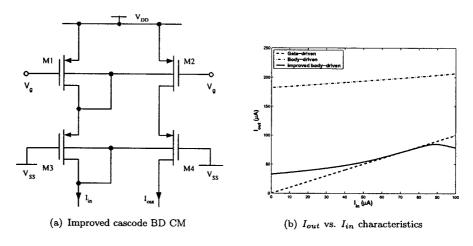

| Figure 3.4  | $I_{out}$ vs. $I_{in}$ of simple BD CM                                  | 71 |  |

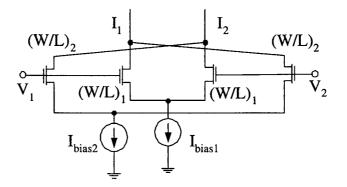

| Figure 3.5  | Cascode BD CM                                                           |    |  |

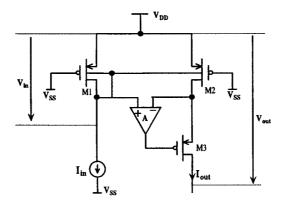

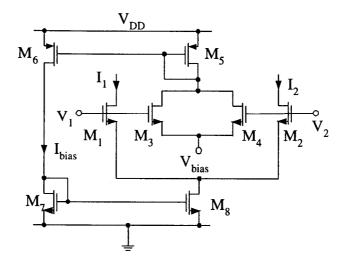

| Figure 3.6  | Topology of the proposed RDCM                                           | 71 |  |

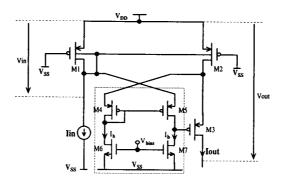

| Figure 3.7  | Detailed schematic of the proposed BDCM                                                                |     |  |

|-------------|--------------------------------------------------------------------------------------------------------|-----|--|

| Figure 3.8  | Comparison of analytical and simulated current transfer accu-                                          |     |  |

|             | racy $\varepsilon\%$ versus $I_{in}$ , for $V_{DD}=1.5$ V, $V_{SS}=0$ V, $ V_{th} =0.47$               |     |  |

|             | V, $I_b = 12 \mu A$ , $\beta = 1.1 \text{ mA/V}^2$ , $\beta_4 = 1.17 \text{ mA/V}^2$ , $\beta_3 = 7.6$ |     |  |

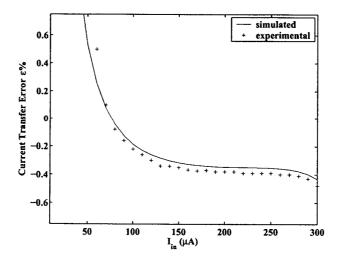

|             | mA/V², $\lambda_4=0.088$ V <sup>-1</sup> and $\lambda_6=0.02$ V <sup>-1</sup>                          | 83  |  |

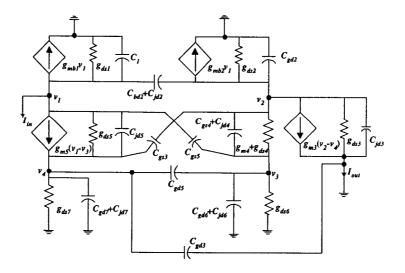

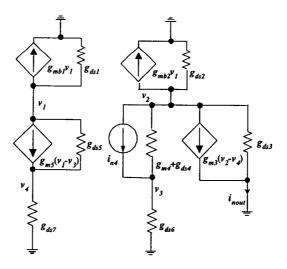

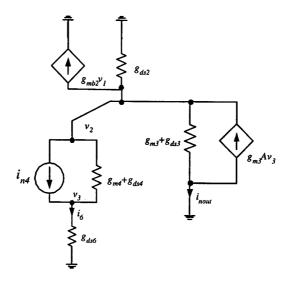

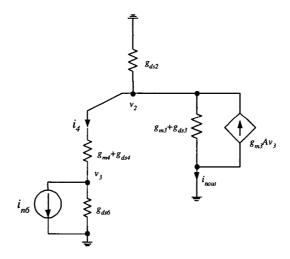

| Figure 3.9  | Small-signal model for the proposed BDCM                                                               | 84  |  |

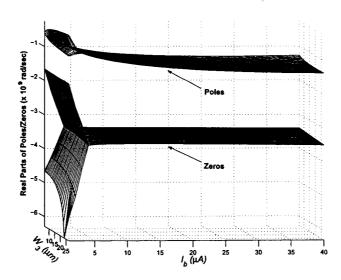

| Figure 3.10 | Real parts of dominant poles and zeros versus $I_b$ and $W_3$                                          | 87  |  |

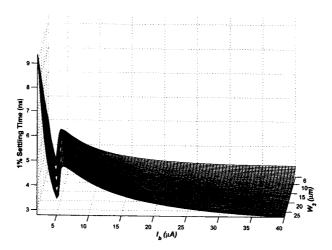

| Figure 3.11 | 1% step response settling time versus $I_b$ and $W_3$                                                  | 88  |  |

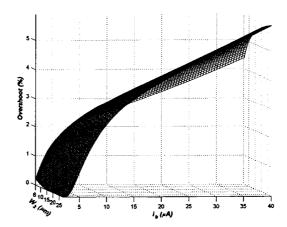

| Figure 3.12 | Overshoot versus $I_b$ and $W_3$                                                                       | 89  |  |

| Figure 3.13 | Small-signal diagram for calculating $i_{nout}/i_{n4}$                                                 | 90  |  |

| Figure 3.14 | Simplified small-signal diagram for calculating $i_{nout}/i_{n4}.$                                     | 90  |  |

| Figure 3.15 | Simplified small-signal diagram for calculating $i_{nout}/i_{n6}$                                      | 92  |  |

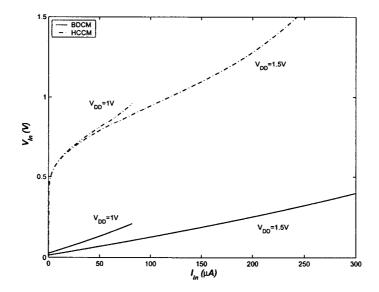

| Figure 3.16 | $V_{in}$ versus $I_{in}$ characteristics                                                               | 94  |  |

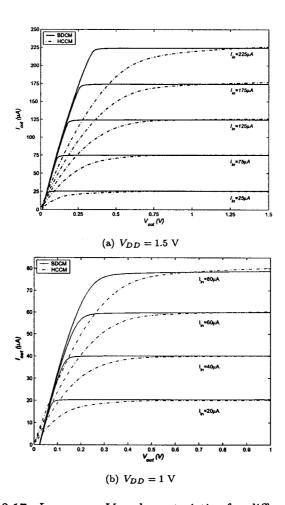

| Figure 3.17 | $I_{out}$ versus $V_{out}$ characteristics for different $I_{in}$                                      | 95  |  |

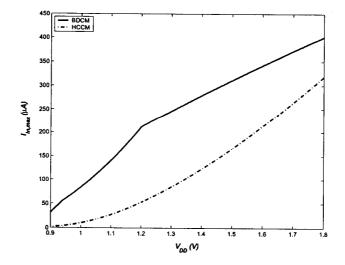

| Figure 3.18 | $I_{in,max}$ versus $V_{DD}$                                                                           | 96  |  |

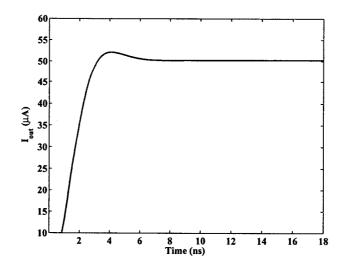

| Figure 3.19 | Step response of the proposed BDCM                                                                     | 97  |  |

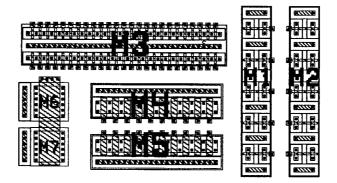

| Figure 3.20 | Layout floor plan of the BDCM                                                                          | 97  |  |

| Figure 3.21 | Current transfer error vs. $I_{in}$                                                                    | 98  |  |

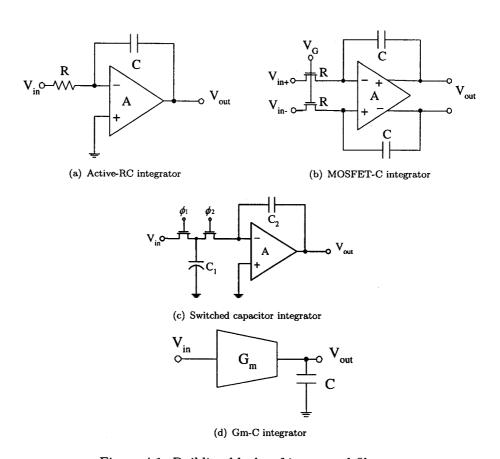

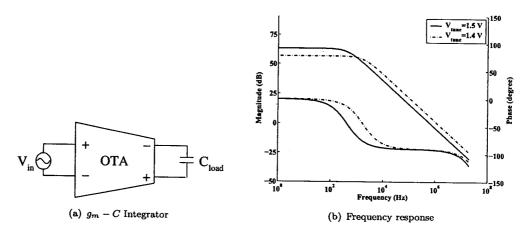

| Figure 4.1  | Building blocks of integrated filters                                                                  | 102 |  |

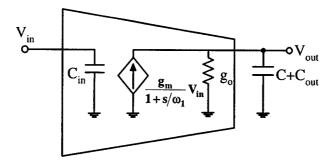

| Figure 4.2  | Non-ideal OTA-C integrator                                                                             | 105 |  |

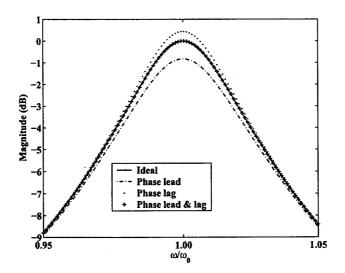

| Figure 4.3  | Frequency responses of ideal and nonideal OTA-C integrator                                             | 106 |  |

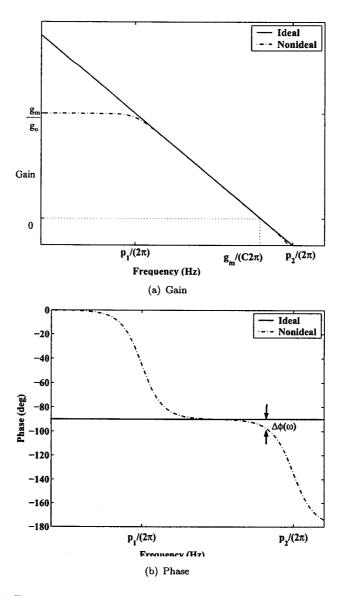

| Figure 4.4  | OTA-C biquadratic bandpass filter                                                                      | 108 |  |

| Figure 4.5  | Non-ideal effects on the filter performance                                                            | 109 |  |

| Figure 4.6  | Conventional simple differential OTA                                                                   | 110 |  |

| Figure 4.7  | Cross-coupled differential OTA                                                                         | 112 |  |

| Figure 4.8  | Grounded common-source differential OTA                                                                | 112 |  |

| Figure 4.9  | Degenerated differential OTA                                                                           | 114 |  |

| Figure 4.10 | Adaptive biasing differential OTA                                                                   | 116  |  |

|-------------|-----------------------------------------------------------------------------------------------------|------|--|

| Figure 4.11 | Triode-based differential OTA                                                                       | 117  |  |

| Figure 4.12 | Pseudo differential OTA                                                                             | 118  |  |

| Figure 4.13 | Pseudo differential OTA with CMFF                                                                   | 120  |  |

| Figure 4.14 | Pseudo differential OTA with CMFF and CMFB                                                          | 122  |  |

| Figure 4.15 | Pseudo-differential OTA with adaptive bias CMFB                                                     | 124  |  |

| Figure 4.16 | Diagram of the proposed differential transconductor core                                            | 126  |  |

| Figure 4.17 | Tuning range vs. input range of conv. and proposed triode-                                          |      |  |

|             | based OTAs                                                                                          | 129  |  |

| Figure 4.18 | Small-signal half-circuit of the proposed differential transcon-                                    |      |  |

|             | ${\bf ductor.} \ \ldots \ $ | 131  |  |

| Figure 4.19 | Proposed OTA core with CMFF                                                                         | 134  |  |

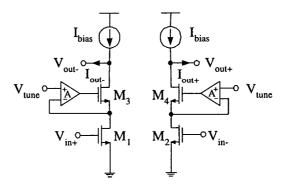

| Figure 4.20 | Schematic of the triode-based CMFB                                                                  | 135  |  |

| Figure 4.21 | Schematic of the proposed differential transconductor 136                                           |      |  |

| Figure 4.22 | CMFB signal flow diagram                                                                            |      |  |

| Figure 4.23 | The small-signal model of the CMFB scheme                                                           | 139  |  |

| Figure 4.24 | The proposed OTA schematic to evaluate the noise performance                                        | .141 |  |

| Figure 4.25 | Schematics of regulate amplifier topologies                                                         | 143  |  |

| Figure 4.26 | V-I transfer characteristic of the proposed OTA                                                     | 148  |  |

| Figure 4.27 | OTA transconductance vs. $V_{in}$ for different $V_{tune}$                                          | 149  |  |

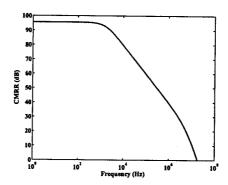

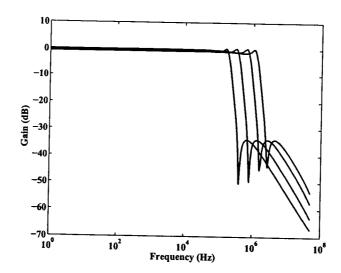

| Figure 4.28 | Frequency response of the $g_m-C$ integrator with $C_{load}=5~p{\rm F}.$                            | 150  |  |

| Figure 4.29 | Frequency response of CMRR for the proposed OTA                                                     | 150  |  |

| Figure 4.30 | Third-order low-pass elliptic filter                                                                | 152  |  |

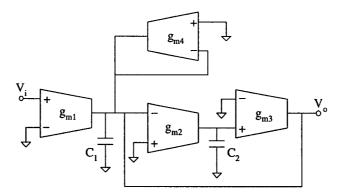

| Figure 4.31 | Gyrator implementation of floating inductor                                                         | 152  |  |

| Figure 4.32 | Frequency response of the $3^{rd}$ order elliptic LPF                                               | 154  |  |

## Acknowledgments

I would like to express sincere gratitude to my doctoral advisor Dr. El-Masry for his guidance, collaboration and support in my research. Dr. El-Masry's strong confidence in me and constant encouragement boost my enthusiasm in this research. It is this passion as well as the sufficient intellectual freedom to pursue my own ideas that make the whole doctoral studies an interesting and rewarding period of my life. Dr. El-Masry's expertise and knowledge in this field are extremely helpful and valuable for my research. Furthermore, the VLSI Research Lab led by Dr. El-Masry has well-organized infrastructure and facilities that is an asset for me to smoothly carry out the research work.

I am fortunate to have Dr. William J. Phillips and Dr. Jacek Ilow as my two guiding committee members, who equipped me with solid research background in Engineering Mathematics, Signal Processing and Communication Systems.

I would like to express my appreciation to all my colleagues for their thoughtful discussions and comments they provided. Special thanks is expressed to the Systems Administrator Mark LeBlanc and Senior Electronic Technologist Christopher Hill for their help in maintaining and upgrading the workstations & Cadence softwares.

I would like to acknowledge the Killam Scholarship Committee for providing me the Izaak Walton Killam Predoctoral Scholarship. I would also thank the support in part by the Natural Sciences and Engineering Research Council of Canada (NSERC), and the Canadian Network of Centres of Excellence in Microelectronics (MICRONET). My gratitude also goes to Canadian Microelectronics Corporation (CMC) and Taiwan Semiconductor Manufacturing Company Ltd. (TSMC) for their fabrication services.

Last but not the least, the author wishes to express special gratitude to my parents, Baohua Zhang, Huimin Lu and my brother Xudong Zhang for their support, their encouragement for pursuing this career, and their inspiration throughout these years.

## **Abstract**

Modern low-voltage (LV) submicron CMOS technologies with large second or higher order effects put great challenge in designing high performance analog building blocks for increasingly popularized portable battery-powered applications. Bodydriven (BD) MOSFET is equivalent to a depletion type device and compatible with standard CMOS technology. Although BD technique has great potential to achieve LV operation, few practical BD circuits have been proposed due to two reasons: 1) BD technique is a new research area; 2) MOSFET models are optimized for conventional gate-driven (GD) MOSFETs. Their accuracy in simulating BD MOSFET has not been investigated. So far, no research has been carried out on BD MOSFET modeling. The objective of this Ph.D. work is to exploit the potentials of the BD technique by 1) carrying out a comprehensive study on the industry-standard model's performance in simulating body-driven MOSFET; 2) presenting solutions and an improved model for BD MOSFET that improve the simulation accuracy; 3) predicting the future prospects of the body-driven device performance; 4) proposing and implementing novel high performance BD analog signal processing building blocks for LV operation. Specifically, a novel 1 V/1.5 V regulated current mirror (CM) is developed based on BD technique and active feedback scheme. An optimum design methodology is formulated based on the complete analysis of the input/output characteristics, system DC current transfer error and pole/zero locations. A 1.8 V differential BD operational transconductance amplifier (OTA) is also presented that achieves enhanced linearity as well as relieves the conventional trade-off between the input range and tuning range. Detailed analysis addressing the design concerns is provided. Finally, a 3<sup>rd</sup> order elliptic low-pass filter is implemented by using the proposed OTA and synthesized from a doubly terminated passive LC ladder. It features high linearity, wide signal swing and tuning range, as well as good dynamic range.

#### Chapter 1

#### INTRODUCTION

The motivation and objective of the research described in this thesis are discussed in this chapter.

#### 1.1 LOW-VOLTAGE DESIGN STRATEGIES

Fast growing broadband wireless and wireline system industry demands smaller, faster, cheaper, low power (LP), low voltage single chip implementations (SoC). This results in the fast scaling of CMOS VLSI technologies and power supply voltages. According to the International Technology Roadmap for Semiconductors (ITRS) [4], the power supply is expected to be as low as 0.3 V with device sizes below 13nm by the year of 2016. Digital CMOS circuits definitely benefit greatly from the scaling with respect to higher integration levels, faster operation speed, as well as decreased power consumption ( $\propto V_{DD}^2$ ). Unfortunately, high performance analog circuits become increasingly difficult to implement with the scaling trend mainly due to the following reasons:

• Threshold voltage cannot be scaled proportionally with the power supply voltage from the point of view of leakage current and standby power. The leakage current for a MOSFET can be written as

$$I_{leak} = WI_s e^{-V_{th}/V_o} (1.1)$$

where

W =the effective transistor width of the MOSFET,

$I_s$  = the zero-threshold leakage current,

$V_{th}$  = the threshold voltage,

$V_o$  = the subthreshold slope.

The influence of drain voltage and reverse biased diodes on the leakage current is ignored. Equation 1.1 reveals that the leakage current increases with the reduction of  $V_{th}$  at exponential scale. Such subthreshold behavior originates directly from fundamental thermodynamics and is independent of power supply voltage and channel length. Hence, in order to prevent this drastic leakage current increase, the threshold voltage  $(V_{th})$  should not be scaled down with the same rate as the maximum allowable power supply voltage. This directly results in the decrease of signal headroom. Since the noise floor stays at a relatively constant level, the circuit dynamic range is degraded as well.

- MOSFET scaling leads to severe Channel Length Modulation (CLM) effect. Seeing from the device level point of view, CLM effect reduces the MOSFET output resistance  $r_{ds}$  and the intrinsic small signal gain that is given by  $g_m r_{ds}$ , where  $g_m$  is the small signal transconductance of the MOSFET. In analog circuit design, smaller MOSFET gain leads to less settling accuracy in feedback topologies and worse linearity. Traditionally, cascode topology featured with "stacked" devices is widely used to compensate the above performance loss. Every "stacked" device enhances the circuit output impedance by a factor of  $g_m r_{ds}$ . However, the number of "stacked" devices is strictly limited by the voltage headroom required for each device in low-voltage applications.

- MOSFET scaling results in higher minimum-size MOSFET mismatch that is

extremely important in affecting the performance of many analog circuits, such

as differential pairs, CMs, Analog to Digital (A/D) and Digital to Analog (D/A)

converters.

Due to the above difficulties, LV analog IC components become the major and challenging bottleneck in CMOS SoC design. An adaptation of alternative CMOS design techniques to suit the low voltage environments have been reported, such as subthreshold operation [5], BD technique [6–13], floating gate technique [11–14], and self-cascode technique [11–13,15].

#### 1.1.1 Body-Driven Technique

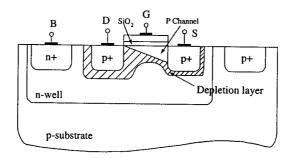

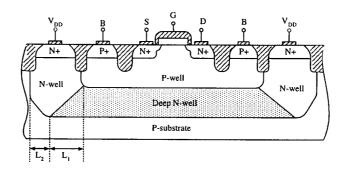

Figure 1.1: Cross section of a PMOS in N-well technology.

The cross section of a PMOS structure in N-well is illustrated in Figure 1.1. For a conventional MOSFET, gate-source voltage  $V_{GS}$  is used to control the conductivity of the channel, hence the drain current. The influence of bulk-source voltage  $V_{BS}$  on  $I_{SD}$  (shown in Equation 1.2) is considered as a parasitic effect, i.e., body effect.

$$I_{SD} = \begin{cases} \frac{1}{2} \mu C_{ox} \frac{W}{L} \left( V_{SG} - |V_{th}| \right)^2 & V_{SD} \ge V_{SG} - |V_{th}| \\ \mu C_{ox} \frac{W}{L} \left( V_{SG} - |V_{th}| - \frac{1}{2} V_{SD} \right) V_{SD} & V_{SD} < V_{SG} - |V_{th}| \end{cases}$$

(1.2)

where

W/L = MOSFET aspect ratio,

$\mu = \text{mobility of the carriers},$

$C_{ox} = \text{gate oxide capacitance per unit area},$

$$|V_{th}| = |V_{th0}| + \gamma \sqrt{2|\phi_F| + V_{BS}} - \gamma \sqrt{2|\phi_F|},$$

$\gamma = \text{body effect coefficient},$

$|V_{th0}|$  = value of  $|V_{th}|$  at zero substrate bias  $V_{BS} = 0$ ,

$|\phi_F|$  = absolute body Fermi potential whose typical value for a substrate doping of  $4 \times 10^{17}$  cm<sup>-3</sup> is 0.44 V.

Except from the quantitative expression, it is important to give a qualitative description of the body effect from the physics point of view. For a PMOS with zero body bias (i.e.,  $V_{SB} = 0$ ), it is known that inversion layer forms when the source-gate voltage is sufficiently high. In this case, negative charges are placed on the gate, while positive charges/holes are contained in depletion region. Assume that  $V_{SG}$  is large enough to cause strong inversion. The inversion layer with abundant holes and the lightly doped substrate form a field-induced pn junction. This junction behaves similarly as the regular pn junction and  $V_{BS}$  is equivalent to the reverse bias of the pn junction. Increasing  $V_{BS}$  widens the depletion region under the strongly inverted surface. If  $V_{SG}$  is kept constant, the total positive charges under the oxide remain constant. However, since the increased depletion width contributes more positive charges, fewer holes are actually needed in the inversion level. Thus, the level of inversion decreases. Therefore, the induced channel current drops.

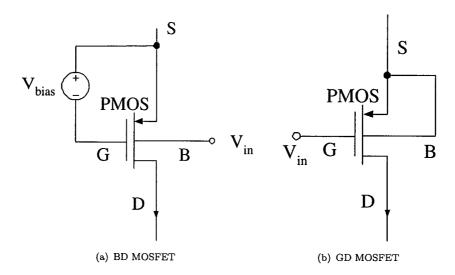

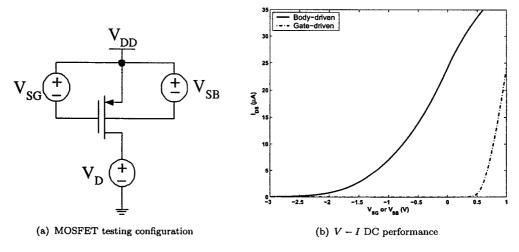

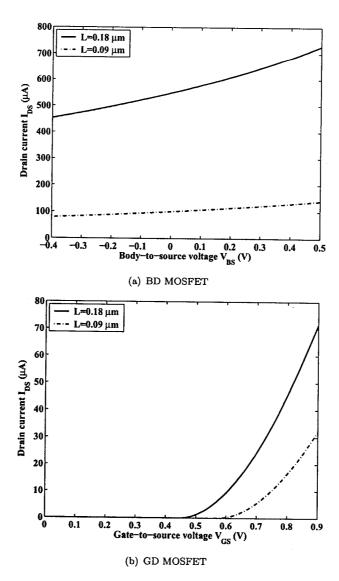

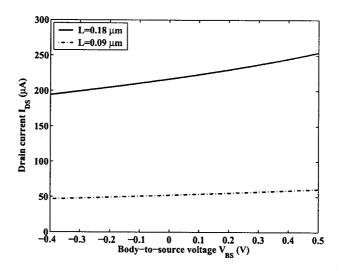

For a BD MOSFET, the body-effect is utilized as the major factor to change the channel conductivity. This is done by applying the input voltage to the body terminal, while biasing the source-gate voltage to be a constant value that is large enough to always turn on the MOSFET, as shown in Figure 1.2(a). Figure 1.3 shows the DC performance of the BD MOSFET and conventional GD MOSFET.  $V_{DD}$  equals to 1 V. The aspect ratio of the PMOS is chosen as  $W/L = 0.5 \,\mu\text{m}/0.18 \,\mu\text{m}$ . Body terminal is tied to its source for GD PMOS, while source-gate voltage is biased to be 1 V for BD PMOS.  $V_D$  is set to be 0.5 V. As clearly illustrated in Figure 1.3, BD MOSFET operates similarly as a JFET. This depletion characteristic removes the requirement of turn-on threshold voltage  $V_{th}$ . Hence, BD circuits can easily achieve high signal swing

Figure 1.2: BD and GD MOSFETs.

Figure 1.3: DC performance of BD and GD MOSFETs.

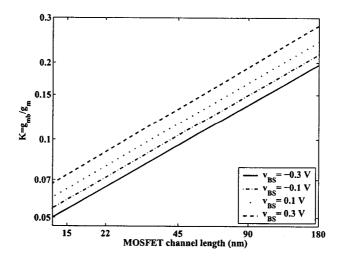

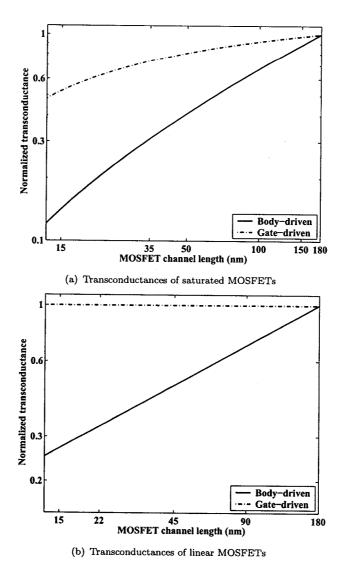

with low power supply voltages. Assuming MOSFETs operate at saturation region, the comparison of BD and GD MOSFETs is summarized in Table 1.1 [10]. MOSFET characteristics including transconductance, transition frequency, and power spectral density of the input-referred noise are considered, where

Table 1.1: Performance comparison of BD and GD MOSFETs

| MOSFET           | BD                                                                                      |  |

|------------------|-----------------------------------------------------------------------------------------|--|

| Transconductance | $g_{mb}$                                                                                |  |

| $ m f_{T}$       | $g_{mb}/\left(2\pi(C_{bs}+C_{bsub}+C_{bd})\right)$                                      |  |

| Noise            | $\frac{8kT(1+K)}{3K^2g_m} + \frac{KF}{K^2f^{AF}C_{ox}^2WL} + 4kT$                       |  |

|                  | $\left(\frac{1}{N}\right)^2 \left(\sum_{i=1}^N R_{gi}/K^2 + \sum_{i=1}^N R_{bi}\right)$ |  |

| MOSFET           | GD                                                                                      |  |

| Transconductance | $g_m$                                                                                   |  |

| $\mathbf{f_T}$   | $g_m/\left(2\pi(C_{gs}+C_{gd})\right)$                                                  |  |

| Noise            | $\frac{8kT(1+K)}{3g_m} + \frac{KF}{f^{AF}C_{ox}^2WL} + 4kT$                             |  |

|                  | $\left(\frac{1}{N}\right)^2 \left(\sum_{i=1}^N R_{gi} + K^2 \sum_{i=1}^N R_{bi}\right)$ |  |

$g_{mb} = \text{body transconductance},$

$C_{bs} = \text{body-source capacitance},$

$C_{bsub} = \text{body-substrate capacitance},$

$C_{qs}$  = gate-source capacitance,

$K = g_{mb}/g_m$

N = number of fingers for an interdigitated MOSFET structure,

KF = flicker noise empirical parameter that depends on fabrication process,

AF = exponential parameter with variation between 0.7 and 1.2,

$R_{bi}$  = effective series bulk resistance for the ith gate finger,

$R_{gi}$  = effective series gate-metal resistance of the ith gate finger,

Although BD circuit is especially appealing for low voltage applications, it has disadvantages:  $g_{mb}$  is typically smaller than  $g_m$  by 0.2 to 0.4 times [10]. This property makes the BD MOSFET to have lower transition frequency and higher input referred

noise than conventional GD MOSFET.

As far as technology is concerned, only N(P) channel BD MOSFETs are available for single P(N)-well CMOS process conventionally. However, under the demand of the vast increasing mixed-signal system designs, standard CMOS processes with extra features have been developed nowadays which provide the possibility to build both types of BD MOSFETs on a single chip. For example, Taiwan Semiconductor Manufacturing Company Ltd. (TSMC) [16] offers standard N-well processes with deep N-well option for 0.25  $\mu m$  and smaller technologies. This option yields isolated P-wells. Thus, each N-channel MOSFET that requires individual body potential can be easily built in these isolated P-wells. IBM [17] also offers industry-standard 0.18  $\mu m$  (and smaller size) CMOS process that is twin-well technology as well as offers the option of isolated triple-well NMOS. Therefore, it is no longer a problem to have both BD NMOS and BD PMOS in state-of-art CMOS processes.

#### 1.1.2 Floating-Gate Technique

Since floating-gate (FG) devices were first proposed in 1967 [18], FG technique has been widely used in digital memory circuits such as erasable programmable read-only memory (EPROM), electronically erasable programmable read-only memory (EEPROM), and flash memory [19–21]. Completely surrounded by the silicon dioxide which provides excellent electric isolation, the floating gate can store data for long time. Therefore, the FG MOSFETs were primarily used as data storage devices originally. Only in the late 1980s, multiple-input floating-gate (MIFG) devices started to be utilized in analog circuits, such as analog memories [22,23], trimming circuits [24,25], low voltage operational amplifiers and filters [26–29]. FG devices normally require two poly layers: the control gate layer and the FG layer. Therefore, fabrication of FG devices may require nonstandard CMOS fabrication process: double-poly process, which is provided by limited silicon foundries such as austriamicrosystems (AMS) [30].

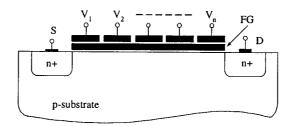

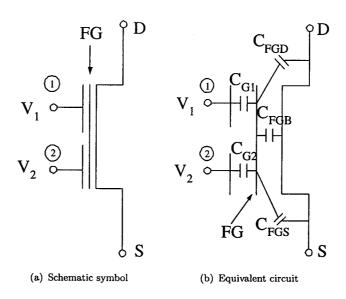

The cross section of a MIFG MOSFET is shown in Figure 1.4. Its operation principle

Figure 1.4: Cross section of a FG MOSFET in double-ploy process.

is to process signals by linearly summing a number of input voltages on the FG (via a capacitive voltage divider).

For simplicity but without losing generality, two-input FG MOSFET is shown in

Figure 1.5: Two-input FG MOSFET.

Figure 1.5. The FG voltage  $(V_{FG})$  can be expressed as

$$V_{FG} = \left(Q_{FG} + C_{FGD}V_D + C_{FGB}V_B + C_{FGS}V_S + \sum_{i=1}^{2} C_{Gi}V_i\right)/C_T$$

(1.3)

where

$Q_{FG}$  = the amount of charge stored on the FG,

$C_{FGD}$  = the coupling capacitance between the FG and the drain,

$C_{FGB}$  = the coupling capacitance between the FG and the body,

$C_{FGS}$  = the coupling capacitance between the FG and the source,

$C_{Gi}$  = the coupling capacitance between the FG and the ith control gate, i=1,2,

$$C_T = C_{G1} + C_{G2} + C_{FGD} + C_{FGB} + C_{FGS}.$$

For low voltage analog circuits, FG normally does not have static charge, i.e.,  $Q_{FG} = 0$ . Also,  $C_{Gi}$  is deliberately made to be much larger compared with other coupling capacitors, i.e.,  $C_{Gi} >> C_{FGD}, C_{FGB}, C_{FGS}$ . This can be readily attained through proper layout techniques [19,31]. If one input (node 2) is used as biasing terminal to reduce or even cancel the threshold voltage, the other terminal (node 1) is used as input terminal, the drain current in saturated FG device is expressed as

$$I_{DS} = \frac{1}{2} \frac{W}{L} \mu C_{ox} \frac{C_{G1}}{C_T} \left\{ V_1 - V_S - \left[ V_{th} + \frac{C_{G2}}{C_{G1}} \left( V_{th} - V_2 \right) \right] \right\}^2.$$

(1.4)

where  $C_T \approx C_1 + C_2$ . Thus, the effective threshold voltage  $V_{th,eff}$  seen by input terminal is

$$V_{th,eff} = V_{th} + \frac{C_{G2}}{C_{G1}} (V_{th} - V_2).$$

(1.5)

By properly selecting the bias voltage  $V_2$  and the coupling capacitors ( $C_{G2}$  and  $C_{G1}$ ),  $V_{th,eff}$  can be adjusted to be much lower than the threshold voltage of a MOS-FET. This makes FG a promising technique to overcome the threshold voltage limitation and achieve ultra-low voltage operation. However, the effective transconductance  $g_{m,eff}$  and output conductance  $g_{ds,eff}$  of the MIFG MOSFET are smaller than those of the traditional MOSFET due to the capacitive voltage divider effect and the capacitive coupling effect between the gate and the drain. Taking two-input FG MOSFET

for example,  $g_{m,eff}$  and  $g_{ds,eff}$  are expressed, respectively, as

$$g_{m,eff} \simeq \frac{C_{G1}}{C_T} g_m \tag{1.6}$$

$$g_{ds,eff} \simeq g_{ds} + \frac{C_{FGD}}{C_T} g_m \tag{1.7}$$

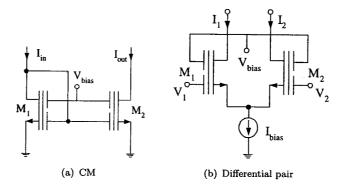

Therefore, the MIFG devices achieve low-voltage operation at the expense of degraded transconductance and the gain-bandwidth-product as well as increased silicon area. Basic MIFG analog building blocks such as simple CM and differential pair are shown in Figure 1.6.

It is worth mentioning that, for single-input FG device, the effective threshold volt-

Figure 1.6: MIFG building blocks.

age seen from the control gate can be adjusted by varying the amount of the static charge on the FG. Transferring electrons onto the FG increases the effective threshold voltage, while removing electrons from the FG decreases the threshold voltage. There are mainly three programming mechanisms to accomplish this task: ultra-violet light, hot-electron injection and Folwer-Nordheim tunneling. However, the additional programming circuits and high programming voltage limit the single-input FG devices in low voltage applications.

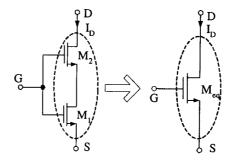

Figure 1.7: Self-cascode MOSFET.

#### 1.1.3 Self-Cascode Technique

Self-cascode MOSFET [15, 32] has high output impedance as conventional cascode topology does, but it avoids the disadvantage of the cascode topology — loss of linear output signal swing. As shown in Figure 1.7, the self-cascode MOSFET consists of MOSFETs  $M_1$  and  $M_2$  connecting in series with their gates tied together. Since  $M_1$  operates in deep triode region,  $V_{DS1}$  is quite small. Hence, the saturation voltage of the self-cascode MOSFET is similar to that of the simple MOSFET, which makes the composite MOSFET feasible for low-voltage applications. Assume  $M_1$  and  $M_2$  have the same threshold voltage. Depending on the operation mode of  $M_2$ , the drain current  $I_D$  is expressed as

$$I_D = \begin{cases} \frac{1}{2} \mu C_{ox} \left(\frac{W}{L}\right)_{eq} \left(V_{GS} - V_{th}\right)^2 & \text{if } M_2 - \text{saturation region} \\ \mu C_{ox} \left(\frac{W}{L}\right)_{eq} \left(V_{GS} - V_{th} - \frac{1}{2}V_{DS}\right) V_{DS} & \text{if } M_2 - \text{linear region} \end{cases}$$

Hence, the combined MOSFETs are equivalent to a single MOSFET operating in saturation or linear region with an effective aspect ratio of

$$\left(\frac{W}{L}\right)_{eq} = \frac{\left(\frac{W}{L}\right)_2 \left(\frac{W}{L}\right)_1}{\left(\frac{W}{L}\right)_2 + \left(\frac{W}{L}\right)_1} \tag{1.8}$$

For optimum operation, the aspect ratio of  $M_2$  is normally chosen to be much larger than that of  $M_1$ . In this case,  $(W/L)_{eq} \approx (W/L)_1$ . If the composite MOSFET operates in saturation region, the output impedance equals to  $g_{m2}r_{ds2}r_{ds1}$ , where  $g_{m2}$

is the transconductance of  $M_2$ ,  $r_{ds1}$  and  $r_{ds2}$  are the output conductance of  $M_1$  and  $M_2$ , respectively. The circuit characteristics of the self-cascode and the conventional cascode topologies are compared in Table 1.1.3. It should be noted that although

Table 1.2: Comparison of self-cascode and conv. cascode topologies

| Topology     | $g_m$    | $r_{out}$              | $V_{out,min}$      |

|--------------|----------|------------------------|--------------------|

| Self-cascode | $g_{m1}$ | $g_{m2}r_{ds2}r_{ds1}$ | $\approx V_{DSAT}$ |

| Cascode      | $g_{m1}$ | $g_{m2}r_{ds2}r_{ds1}$ | $2V_{DSAT}$        |

self-cascode and conventional cascode topology have the same output impedance format,  $r_{out}$  of self-cascode topology is smaller than that of the conventional cascode topology. This is because both transistors in conventional cascode topology operate in saturation region, while one of the transistors in self-cascode topology operate in linear region. Although self-cascode topology provides higher output swing, the input still suffers from threshold voltage limitation which is a major hurdle to achieve low-voltage applications.

#### 1.1.4 Level-Shifting Technique

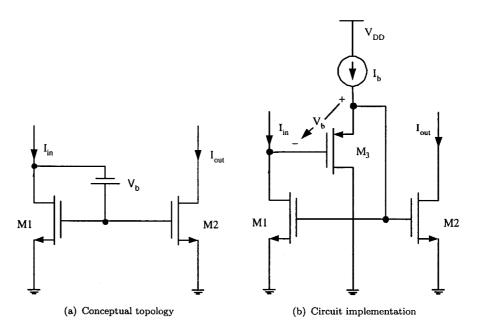

Level-shifting technique is used to reduce the power supply requirement by adding extra circuits to shift the signal DC level to a lower level. This technique is illustrated by an example. Figure 1.8 shows a modified simple CM using level-shifting technique. Instead of short connecting the drain and gate terminals of MOSFET  $M_1$  as the conventional simple CM does, a DC level-shifting voltage  $V_b$  is added between these two terminals. This method reduces the minimum input voltage requirement to  $V_{DSAT}$  as compared to  $V_{th} + V_{DSAT}$  of the conventional CM. In practice, the DC level shifting can be implemented by a source follower as shown in Figure 1.8(b). Similarly, level-shifting technique can be utilized to other conventional CM structures that have diode connections at the input.

Conventionally, the application of level-shifting technique is mainly limited to current

Figure 1.8: Modified simple CM with level shifting technique.

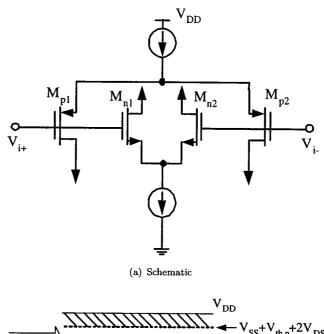

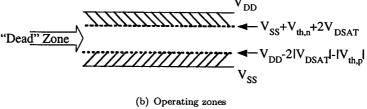

mirror structures. Recently, this technique is extended to 1 V rail-to-rail operational amplifier designs and the concept of dynamic level shifting [2] was proposed. The parallel-connected complementary differential pairs in the input stage (Figure 1.9) are traditionally used to fully exploit the limited signal room resulted from the limited power supply values. However, for extremely low voltage supplies (such as 1 V), this topology loses its merit by leaving a "dead" zone around the mid-range of the power supplies: neither NMOS nor PMOS pairs are turned on in this range. Dynamic level shifting solves this problem by shifting the input voltages ( $V_{i+}$  and  $V_{i-}$ ) adaptively based on the value of  $V_{ic}$ , where  $V_{ic}$  is the common mode component of the inputs and  $V_{ic} = (V_{i+} + V_{i-})/2$ . When  $V_{ic}$  is within the "dead" zone,  $V_{i+}$  ( $V_{i-}$ ) is shifted up (down) to turn on NMOS (PMOS) pair; when  $V_{ic}$  is close to one of the power supplies, no shifting will be applied to the input pairs. This adaptive mechanism is implemented by the level-shifting current generator and resistors. The concept of dynamic level-shifting is illustrated in Figure 1.10. The common mode components

Figure 1.9: Complementary differential pair input stage.

$V_{cm,shift}$  for NMOS and PMOS pairs are

$$V_{cm,shift} = \left\{ egin{array}{ll} V_{ic} + IR & ext{for NMOS pair} \ V_{ic} - IR & ext{for PMOS pair} \end{array}

ight.$$

Figure 1.10: Concept of dynamic level shifting [2].

Obviously, dynamic level-shifting technique increases the circuit complexity, power consumption as well as noise.

#### 1.1.5 Subthreshold Technique

In subthreshold (weak inversion) region, MOSFET exhibits exponential relationship between gate voltage and drain current as shown in Equation 1.9 [33,34].

$$I_D \cong I_{D0} \frac{W}{L} e^{V_{GB}/nU_T} \left( e^{-V_{SB}/U_T} - e^{-V_{DB}/U_T} \right)$$

(1.9)

where

$V_{GB}$  = gate to body voltage,

$V_{SB}$  = source to body voltage,

$V_{DB} = \text{drain to body voltage},$

$n = \left(C_{ox} + C_{dept}\right) / C_{ox} \cong 1.5,$

$C_{ox}$  = oxide capacitance,

$C_{dept}$  = surface depletion capacitance,

$U_T = kT/q$ ,

$I_{D0} = \text{characteristic current},$

$I_{D0}$  is a process-dependent parameter that varies from batch to batch, therefore, the circuits should be designed such that their performance is based on the ratios instead of the absolute values of the drain currents. For  $V_S = V_B = 0$  and  $V_{DS} > U_T$ , which is usually true for subthreshold circuit designs, Equation 1.9 can be simplified as

$$I_D \cong I_{D0} \frac{W}{L} e^{V_{GS}/nU_T} \tag{1.10}$$

The transconductance in weak inversion can be easily derived from Equation 1.10 as

$$g_m = \frac{I_D}{nU_T} \tag{1.11}$$

For a MOSFET,  $g_m/I_D$  reaches to the maximum value in weak inversion. It means MOSFET reaches the highest processing rates per unit power at subthreshold operation. This property as well as exponential input-output characteristics can be beneficially utilized in many low power, low voltage and low frequency applications. One application [35] is nonlinear systems analysis and synthesis (such as rms-dc converters [36, 37], oscillators [38], phase detectors [39] and phase-locked loops [40]) based on translinear principle, which was first introduced by Gilbert in 1975 [41]. The second major application is log-domain filters designs [42–48] that rely on voltage companding principle. At the input stage of the log-domain filters, the input currents are compressed logarithmically into voltage signals. Hence, the signal swings are drastically reduced, that leads to reduced the power supply. After the signal processing block, the voltages signals are expanded exponentially and converted back to current signals. Although the signal is processed non-linearly within the circuit, the overall linearity is preserved. Thus, the log-domain technique is well suited for low-voltage analog signal processing applications. Since subthreshold MOSFETs can implement wide varieties of large-signal linear/nonlinear real-time functions, they are

used in different applications such as neural networks, image processing and hearing aids systems. One limitation of the subthreshold MOSFET is its small transconductances due to the small bias currents. In addition, log domain circuits are sensitive to threshold voltage mismatch which leads to considerable linearity degradation.

#### 1.1.6 Dynamic Threshold Voltage MOSFET

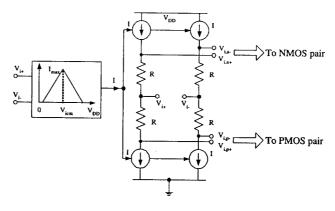

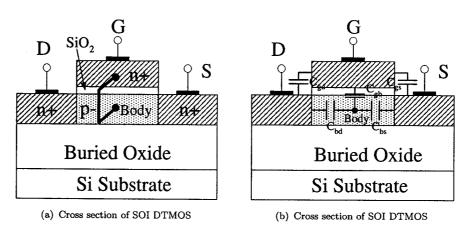

Figure 1.11: SOI DTMOS [1].

Dynamic Threshold Voltage MOSFET (DTMOS) is implemented by using siliconon-insulator (SOI) substrate. By connecting the gate electrode directly to the body

region [49–54] of a SOI MOSFET, the threshold voltage of MOSFET is dynamically

controlled: when the device is turned on, the threshold voltage decreases to allow

high switching speed and large current drive. When the device is turned off, the

threshold voltage increases to reduce the leakage current. Thus, DTMOS achieves

high speed and low stand-by power at low supply voltage. The cross section of SOI

DTMOS is shown in Figure 1.11. The DTMOS concept attracted a lot of research

attention since it was first proposed in 1994 [49]. Many novel circuit topologies based

on DTMOS and its derivatives have been proposed in a short period of time, such

as buffers and drivers [55–58], pass-gate logics [59–61]. By utilizing the low parasitic

Table 1.3: Parasitic capacitance of SOI MOSFET [1]

| Operation Mode | Approximate value                                                     |

|----------------|-----------------------------------------------------------------------|

| Triode         | $C_{gs} = 1/2C_{ox}, C_{gd} = 1/2C_{ox}, C_{gb} \approx 0$            |

|                | $C_{bs} \& C_{bd} = \sqrt{qN_d\varepsilon_{si}/2(V_{bi} - V_{bias})}$ |

| Saturation     | $C_{gs} = 2/3C_{ox}, C_{gd} = C_{gdo}, C_{gb} \approx 0$              |

|                | $C_{bs} \& C_{bd} = \sqrt{qN_d\varepsilon_{si}/2(V_{bi} - V_{bias})}$ |

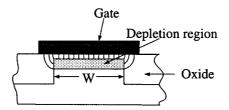

capacitances and high drive-current characteristics of DTMOS, a 0.5 V multiplexer and demultiplexer with high-speed, low-voltage, and low power was proposed in [62]. [63] and [64] indicate that DTMOS can be considered as a very promising candidate for low-power, low-voltage RF applications thanks to its high current driving ability and high output impedance. However, with both gate and body tied together, DTMOS is prohibited to operate with gate-source voltages above the turn-on voltages of the source/drain (S/D) junctions. Compared to conventional floating-body SOI, DTMOS technology has another disadvantage: it has increased input parasitic capacitance due to the added body capacitances such as body-source capacitance  $C_{bs}$  and body-drain capacitance  $C_{bd}$ . Figure 1.11(b) shows the parasitic capacitances of SOI DTMOS and Table 1.3 gives their approximate values [1,49].  $C_{bs}$  and  $C_{bd}$  are the pn junction capacitances that vary with the bias voltage  $V_{bias}$ . In Table 1.3,  $V_{bi}$  refers to the builtin potential;  $N_d$  is the doping density of the body;  $\varepsilon_{si}$  is the permittivity of silicon and q is the magnitude of electronic charge. Gate-to-body capacitance  $C_{gb}$  is zero due to the short connection of gate and body terminals.  $C_{gdo}$  denotes the gate-drain overlap capacitance and fringing capacitance. The third disadvantage of DTMOS using SOI is high body resistance, which leads to speed degradation. Currently, DTMOS technology is under investigation and verification mainly at device level. Research activities in this area include finding techniques to overcome the above limitations as well as building accurate models for DTMOS characterization.

#### 1.2 ORGANIZATION

This thesis focuses on body-driven technique and is organized into 5 chapters. Chapter 2 discusses the model issues of BD MOSFETs. In this chapter, the accuracy of the current industrial-standard model BSIM3V3 in describing the performance of BD MOSFETs is evaluated. Modifications of BSIM3V3 are presented to achieve better simulation accuracy. The scaling effects on the future performance of BD MOSFET are also investigated.

Chapter 3 studies the weakness of the conventional BD CMs and proposes the design techniques to enhance their performance. Later, Chapter 3 presents a novel high performance regulated BD CMOS CM for low-voltage applications. Comprehensive analysis of the proposed CM is carried out including DC characteristics, frequency and noise performance. To facilitate the optimization, the design methodology is also discussed in detail.

Operational transconductance amplifier (OTA) is another useful building block for analog signal procession. In Chapter 4, the deficiencies of the existing OTA topologies in meeting the linearity requirements of low-voltage applications are discussed first. By using BD technique, a differential triode-based OTA with enhanced linearity, wider tuning range as well as input range is presented in Chapter 4. Detailed evaluation of the proposed OTA is provided that covers the nonlinearity analysis, frequency response, common-mode feedback design and noise analysis. Finally, an OTA-C filter design example is given to demonstrate the applications of the proposed OTA.

Finally, Chapter 5 summarizes the contributions of the research and directions for future work are suggested.

#### Chapter 2

#### **BODY-DRIVEN MOSFET MODEL**

A very critical part of process development is the ability to rapidly and precisely measure devices during the process development cycle and use these data to construct accurate and predictive device models. This creates both measurement and modeling challenges for the analog circuits. Since body terminal instead of gate is used as active input terminal of BD circuit, special modeling emphasis should be given to the effects that are associated with the body terminal.

#### 2.1 MOSFET MODELS

MOSFET models [65] can be classified into three categories:

#### Analytical model

Analytical model intends to help understanding the MOSFET behavior by linking the physical process and geometry parameters to the electrical behavior through analytical equations. With the advent of new technology, analytical model is normally scalable with some minor modifications.

#### • Table lookup model [66–68]

Unlike analytical model, table lookup model does not give physical insight into device behavior. It is based on mathematical methods that store the measured device data for different bias conditions and device geometries in a tabular form. Table lookup model is technology independent and requires much less time to develop compared to analytical model. However, it is not scalable.

#### • Empirical model [69]

The model equations in empirical model do not represent physical meanings

but are generated purely from curve fitting. Empirical model is technology dependent. Although it requires smaller data memory as compared to table lookup model, purely empirical model is seldom used in circuit simulators.

Most of the existing models belong to analytical model category and the notable analytical MOSFET models include physics-based BSIM3 (Berkeley Short-Channel IGFET Model) developed by the BSIM Research Group at the University of California, Berkeley; Model 9 [70] brought by Philips Research Laboratories and EKV model [71] supplied by Swiss Federal Institute of Technology (EPFL), Switzerland. Compared with BSIM3, Model 9 achieves similar accuracy in circuit simulation with fewer number of parameters. However, companies generally choose BSIM3 because it was not obvious whether there were intellectual property issues associated with MOS Model 9 [72]. Unlike other models which use source-referencing, EKV model brings a unique style of MOSFET modeling by using body as the voltage reference point. This feature makes it possible to simulate MOSFETs as symmetrical devices. The EKV model has more physical basis and much less parameters compared with other models. However, due to the late arrival, EKV is still a work in progress and not yet popular. In this chapter, we only focus on BSIM3V3 (BSIM3 Version 3) model due to the following reasons:

- BSIM3V3 is the first international industry standard. It has been the worldwidely public-used model for CMOS IC design.

- Many semiconductor dedicated foundry, including the market leader TSMC, only supports and provides technology parameters based on BSIM3V3 model.

- BSIM3V3 has demonstrated to be adequate for a majority of analog and digital circuit simulation in deep-submicron technologies including 0.18 μm technology.

The intention of this chapter is to investigate and evaluate the current industrialstandard model BSIM3V3, identify the aspects that the model shows inadequacies in simulating BD MOSFET, analyze how these inadequacies affect the description of the BD device behavior. Then, a modified model which provides improved accuracy in characterizing BD MOSFET is developed based on the above analysis. Finally, in order to evaluate how the BD MOSFET performance will be affected by the scaling trend, detailed analytical analysis is carried out on the major parameters that characterize the device.

#### 2.2 OVERVIEW OF BSIM3V3 MODEL

As an enhanced version of BSIM3, BSIM3V3 not only maintained the physical characteristics of BSIM3, but also launched several enhanced features.

- Previous generations of SPICE models used distinct I-V equations for different operating regions, which lead to discontinuities in the device characteristics. In order to avoid such numerical difficulties incurred by regional-model equation, a unified I-V model is developed in BSIM3V3 with the introduction of smoothing functions, such as V<sub>BS,eff</sub>, V<sub>DS,eff</sub>, V<sub>FB,effCV</sub>, V<sub>GST,eff</sub>, V<sub>GST,effCV</sub>. These smoothing functions gradually change a variable between two extreme values, thus smoothing out the transition between the linear and saturation region, between the subthreshold and strong inversion. This guarantees the continuity of drain current, conductance, output conductance and their derivatives throughout all operation regimes.

- New width dependencies for bulk charge and source/drain resistance  $(R_{ds})$  are introduced. This is especially beneficial in improving the accuracy in modeling narrow width devices.

- The fact that channel width/length offset depends on device's geometry is considered in BSIM3V3 model. This expands the model's capacity to fit a wide range of W/L with a single set of parameters.

- An improved capacitance model has been formulated that accurately describes

the C-V characteristics of the device with the channel length down to deep

submicron region. Also, non-quasi-static model option is included.

- Binning option is provided to further improve the model accuracy.

#### 2.3 THRESHOLD VOLTAGE MODEL IN BSIM3V3

Since body/bulk is used as the input terminal instead of gate, accurate modeling of body-effect, i.e., threshold voltage  $(V_{th})$ , is one of the most important requirements for characterizing BD MOSFET. Of course, accurate prediction of threshold voltage also serves as a useful reference point for the evaluation of device operating regions [3]. First, if the gate-source voltage  $V_{gs}$  is greater than the threshold voltage  $V_{th}$ , the inversion charge density is larger than the substrate doping concentration. MOSFET is operating in the strong inversion region and drift current is dominant. Second, if the gate voltage is smaller than  $V_{th}$ , the inversion charge density is much smaller than the substrate doping concentration. The transistor operates in the weak inversion (or subthreshold) region and diffusion current is now dominant. Lastly, if the gate voltage is very close to  $V_{th}$ , the inversion charge density is close to the doping concentration. The MOSFET operates in the transition region. In such a case, both diffusion and drift currents are equally important.

For a MOSFET with long channel length/width and uniform substrate doping concentration, the threshold voltage  $V_{th}$  is given by:

$$V_{th} = V_{th0} + \gamma \sqrt{2\phi_F - V_{BS}} - \gamma \sqrt{2\phi_F} \tag{2.1}$$

where

$\gamma = \sqrt{2q\varepsilon_{si}N_a}/C_{ox},$

$N_a$  = the doping concentration of the p-type substrate,

$C_{ox}$  is expressed as  $\varepsilon_{ox}/t_{ox}$ , where  $t_{ox}$  is the thickness of the silicon dioxide and  $\varepsilon_{ox}$  is

its permittivity.  $V_{th0}$  is given as

$$V_{th0} = V_{FB} + 2\phi_F + \gamma\sqrt{2\phi_F} \tag{2.2}$$

$V_{FB}$  is flat band voltage. Neglecting the small "parasitic" charge within the oxide as well as at the oxide-semiconductor interface, the flat band voltage is mainly contributed by the net contact potentials from gate, through external connection to substrate. For conventional silicon technology, gate of N-channel MOSFET is heavily doped with n-type impurities. Thus,  $V_{FB}$  numerically equals to the contact potential of degenerated n+ polysilicon minus Fermi potential  $\phi_F$  (i.e., the negative of the contact potential of the lightly doped substrate), which is shown as

$$V_{FB} = -E_g/2q - \phi_F = -0.56 - \frac{kT}{q} \ln \frac{N_a}{n_i}$$

(2.3)

where

$n_i = \text{intrinsic carrier concentration},$

$E_g = \text{energy band-gap of silicon}.$

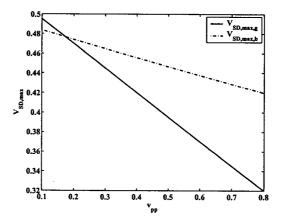

It is seen from Equation 2.1 that threshold voltage depends on  $N_a$  and  $t_{ox}$ . If  $N_a$