# RF TRANSCEIVER FOR CODE-SHIFTED REFERENCE IMPULSE-RADIO ULTRA-WIDEBAND (CSR IR-UWB) SYSTEM

by

Jet'aime D. Lowe

Submitted in partial fulfilment of the requirements for the degree of

Master of Applied Science

at

Dalhousie University Halifax, Nova Scotia June 2010

# **DALHOUSIE UNIVERSITY**

#### Faculty of Engineering

The undersigned hereby certify that they have read and recommend to the Faculty of Graduate Studies for acceptance a thesis entitled "RF Transceiver for Code-Shifted Reference Impulse-Radio Ultra-Wideband (CSR IR-UWB) System" by Jet'aime D. Lowe in partial fulfilment of the requirements for the degree of Master of Applied Science.

|             | Dated: June 2 <sup>nd</sup> , 2010 |

|-------------|------------------------------------|

| Supervisor: |                                    |

|             | Dr. Zhizhang (David) Chen          |

| Readers:    |                                    |

|             | Dr. Hong Nie                       |

|             | Dr. Yuan Ma                        |

|             | Dr. William Phillips               |

# **DALHOUSIE UNIVERSITY**

#### Faculty of Engineering

DATE:

| AUTHOR:  | Jet'aime D. Lowe                                        |                                   |             |                |           |

|----------|---------------------------------------------------------|-----------------------------------|-------------|----------------|-----------|

| TITLE:   | RF Transceiver<br>Wideband (CSR IR                      | for Code-Shifted<br>L-UWB) System | Reference   | Impulse-Rad    | io Ultra- |

| DEPARTME | ENT OR SCHOOL:                                          | Electrical and Co                 | omputer Eng | ineering       |           |

| DEGREE:  | MASc                                                    | CONVOCATION:                      | October     | YEAR:          | 2010      |

|          | ission is herewith gron-commercial purpor institutions. | oses, at its discretion           | •           | title upon the |           |

The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.

The author attests that permission has been obtained for the use of any copyrighted material appearing in the thesis (other than the brief excerpts requiring only proper acknowledgement in scholarly writing), and that all such use is clearly acknowledged.

# TABLE OF CONTENTS

| List of | Table  | s                                                              | vii  |

|---------|--------|----------------------------------------------------------------|------|

| List of | Figure | es                                                             | viii |

| List of | Abbre  | eviations                                                      | xii  |

| Ackno   | wledgi | ments                                                          | xiv  |

| Abstra  | ct     |                                                                | XV   |

| CHAP    | TER 1  | : Introduction                                                 | 1    |

| 1.1     | Moti   | vation                                                         | 1    |

| 1.2     | Thes   | sis Outline                                                    | 3    |

| CHAP    | TER 2  | 2: Background of UWB                                           | 5    |

| 2.1     | UWI    | B Definition and Regulations                                   | 5    |

| 2.2     | Туре   | es of UWB Transmission                                         | 10   |

| 2.2     | 2.1    | Multi-band ODFM UWB                                            | 11   |

| 2.2     | 2.2    | Impulse-Radio UWB                                              | 13   |

| 2.3     | The    | IR-UWB Pulse                                                   | 14   |

| 2.3     | 3.1    | Pulse Spectral Bandwidth                                       | 14   |

| 2.3     | 3.2    | Pulse Spectral Amplitude                                       | 15   |

| 2.3     | 3.3    | Pulse Shape                                                    | 15   |

| 2.4     | Adva   | antages of IR-UWB Technology                                   | 18   |

| 2.4     | 4.1    | Large Capacity and High Data-Rate                              | 18   |

| 2.4     | 1.2    | Flexibility in Data Rate versus Transmit Distance              | 19   |

| 2.4     | 1.3    | Low Interference and Low Probability of Detection/Interception | 19   |

| 2.4     | 1.4    | Multipath Immunity                                             | 20   |

| 2.5  | Ap  | pplications                                     | 21 |

|------|-----|-------------------------------------------------|----|

| СНАР | TER | 3: Introduction to Code-Shifted Reference (CSR) | 23 |

| 3.1  | Pre | evious Implementation Schemes for IR-UWB        | 23 |

| 3.   | 1.1 | Rake Receiver                                   | 23 |

| 3.   | 1.2 | Transmit Reference Receiver                     | 25 |

| 3.1  | 1.3 | Frequency Shifted Reference                     | 27 |

| 3.2  | Co  | ode-Shifted Reference (CSR)                     | 28 |

| 3.2  | 2.1 | Differential Code-Shifted Reference (DCSR)      | 31 |

| 3.3  | Per | rformance Comparison                            | 35 |

| СНАР | TER | 4: First Proposed CSR Transmitter               | 43 |

| 4.1  | De  | sign Theory                                     | 43 |

| 4.   | 1.1 | Stage1: Pulse Generation                        | 44 |

| 4.   | 1.2 | Stage 2: Pulse Gating                           | 47 |

| 4.   | 1.3 | Stage 3: Signal Coding                          | 49 |

| 4.2  | Sir | nulation Results                                | 50 |

| 4.3  | Im  | plementation Results                            | 55 |

| 4.4  | Co  | onclusions                                      | 60 |

| СНАР | TER | 5: Proposed CSR Transmitter                     | 62 |

| 5.1  | De  | esign Theory                                    | 62 |

| 5.   | 1.1 | Stage1: Pulse Generator                         | 63 |

| 5.   | 1.2 | Stage2: Amplitude Modulation                    | 64 |

| 5.   | 1.3 | Stage3: Gate Pulse                              | 65 |

| 5.2  | Sir | nulation Results                                | 68 |

| 5.3  | Im  | plementation Results                            | 76 |

| 5.4  | Co  | nclusions                                       | 83 |

| CHAI   | PTER    | 6: Proposed CSR Receiver                    | . 85 |

|--------|---------|---------------------------------------------|------|

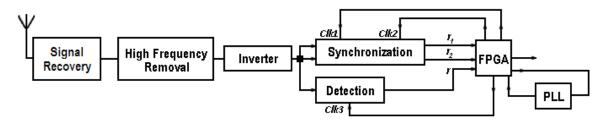

| 6.1    | Des     | sign Theory                                 | . 85 |

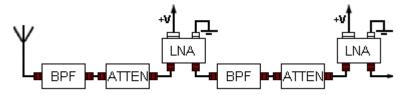

| 6.     | 1.1     | Stage 1: Signal Recovery                    | . 86 |

| 6.     | 1.2     | Stage 2: High Frequency Removal             | . 87 |

| 6.     | 1.3     | Stage3: Inverter                            | . 88 |

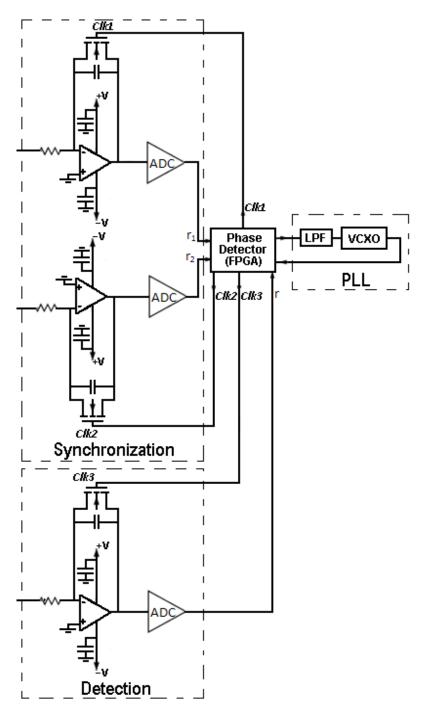

| 6.     | 1.4     | Stages 4 & 5: Synchronization and Detection | . 89 |

| 6.2    | Sin     | nulation Results                            | . 95 |

| 6.3    | Imp     | olementation Results                        | . 98 |

| 6.4    | Cor     | nclusions                                   | 106  |

| CHAI   | PTER    | 7: Transmitter & Receiver Improvements      | 107  |

| 7.1    | Tra     | nsmitter Improvements                       | 107  |

| 7.2    | Red     | ceiver Improvements                         | 112  |

| 7.3    | Cor     | nclusions                                   | 113  |

| CHAI   | PTER    | 8: Conclusion                               | 114  |

| 8.1    | Fut     | ure Work                                    | 116  |

| Refere | ences   |                                             | 117  |

| Apper  | ıdix    |                                             | 122  |

| Firs   | t Trans | smitter Design (corresponds to Chapter4)    | 122  |

| Seco   | ond Tr  | ransmitter Design (corresponds to Chapter5) | 123  |

| Rec    | eiver I | Design (corresponds to Chapter6)            | 127  |

| Full   | Syste   | m Implementation: Test Set-up               | 130  |

# LIST OF TABLES

| Toble 2.1. ECC emissi    | on limits for indoor    | and outdoor LIWP | transmission9  |

|--------------------------|-------------------------|------------------|----------------|

| Table 2.1. Full tillissi | OH HIIIIIS TOL HIGOOL & | and outdoor o wb | uansiinssion 9 |

# LIST OF FIGURES

| Figure 2.1: Spectral Comparison of UWB and Narrowband Transmission                         | 6  |

|--------------------------------------------------------------------------------------------|----|

| Figure 2.2: FCC spectral mask for (a) indoor and (b) outdoor systems                       | 8  |

| Figure 2.3: Wireless systems operating in the same bandwidth as UWB                        | 10 |

| Figure 2.4: OFDM (a) original single-carrier, (b) multi-band with overlapping, and         |    |

| (c) multi-band without overlapping                                                         | 12 |

| Figure 2.5: MBOA MB-OFDM Channel allocation                                                | 13 |

| Figure 2.6: (a) Time domain waveforms of n <sup>th</sup> order Gaussian waveforms, and (b) |    |

| frequency spectrum of n <sup>th</sup> order Gaussian waveforms                             | 17 |

| Figure 2.7: Occurrence of multipath in an indoor environment                               | 20 |

| Figure 3.1: General Rake receiver structure (with 2 MPCs)                                  | 23 |

| Figure 3.2: Comparison of the principles behind the A-rake (a) and (b) S-rake              | 24 |

| Figure 3.3: General TR receiver structure                                                  | 25 |

| Figure 3.4: TR receiver detection procedure                                                | 26 |

| Figure 3.5: General FSR receiver structure                                                 | 28 |

| Figure 3.6: General CSR transmitter structure.                                             | 29 |

| Figure 3.7: General CSR receiver structure                                                 | 30 |

| Figure 3.8: General DCSR transmitter structure                                             | 31 |

| Figure 3.9: DCSR Transmitter Example Results                                               | 33 |

| Figure 3.10: General DCSR receiver structure                                               | 34 |

| Figure 3.11: BER of the CSR system: theoretical vs. simulation results                     | 36 |

| Figure 3.12: BER of the DCSR system: theoretical vs. simulation results                    | 38 |

| Figure 3.13: BER comparison between DCSR, CSR, FSR and TR, M=2                             | 39 |

| Figure 3.14: BER comparison between DCSR, CSR, FSR and TR, M=3                             | 40 |

| Figure 4.1: Block diagram of first design of CSR Transmitter                               | 43 |

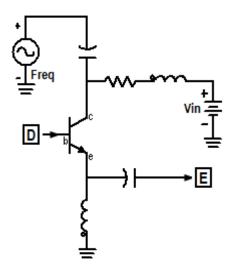

| Figure 4.2: Transmitter 'Pulse Generation' stage                                           | 45 |

| Figure 4.3: Theoretical time domain pulse waveforms for impulse generator                  | 46 |

| Figure 4.4: Concept of Pulse Gating in the time domain                                | 47 |

|---------------------------------------------------------------------------------------|----|

| Figure 4.5: Transmitter 'Gated Pulse' stage                                           | 47 |

| Figure 4.6: Theoretical time domain response of the 'Gated Pulse' stage               | 48 |

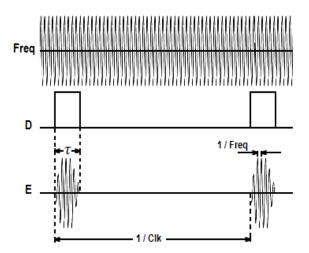

| Figure 4.7: Concept of pulse coding by the VGA                                        | 49 |

| Figure 4.8: Simulation schematic of 'Pulse Generation' and 'Gated Pulse' stages       | 51 |

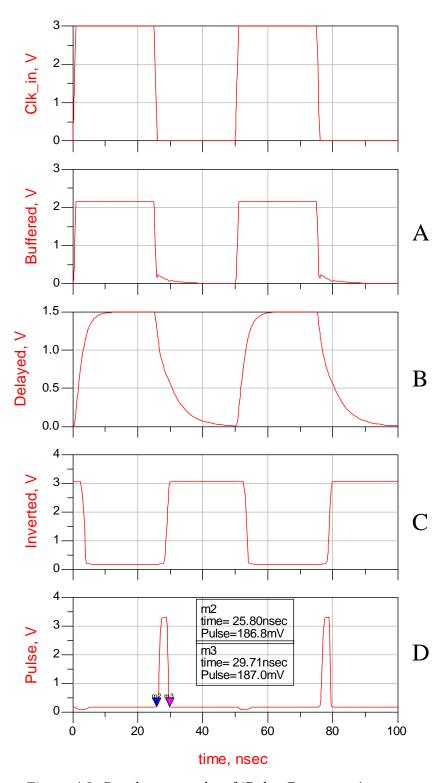

| Figure 4.9: Simulation results of 'Pulse Generation' stage                            | 52 |

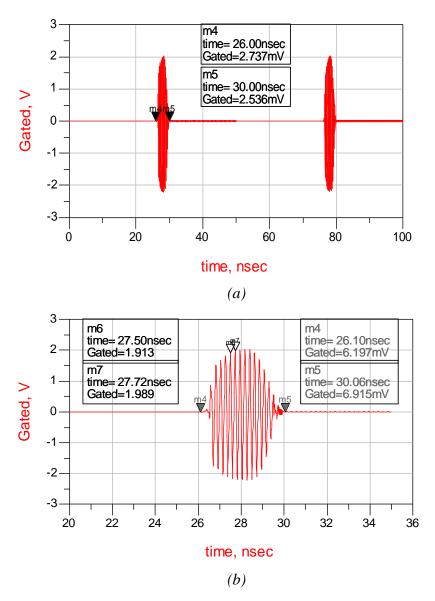

| Figure 4.10: Simulation results of the (a) 'Gated Pulse' stage and (b) Magnification  |    |

| of the gated pulse                                                                    | 53 |

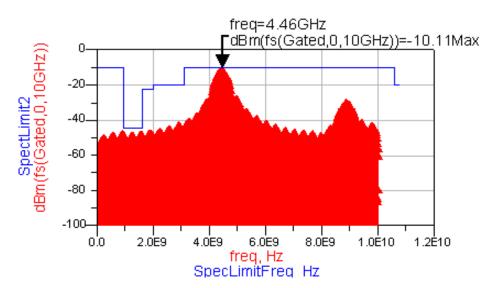

| Figure 4.11: Spectral response of the simulated pulse results against FCC indoor      |    |

| mask                                                                                  | 54 |

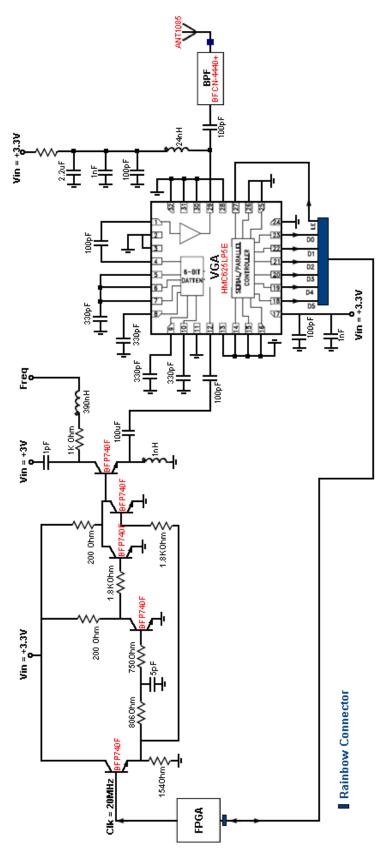

| Figure 4.12: Full Schematic of the first Transmitter design                           | 56 |

| Figure 4.13: Implementation results after 'Pulse Generation'                          | 57 |

| Figure 4.14: Implementation results after 'Pulse Gating'                              | 58 |

| Figure 4.15: Implementation results after VGA                                         | 58 |

| Figure 4.16: Implementation results after VGA with clock rate of (a) 5MHz and         |    |

| (b)100KHz                                                                             | 60 |

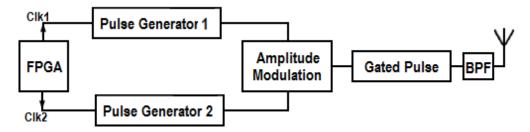

| Figure 5.1: Block Diagram of CSR Transmitter                                          | 62 |

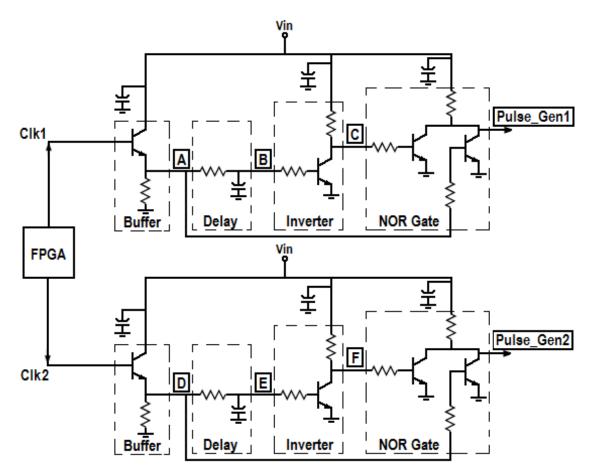

| Figure 5.2: Revised transmitter 'Pulse Generation' stage                              | 63 |

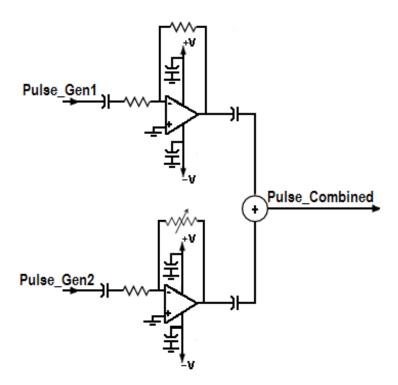

| Figure 5.3: Revised transmitter 'Amplitude Modulation' stage                          | 64 |

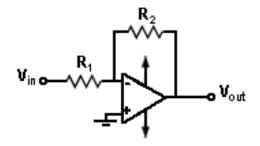

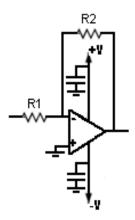

| Figure 5.4: General structure of the Inverting Op-amp                                 | 65 |

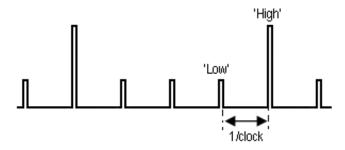

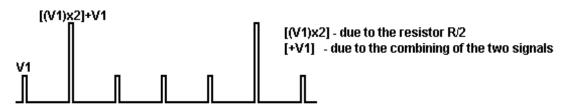

| Figure 5.5 Example of combined amplitude modulated pulse sequence                     | 65 |

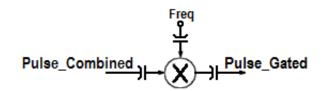

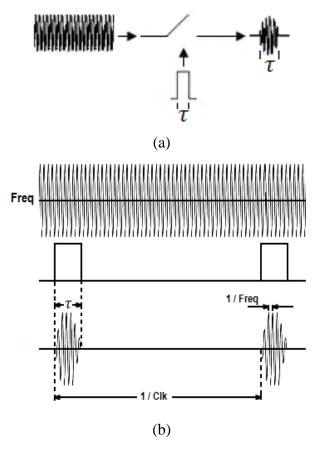

| Figure 5.6: Revised transmitter 'Gated Pulse' stage                                   | 66 |

| Figure 5.7: (a) Concept and (b) Application of gating signal in time domain           | 67 |

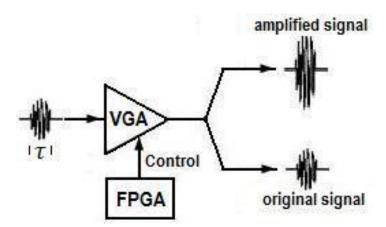

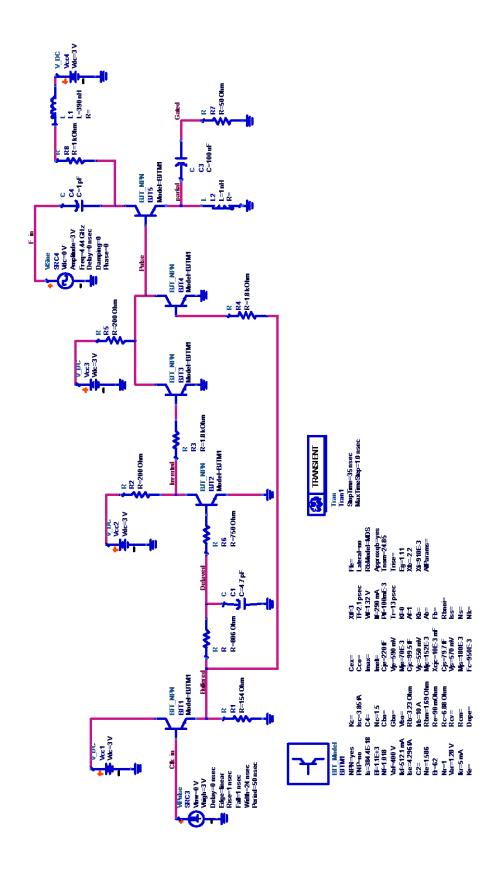

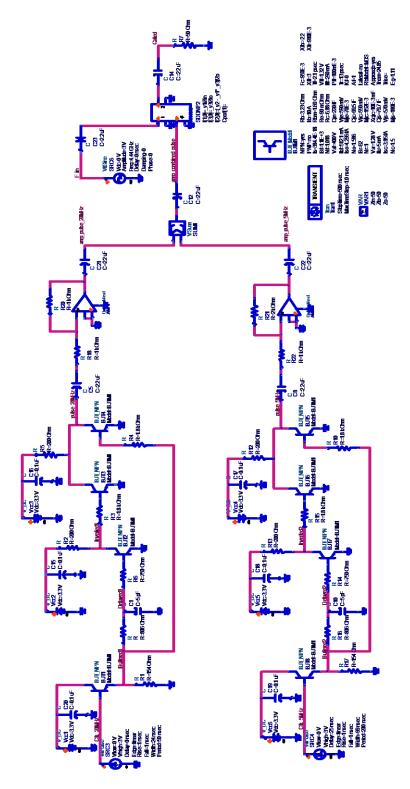

| Figure 5.8: Simulation schematic of revised CSR Transmitter                           | 68 |

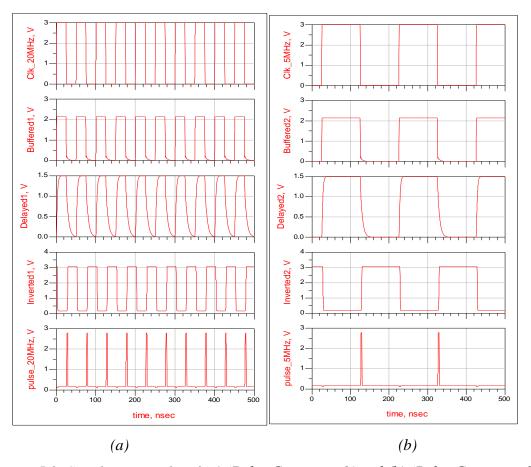

| Figure 5.9: Simulation results of (a) 'Pulse Generator 1' and (b) 'Pulse Generator 2' | 69 |

| Figure 5.10: Amplification Method1 to produce 3:1 ratio                               | 70 |

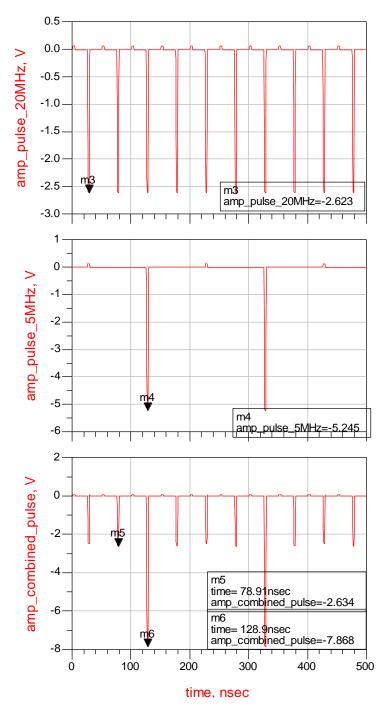

| Figure 5.11: Simulation results of 'Amplitude Modulation' stage of the transmitter –  |    |

| Amplification Method1                                                                 | 71 |

| Figure 5.12: Amplification Method2 to produce 3:1 ratio                               | 72 |

| Figure 5.13: Simulation results of 'Amplitude Modulation' stage of the transmitter –  |    |

| Amplification Method2                                                                 | 73 |

| Figure 5.14: Simulation results of the (a) 'Gated Pulse' stage and (b) Magnification  |

|---------------------------------------------------------------------------------------|

| of the gated pulse                                                                    |

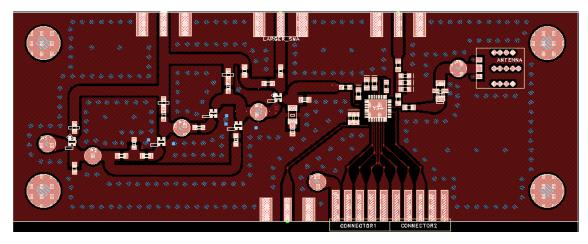

| Figure 5.15: Full design of the Transmitter implementation                            |

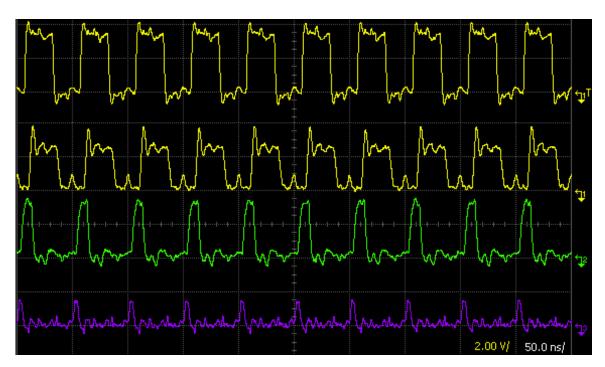

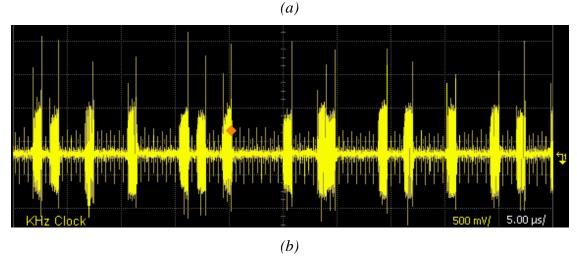

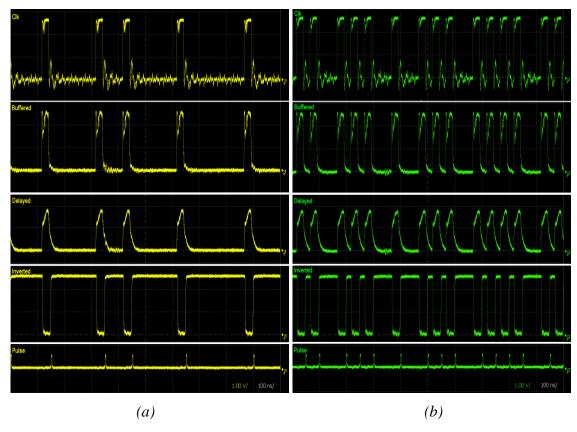

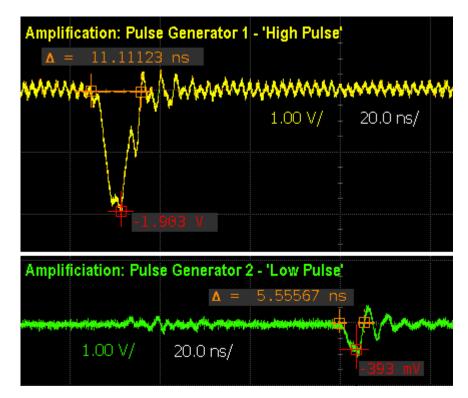

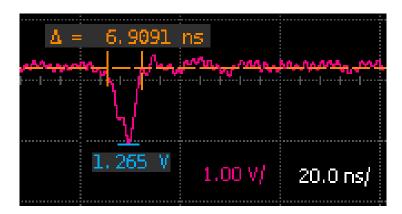

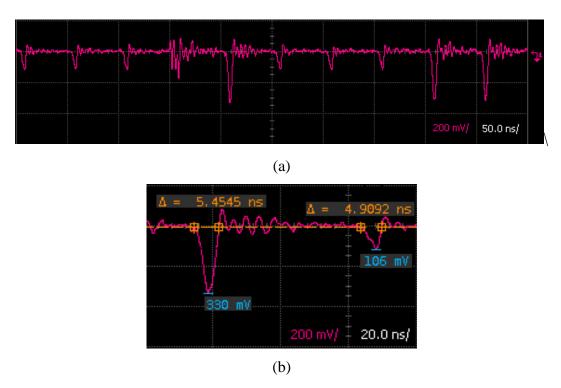

| Figure 5.16: Oscilloscope results of Board1 after each stage of – Pulse Generation79  |

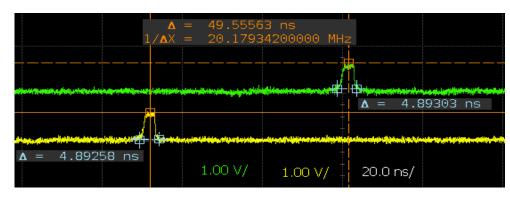

| Figure 5.17: Oscilloscope results of 'Pulse Generator 1' and 'Pulse Generator 2'      |

| impulses expanded80                                                                   |

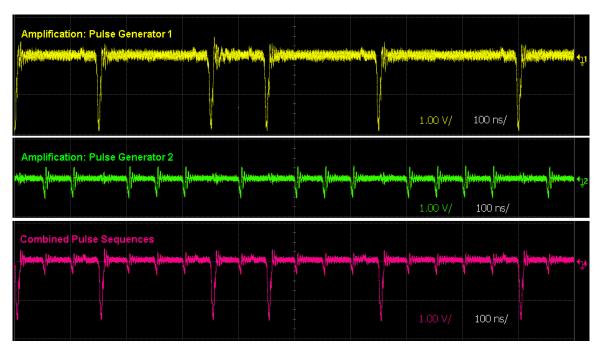

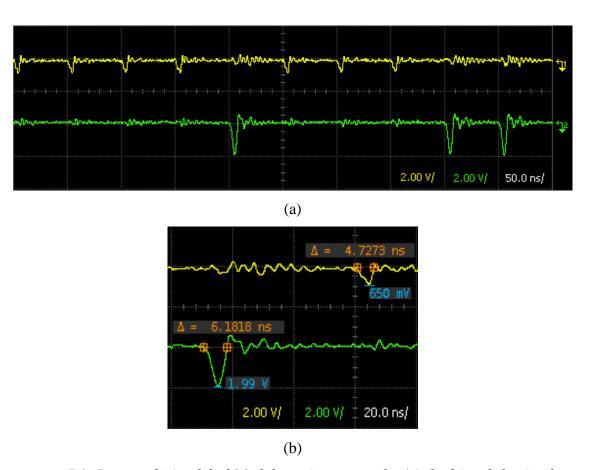

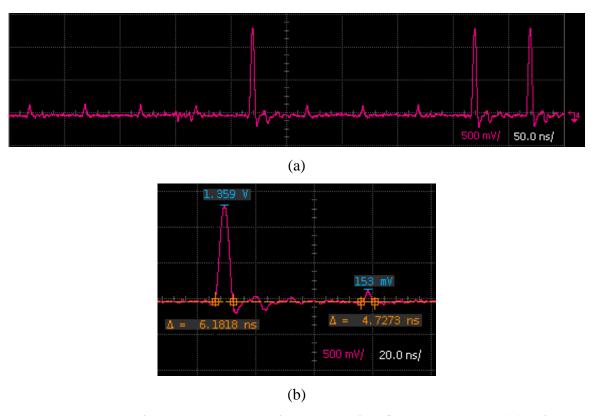

| Figure 5.18: Oscilloscope results of Board2 – Amplitude Modulation80                  |

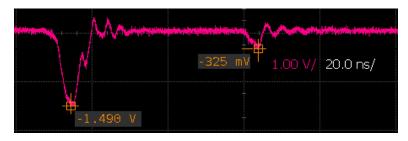

| Figure 5.19: Expansion of oscilloscope results for the combined pulse sequences       |

| after Amplitude Modulation81                                                          |

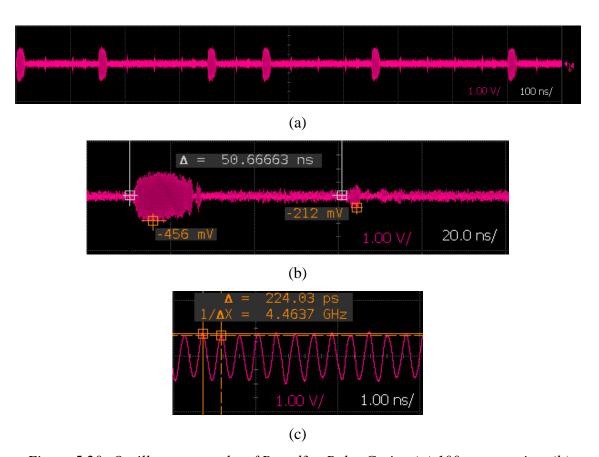

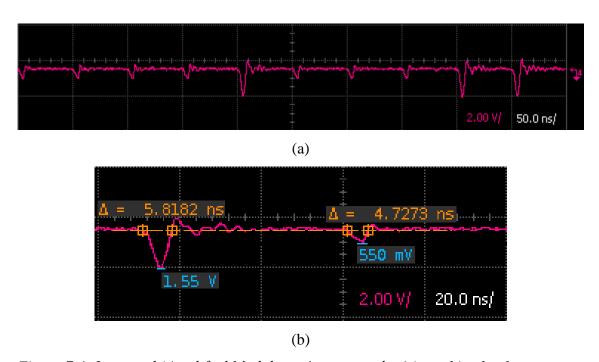

| Figure 5.20: Oscilloscope results of Board3 – Pulse Gating (a) 100ns expansion, (b)   |

| 20ns expansion, (c) 1ns expansion                                                     |

| Figure 6.1: Block diagram of CSR Receiver85                                           |

| Figure 6.2: Receiver 'Signal Recovery' stage                                          |

| Figure 6.3: Theoretically expected results after 'Signal Recovery' stage87            |

| Figure 6.4: Receiver 'High Frequency Removal' stage                                   |

| Figure 6.5: Theoretically expected results after the 'High Frequency Removal' stage88 |

| Figure 6.6: Receiver 'Inverter' stage                                                 |

| Figure 6.7: Receiver 'Synchronization' and 'Detection' stages90                       |

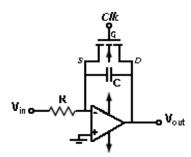

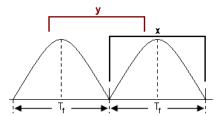

| Figure 6.8: Concept of the op-amp integrator91                                        |

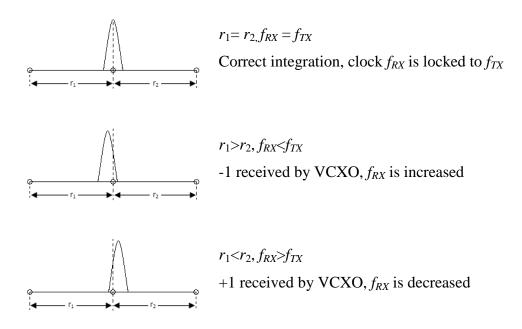

| Figure 6.9: Correct vs. incorrect integration                                         |

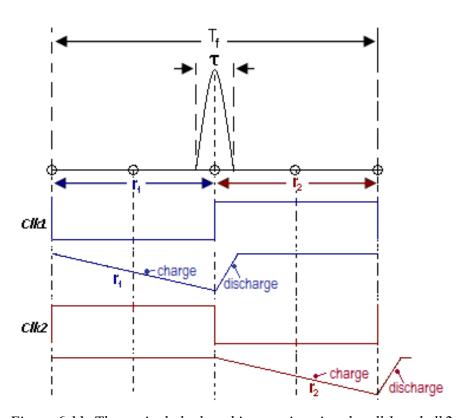

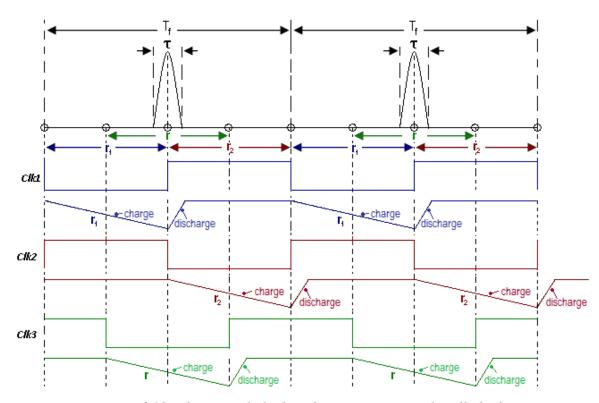

| Figure 6.10: Integration Signals 92                                                   |

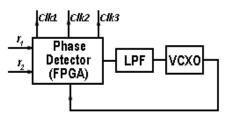

| Figure 6.11: Theoretical clock and integration signals: clk1 and clk293               |

| Figure 6.12: Synchronization concept                                                  |

| Figure 6.13: Theoretical clock and integration signals: all clocks95                  |

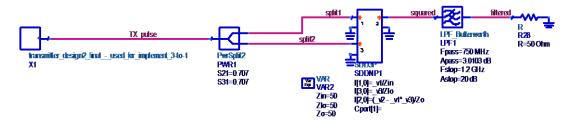

| Figure 6.14: Receiver simulation schematic                                            |

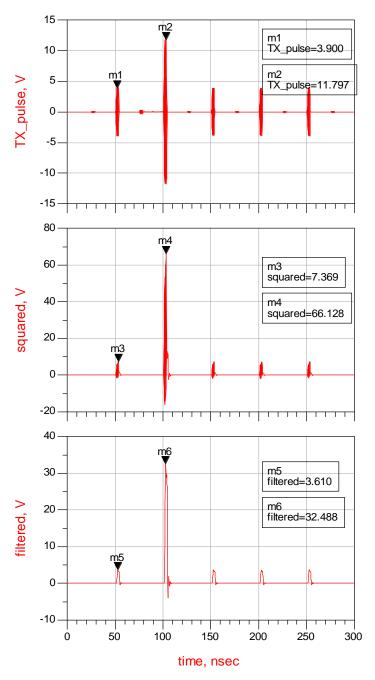

| Figure 6.15: Receiver simulation results – 'High Frequency Removal' stage97           |

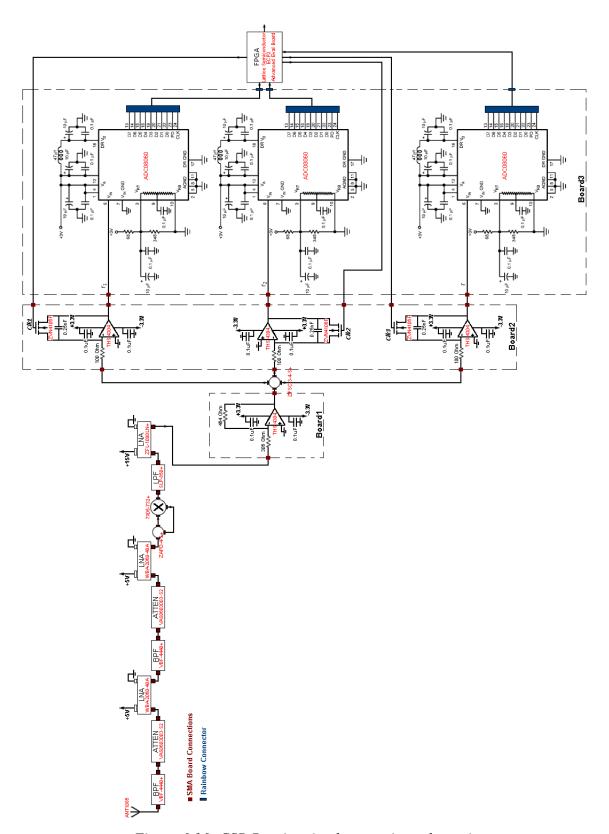

| Figure 6.16: CSR Receiver implementation schematic                                    |

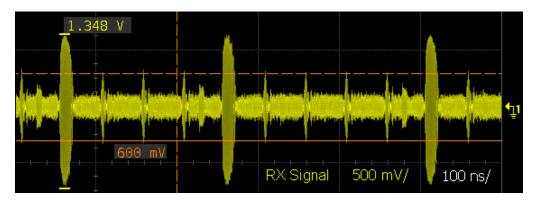

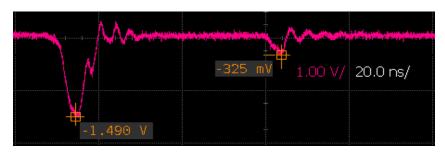

| Figure 6.17: Receiver implementation result - after the 'Signal Recovery' stage100    |

| Figure 6.18: Transmitter implementation result - after the 'Gated Pulse' stage100     |

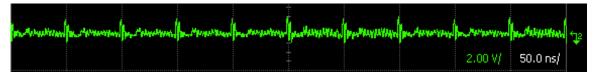

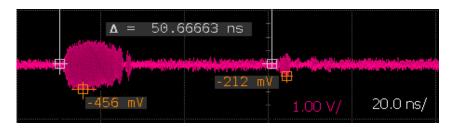

| Figure 6.19: Receiver encoded pulse sequence – after 'High Frequency Removal'         |

| stage (a) 100ns scale and (b) 20ns scale                                              |

| Figure 6.20: Transmitter encoded pulse sequence – after 'Amplitude Modulation'       |     |

|--------------------------------------------------------------------------------------|-----|

| stage                                                                                | 102 |

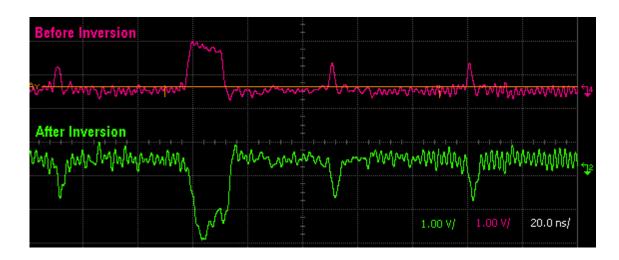

| Figure 6.21: Results before and after 'Inverter' stage                               | 103 |

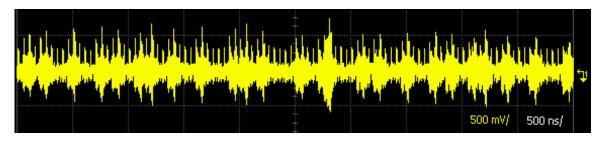

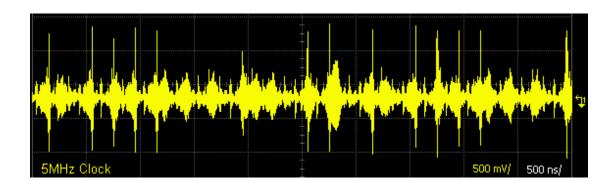

| Figure 6.22: Test results – integrator with no reset clock                           | 104 |

| Figure 6.23: Test results – integrator with reset clock                              | 105 |

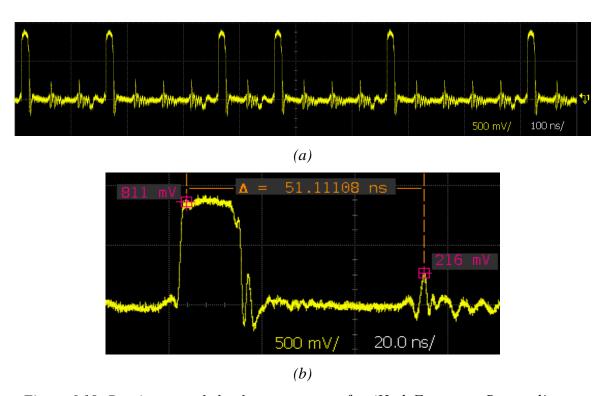

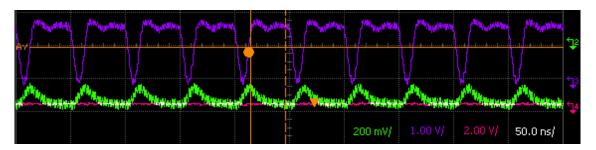

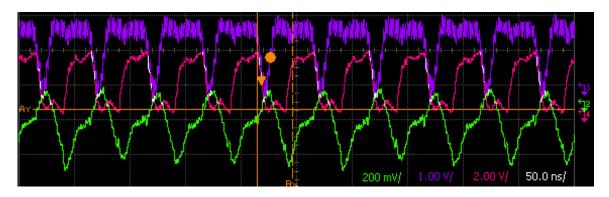

| Figure 7.1: 'Amplitude Modulation' stage results before improvements                 | 108 |

| Figure 7.2: 'Amplitude Modulation' stage test: 'high' pulse branch                   |     |

| (R <sub>1</sub> =R <sub>2</sub> =100Ohm)                                             | 108 |

| Figure 7.3: Improved 'Amplified Modulation' stage results (a) 'high' and 'low' pulse |     |

| sequences and (b) enlarged view                                                      | 109 |

| Figure 7.4: Improved 'Amplified Modulation' stage results (a) combined pulse         |     |

| sequence and (b) enlarged view                                                       | 110 |

| Figure 7.5: Results after added variable attenuator (a) combined pulse sequence and  |     |

| (b) enlarged view                                                                    | 112 |

| Figure 7.6: 'High Frequency Removal' stage results after improvements (a) pulse      |     |

| sequence and (b) enlarged view                                                       | 113 |

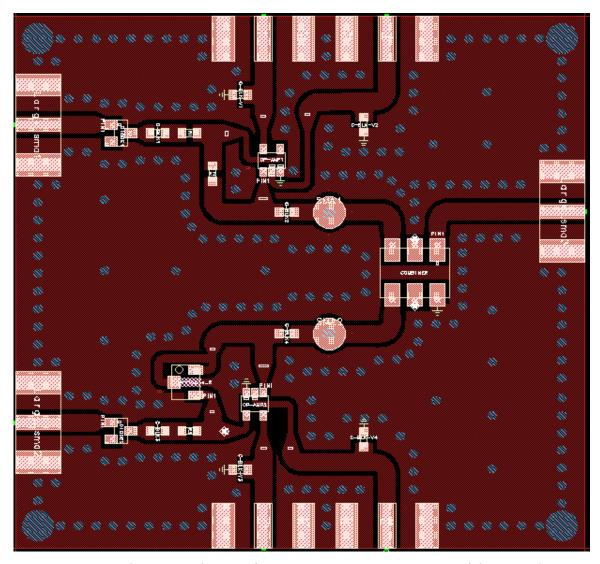

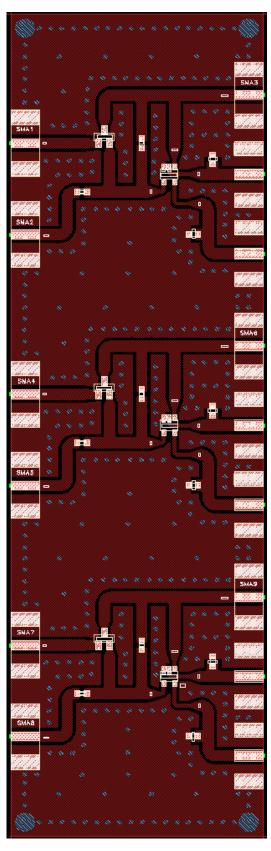

| Figure A.1: Top-layer PCB layout of the first design of the CSR Transmitter          | 122 |

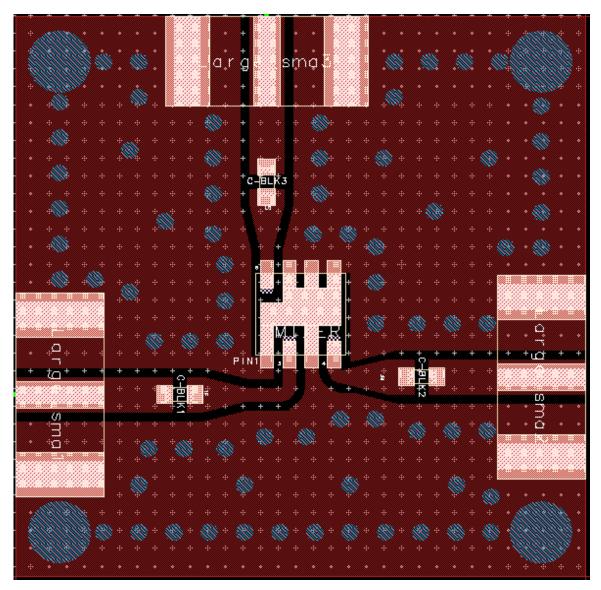

| Figure A.2: Top-layer PCB layout of 'Pulse Generation' stage of the second design    |     |

| of the CSR Transmitter                                                               | 123 |

| Figure A.3: Top-layer PCB layout of 'Amplitude Modulation' stage of the second       |     |

| design of the CSR Transmitter                                                        | 124 |

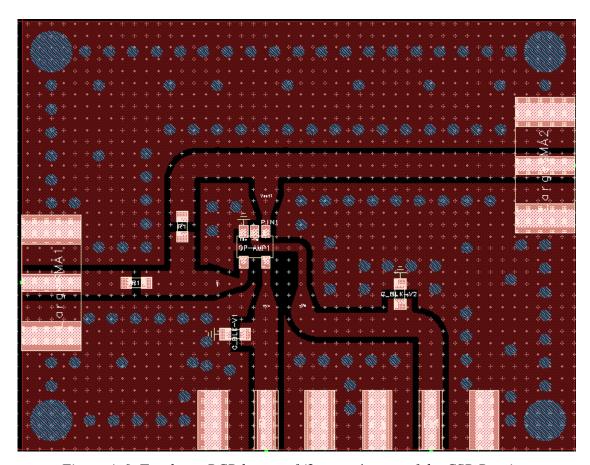

| Figure A.4: Top-layer PCB layout of 'Gated Pulse' stage of the second design of the  |     |

| CSR Transmitter                                                                      | 125 |

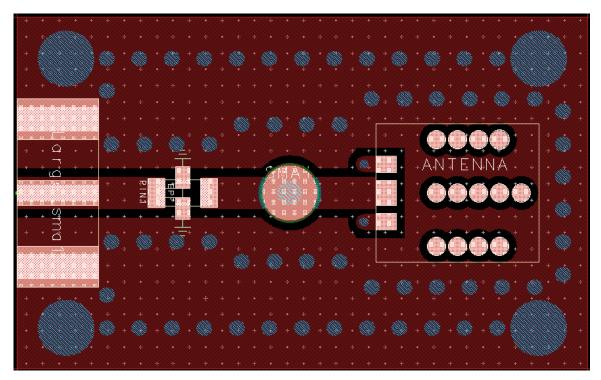

| Figure A.5: Top-layer PCB layout of BPF and Antenna of the second design of the      |     |

| CSR Transmitter                                                                      | 126 |

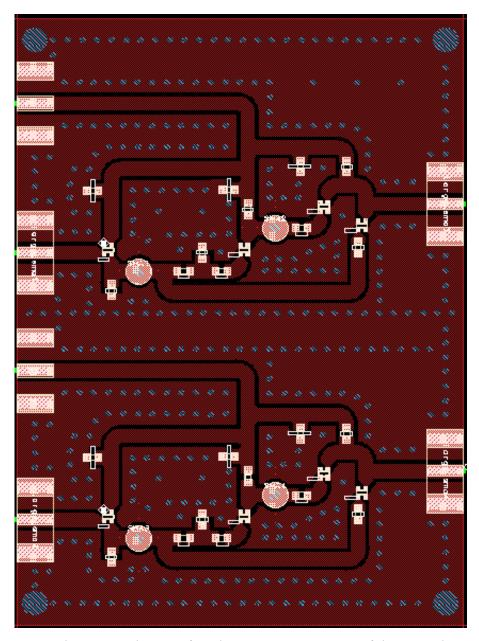

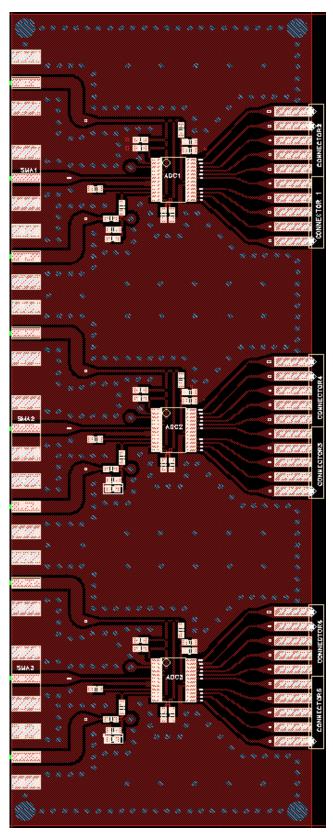

| Figure A.6: Top-layer PCB layout of 'Inverter' stage of the CSR Receiver             | 127 |

| Figure A.7: Top-layer PCB layout of Integrators of the CSR Receiver                  | 128 |

| Figure A.8: Top-layer PCB layout of ADCs of the CSR Receiver                         | 129 |

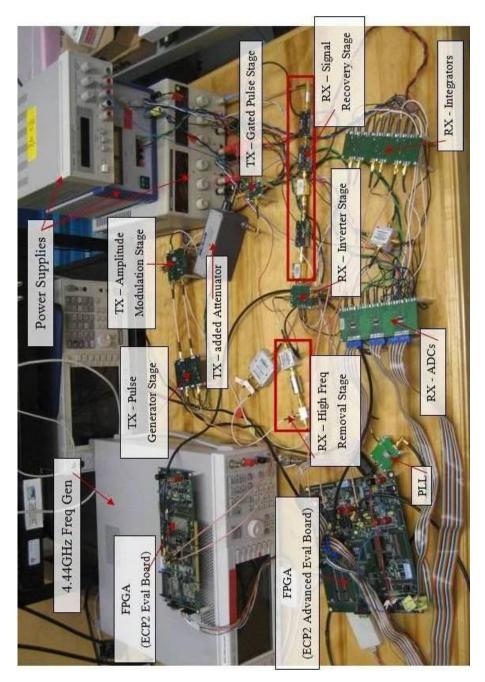

| Figure A.9: Picture of test set-up of CSR Transmitter and Receiver                   | 130 |

# LIST OF ABBREVIATIONS

AC Alternating Current

ADC Analog to Digital Converter

ADS Advanced Design Systems

ATTEN Attenuator

AWGN Additive White Gaussian Noise

BER Bit Error Rate

BJT Bipolar Junction Transistor

BPF Band-pass Filter

BW Bandwidth

CE Consumer Electronic

CMOS Complementary Metal–Oxide–Semiconductor

CSR Code-Shifted Reference

DC Direct Current

DCSR Differential Code-Shifted Reference

EIRP Equivalent Isotopic Radiated Power

FCC Federal Communications Commission

FPGA Field-programmable Gate Array

FSR Frequency-Shifted Reference

GPS Global Positioning System

HDR High data-rate

IC Integrated Circuit

IF Intermediate Frequency

IR Impulse-Radio

ISI Inter-Symbol Interference

ISM Industry, Scientific, and Medical (systems)

LDR Low data-rate

LNA Low Noise Amplifier

LO Local Oscillator

LPF Low-pass filter

MB Multi-band

MBOA Multiband OFDM Alliance

MPC Multipath Component

OFDM Orthogonal Frequency Division Multiplexing

PAPR Peak to Average Power Ratio

PC Personal Computer

PCB Printed Circuit Board

PLL Phase Lock Loop

PPR Pulse Repetition Rate

PSD Power Spectral Density

RF Radio Frequency

RMS Root Mean Square

S-FSR Slightly Frequency-Shifted Reference

SMT Surface-mount

SNR Signal-to-Noise Ratio

SRD Step Recovery Diode

TR Transmit Reference

UWB Ultra Wideband

VCXO Voltage Control Crystal Oscillator

VGA Variable Gain Amplifier

WLAN Wireless Local Area Network

## **ACKNOWLEDGMENTS**

First and foremost, I want to give thanks to God. He has given me the strength and courage to reach my goals, and surrounded me with wonderful family, friends and peers. Through Him, so many obstacles have been overcome and I have been able to achieve things that I would have otherwise thought impossible.

I would like to thank my Supervisor Dr. Zhizhang Chen for giving me the opportunity to research this topic. I truly appreciate his encouragement to learn as much as I can, and for his continued guidance and support in the completion of this project. I would also like to thank Dr. Hong Nie for agreeing to be my co-supervisor, and for his useful discussions and guidance.

I would like to extend my gratitude to InNova Corp of Nova Scotia Government of Canada for their financial support. Also thanks to Cape Breton University for kindly allowing us to borrow their oscilloscope.

I would like to thank the members of the RF and Wireless Lab for their support and kindness. Thanks to all the staff and professors within the ECE Department for enriching my experience at Dalhousie. Thanks to Dr. Munir Tarar for his technical advice and guidance. Also to Chen Wie, for working with me on this project, providing the programming of the FPGA to perform the coding and decoding of the DSCR signals.

Finally, I would like to thank my parents, Daniel and Clara Lowe, and my sister Jenai, for all their love, support, patience, and continued encouragement throughout my degree. This thesis is dedicated to them.

# **ABSTRACT**

The objective of this thesis is to present the design, implementation and testing of a Transmitter and Receiver for the use of the emerging Code-Shifted Reference (CSR) scheme for Impulse-Radio Ultra-Wideband (IR-UWB) systems.

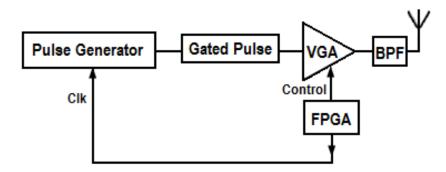

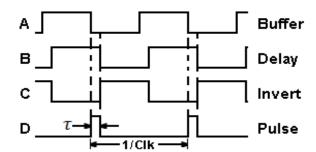

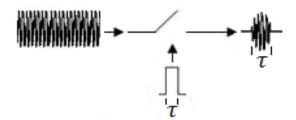

The transmitter is shown to generate impulses of duration 4ns at repetition rates of 20MHz. In order to avoid any interference with WLAN operating at 5GHz, it was decided to have the UWB system operate in the lower half of the UWB spectrum, from 3-5GHz, with a center frequency of 4.44GHz. After gating, the spectrum will consist of two 250MHz bands located at 4.44GHz+250MHz and 4.44GHz-250MHz, i.e. a 500MHz bandwidth centered at 4.44GHz; therefore meeting the 500MHz bandwidth requirement of UWB transmission. The impulses are encoded by means of amplitude modulation, according to information provided by the FPGA based on the differential CSR algorithm.

The transmitted coded-impulse-sequence is recovered by means of the CSR receiver, based on the general structure outlined in [1]. Band-pass filtering is performed to remove noise and interferences outside of the desired frequency band. Squaring and low-pass filtering is to remove the 4.44GHz, ultimately recovering the baseband signal originally produced by the impulse generator of the transmitter (with the amplitudes of the impulses being squared their original value). Integration is to detect the energy of the recovered signal. The FPGA performs the clock synchronization between the receiver clock and the transmitter clock by means of a phase-lock-loop (PLL). The data sequence is then extracted from the signal by means of the differential CSR algorithm.

# **CHAPTER 1: INTRODUCTION**

#### 1.1 MOTIVATION

Traditionally, the field of wireless communication has been dominated by transmission schemes based on conventional narrowband technology. The challenge faced by narrowband transmission results from its limited bandwidth, which has the direct effect of limiting the transmission capacity. Therefore narrowband systems are unable to accommodate the increasing need of higher data-rates in wireless communication applications.

Providing a solution to the problem of bandwidth limitation, Ultra-wideband (UWB) technology has recently received a significant amount of attention in the field of wireless communication. Although UWB is not a new concept, having been used for several years for military applications, the Federal Communications Commission's (FCC) approval of an unlicensed UWB spectrum for wireless communications has opened up new potentials in this field, sparking the interest of both industry and academia.

In comparison to narrowband transmission, UWB technology spreads the signal over a very wide range of frequencies by means of transmitting ultra-short duration pulses on the order of nanoseconds. This enables transmission speeds of several hundred Mbps, accommodating the high data-rate demands of current and future wireless systems. In addition to the advantage of higher data-rates, the reason for UWB's popularity in the wireless field lies in the many other benefits it offers, including low-cost, low transmit power, low complexity, low power consumption, and low probability of detection and interference.

Over the years, several implementation schemes for impulse-radio (IR) UWB systems have been presented. Most notably, these include methods such as Transmit Reference (TR) and Frequency-Shifted Reference (FSR), which have overcome the complexity of channel estimation by transmitting reference pulses to be used as a template for extracting the data pulse. In these methods, this reference pulse is separated from the data pulse by a shift in time and frequency respectively.

Recently, the scheme of Code-Shifted Reference (CSR) has been proposed for IR-UWB transmission [1]. In the proposed CSR scheme, rather than being separated by time (TR) or by frequency (FSR), the reference and data pulse sequences are separated by codes [1]. The CSR scheme overcomes the technical challenges encountered by other UWB systems, given that it does not require explicit channel estimation, a wideband delay element, or separation of reference and data pulse by analog carriers; as a result, it has reduced system complexity, and has been found to achieve better performance than the previous schemes [2].

Papers such as [2] have been published, analyzing the theoretical performance of CSR transmission in comparison to existing schemes such as the Rake Receiver, TR and FSR. However, to the best of our knowledge, there has yet to be research done in terms of the design and testing of a transceiver implementing and verifying the proposed Code-Shifted Reference (CSR) scheme. Therefore, this thesis aims to provide a design for the implementation of the transmitter and receiver for the CSR IR-UWB system, as well as provide test results and discussion on the performance of this system.

#### 1.2 THESIS OUTLINE

The organization of this thesis is as follows:

Chapter 2 provides a brief background to Ultra-wideband technologies. The definition and regulations of UWB transmission as set by the FCC are presented. This is followed by a discussion on the two types of UWB transmission, namely Impulse-Radio (IR) and Multi-band Orthogonal frequency-division multiplexing (MB-OFDM). Given that this thesis utilizes the method of Impulse-Radio transmission, emphasis on the characteristics of IR transmission is given; such as spectral amplitude, bandwidth and pulse shape. This Chapter also covers the advantages of IR-UWB technology, focusing on its ability to achieve high data-rates, the flexibility and trade-off between transmission distance and data-rate, as well as features of multipath immunity and low probability of detection and interception. Finally, a brief section is given on the applications of UWB technology, in specific, applications of high data-rate, short transmission distance (as this is the target for the system presented in this thesis).

Chapter 3 gives a brief introduction to schemes for implementing IR-UWB. This includes the methods of Rake Receiver, Transmit Reference (TR), Frequency-Shift Reference (FSR), and emerging Code-Shifted Reference (CSR). A brief discussion is given for each method, concluded by a section providing a performance comparison between CSR and the previous methods of Rake, TR and FSR.

Chapter 4 provides the first proposed CSR transmitter as was presented in [3]. This design was later altered, as it was found after implementation the system did not function as efficiently as desired, or as was expected, based on the simulation results. The design theory behind the function of the transmitter is presented, as well as the simulation results. The results obtained after implementation of the circuit are provided and compared to the simulation results. The overall performance of the transmitter is then discussed.

Chapter 5 presents the redesigned CSR transmitter. Design theory behind the function of each of the stages of the transmitter is given. The simulation results are presented and compared with the results obtained from the previous transmitter design (given in Chapter 4). The implementation results of this transmitter are also presented. These results are discussed and compared with the implementation results of the previous transmitter. The results are also compared with its own simulation results to verify that the performance was as expected.

Chapter 6 presents the CSR Receiver. As in the previous two chapters, the design theory of the receiver is given, followed by the simulation and implementation results obtained. Comparison and discussion is made between the expected (simulated) results and the results obtained after implementation and testing.

Chapter 7 provides some improvements that were made to the systems after initial testing had been performed on the CSR transmitter and receiver. These improvements were made to enhance the performance of the system, providing the optimal ratio between 'high' and 'low' pulse so that decoding performed by the receiver would have a better performance. The test results of the changes made to the implemented boards for both transmitter and receiver are presented and discussed in this Chapter.

Chapter 8 provides a conclusion to the thesis. This Chapter presents an overall summary of the thesis as well as some improvements that can be made to the system in the future. Further future work for the system is provided.

References are given at the end of the thesis; as well as an Appendix containing the PCB layouts for the transmitter and receiver boards, and photos of the test set-up of the implemented system.

# **CHAPTER 2:** BACKGROUND OF UWB

#### 2.1 UWB DEFINITION AND REGULATIONS

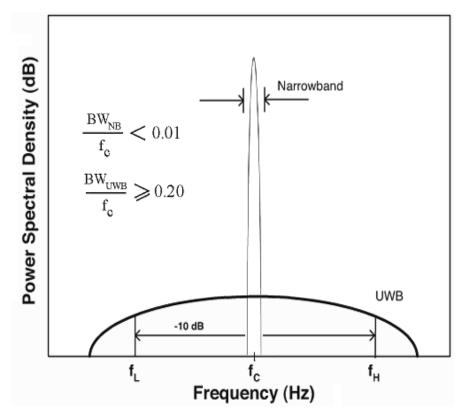

The FCC has defined a UWB system as any wireless scheme whose signals have a -10dB fractional bandwidth ( $B_f$ ) at least 20% higher than its center frequency ( $f_c$ ), or a -10dB absolute bandwidth (BW) greater than or equal to 500MHz [6]. The -10dB absolute bandwidth is defined as the frequency band bound by  $f_h$  and  $f_b$  which are the upper and lower frequency points 10dB below the highest radiated power of the complete transmission system (including the antenna). The fractional bandwidth ( $B_f$ ) can be expressed as [6]:

$$B_f = \frac{BW}{f_c} = 2\frac{f_h - f_l}{f_h + f_l} \tag{2.1}$$

where the center frequency  $f_c$  is defined as the average of  $f_l$  and  $f_h$ :

$$f_c = \frac{f_l + f_h}{2} \tag{2.2}$$

The definitions of fractional and absolute bandwidth are illustrated in *Figure 2.1*. This Figure clearly illustrates the comparison of fractional bandwidth between UWB and traditional narrowband communications. It can be seen that UWB transmission offers a spectral fractional bandwidth of twenty times that of traditional narrowband transmission.

Figure 2.1: Spectral Comparison of UWB and Narrowband Transmission [4]

Figure 2.1 also illustrates that UWB transmission has a far lower power spectral density (PSD) than narrowband. The approximate value of the PSD of a system is defined as:

$$PSD = \frac{P}{BW} \tag{2.3}$$

where P is the transmit power (Watts) and BW is the absolute bandwidth (Hz); therefore PSD is measured in W/Hz. Given this equation, it can be determined that for a fixed amount of power, we can either transmit with a large PSD value over a small frequency bandwidth or a small PSD value over a larger frequency bandwidth.

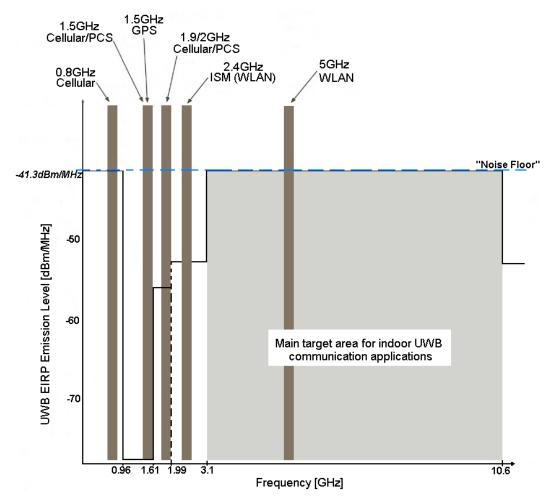

The reason that FCC specifies a very low PSD is due to the fact that UWB covers extremely large bandwidth that overlaps the transmission spectrums of many existing wireless narrowband systems. This poses a danger of signal interference between these systems and UWB transmissions. In order to avoid interference between UWB and other wireless systems, the FCC specified that the UWB maximum equivalent isotopic radiated power (EIRP) spectral density be -41.3dBm/MHz. The EIRP is defined as the theoretical

amount of power that the transmitter will emit, with the assumption that the transmitter is radiating equally in all directions.

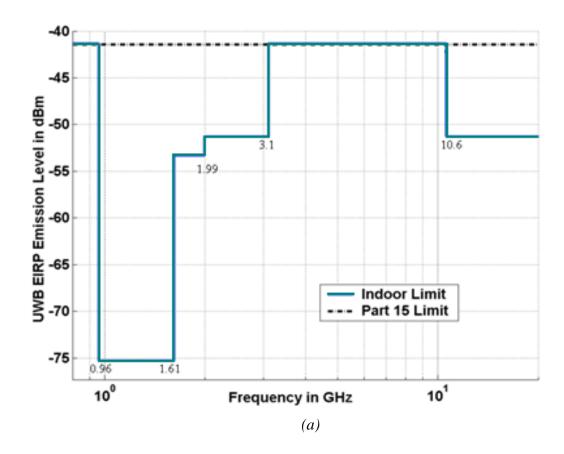

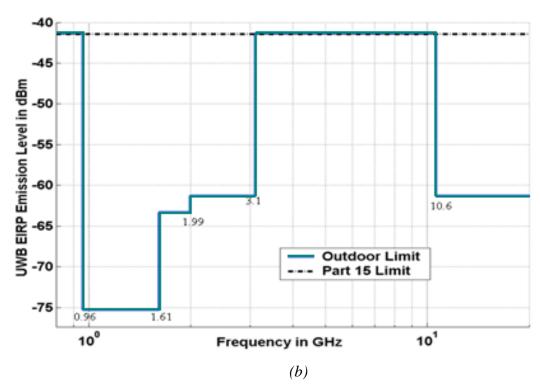

In the Report and Order issued in 2002 [6], the FCC allocated two separate frequency bands for UWB transmission: the first is the DC-960MHz band, mainly for lower datarate transmission (radar applications) [5] and the second is the 3.1-10.6GHz band (frequency band of interest for this research), reserved mainly for UWB communication systems. A spectral mask was defined for both indoor and outdoor UWB transmissions. These masks are given in *Figure 2.2a* and *Figure 2.2b*, respectively.

For a UWB system that utilizes the entire 7.5GHz of the available spectral band, the maximum allowable transmit-power would be approximately 0.56mW. Given these extreme limitations on the transmission power, UWB systems can be seen to operate at the noise floor of existing wireless narrowband systems, and therefore does not interfere with their performance as the systems will see the UWB transmission as merely noise.

Figure 2.2: FCC spectral mask for (a) indoor and (b) outdoor systems [4]

Figure 2.2 indicates that emission limits within the UWB spectrum are varied between specific frequency bands. These emission limits can be summarized in *Table 2.1* below.

Table 2.1: FCC emission limits for indoor and outdoor UWB transmission [7]

| Frequency (MHz) | Indoor<br>EIRP (dBm/MHz) | Outdoor<br>EIRP (dBm/MHz) |

|-----------------|--------------------------|---------------------------|

| 0-960           | -41.3                    | -41.3                     |

| 960-1610        | -75.3                    | -75.3                     |

| 1610-1990       | -53.3                    | -63.3                     |

| 1990-3100       | -51.3                    | -61.3                     |

| 3100-10600      | -41.3                    | -41.3                     |

| Above 1060      | -51.3                    | -61.3                     |

It should be noted that the maximum allowable power emissions between the frequency band 0.96-1.61GHz is extremely low (-75.3dBm/MHz). The reason for avoiding frequencies in this band is illustrated in *Figure 2.3*, i.e. to avoid interference with the many existing systems that operate at those frequencies, such as global positioning systems (GPS), cellular and military usage. This can also be considered a safety measure given that interference between systems such as aviation/military and GPS can prove detrimental. Therefore, the range of operation for UWB communications is specified to be between 3.1-10.6GHz, where the most probable interference is with Wireless Local Area Network (WLAN) systems. Even so, as a further precaution, many researchers have chosen to also avoid the frequencies occupied by WLAN. Therefore transmission can be chosen to operate in either the lower band (3.1-5GHz) or upper band (6-10.6GHz) of the 7.5GHz allocated for UWB communications [9].

Figure 2.3: Wireless systems operating in the same bandwidth as UWB [8]

#### 2.2 Types of UWB Transmission

In general, there are two common forms in which UWB signals are transmitted. These two forms are referred to as Multi-band Orthogonal Frequency Division Multiplexing (OFDM) and Impulse-Radio (IR) UWB. The approach chosen for this project was that of Impulse-Radio UWB. A brief explanation of each method is provided in the following subsections. Further detail regarding the advantages and characteristics of Impulse-Radio is provided in the following sub-sections, *Sections 2.3-2.5*, of this Chapter.

#### 2.2.1 Multi-band ODFM UWB

Multi-band OFDM (MB-OFDM) UWB employs at least two or more frequency bands, where each band complies with the FCC regulation that *BW*≥500MHz. In this way MB-OFDM aims to make use of the allotted UWB spectrum while adhering to the FCC requirements for minimum bandwidth. [10]

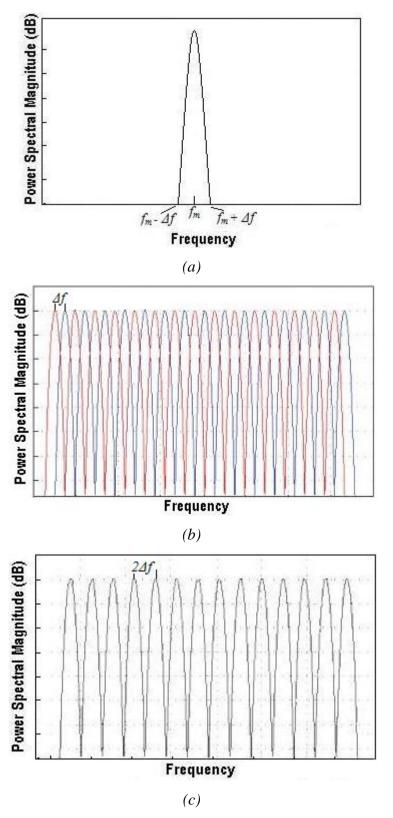

MB-OFDM can be described as the "parallel transmission of N symbols", where each symbol is used to modulate a different sub-carrier frequency,  $f_m$  [12]. In order for the N symbols to be effectively resolved by the receiver, orthogonality must be maintained between sub-carriers [12]. To achieve this, the equal spacing between sub-carriers must be at least  $\Delta f$  in the spectral domain, where  $\Delta f = 1/T_s$  and  $T_s$  is the time taken to transmit each symbol [12]. Figure 2.4 illustrates the instances where the sub-carriers are spaced at frequencies of  $\Delta f$  (Figure 2.4b) resulting in overlapping sub-carriers, and at  $2\Delta f$  (Figure 2.4c) resulting in sub-carriers that do not overlap. In both cases orthogonality is obtained between signals, due to the fact that the peak of one sub-carrier occurs when the other sub-carriers are at zero.

Figure 2.4: OFDM (a) original single-carrier, (b) multi-band with overlapping [7], and (c) multi-band without overlapping [7]

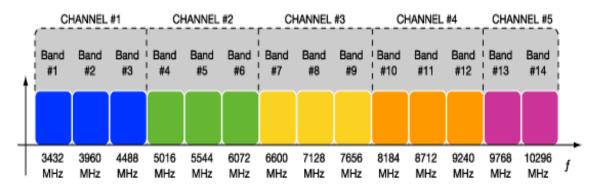

An alliance known as the MBOA (Multiband OFDM Alliance), proposed that the available 7.5GHz for UWB transmission be divided into 14 non-overlapping sub-bands of 528MHz [13]. These sub-bands are grouped into five Channels as shown in *Figure 2.5*. Channel 1, containing the first three sub-bands, is considered mandatory for UWB transmission. The other Channels are optional; therefore certain sub-bands can go unused to avoid interference with existing systems [13]. It should be noted that this is the MB-OFDM UWB plan for North America. This channel allocation differs in places such as Europe and Japan. [14]

Figure 2.5: MBOA MB-OFDM Channel allocation [14]

#### 2.2.2 Impulse-Radio UWB

The Impulse-Radio UWB (IR-UWB) method employs transmission by means of ultra short duration pulses on the order of nanoseconds. The width of these pulses determines the bandwidth the transmitted signal will occupy in the spectral domain. In this way a single narrow pulse can occupy the entire UWB spectrum. The pulses do not carry any information themselves, but are usually 'encoded' by means of amplitude, position or polarity modulation to represent the information to be transmitted. [10]

IR-UWB is discontinuous pulse transmission in time, where the UWB pulse sequence transmitted has a very low duty-cycle. This has an advantage over continuous transmission techniques in that the receiver is only required to function for a small duration of the cycle. The impact of interference from a continuous source is reduced

with IR-UWB. This is due to the fact that the interference will only have relevance when the receiver is trying to detect the signal. Given the very low duty-cycle, this is only for a very small fraction of each period. Between periods, the receiver simply has to 'listen' to the channel as it waits for the next pulse. [10]

#### 2.3 THE IR-UWB PULSE

In the case of IR-UWB, the pulse plays an extremely important role in signal transmission, as the characteristics of the generated pulse determine the spectral characteristics of the signal. Therefore in order to make best use of the spectral mask provided by the FCC, the characteristics of the UWB pulse must be carefully chosen.

This Section will cover the importance of the generated pulse characteristics, and the ways in which these time domain characteristics impact the spectral characteristics of the transmitted signal.

## 2.3.1 Pulse Spectral Bandwidth

The duration, or width, of the pulse will determine the bandwidth of the signal in the frequency domain. This is in relation to the fact that the inverse of the period of a signal is equivalent to its bandwidth, and vice-versa. In the case of an impulse, the inverse of the duration of the pulse,  $\tau$ , is equivalent to its spectral bandwidth, BW. In general, as a rule of thumb, it can be said that:

$$\frac{1}{\tau[sec]} \approx BW[Hz] \tag{2.4}$$

Given the above relation, it can be concluded that in order to achieve an extremely large bandwidth, the pulse duration must be small. For this reason, the widths of UWB pulses are designed to be on the order of nanoseconds in order to occupy spectral bandwidths of 500MHz up to several GHz.

#### 2.3.2 Pulse Spectral Amplitude

The transmit power, limited by the FCC spectral mask to a maximum of -41.3dBm/MHz, is dependent on the pulse repetition rate, *PRR*, (pulse/sec) and the amplitude of the pulses in the time domain [16]. The element actually being limited by these factors is the spectral amplitude of the signal such that:

$$V_f = V_t \left(\frac{\tau}{T}\right) \tag{2.5}$$

where  $V_f$  is the spectral amplitude of the main lobe in the frequency domain,  $V_t$  is the root-mean-square (RMS) amplitude of the pulse in the time domain,  $\tau$  is the width of the generated impulse, and T is the pulse rate (1/clock). [16]

Therefore, when considering the transmission of the pulse, if the PRR is low (i.e. *T* is large) then the pulses can have higher amplitude in the time domain. If the pulse rate is high, the pulses must have lower amplitudes in order to keep in accordance with the FCC emission limits.

## 2.3.3 Pulse Shape

The shape of the pulse is a key factor in determining how the signal energy will occupy the spectral domain, i.e. how effectively the pulse will make use of the allotted FCC spectral mask. Therefore this topic has been of great interest in designing a UWB pulse generator that will make the best use of the FCC spectral mask.

Generally, for IR transmission the shape of the pulse is not specifically defined. Any pulse whose spectral response fits the FCC spectral mask can be used. Within literature, pulse shapes used are typically the Gaussian pulse and its derivatives (e.g. monocycle,

doublet), Rayleigh monocycles, Manchester monocycles, or Hermite pulses [17]. Of these listed, the most common pulse shape used in UWB transmission is that of the Gaussian pulse due to its simplicity in generation.

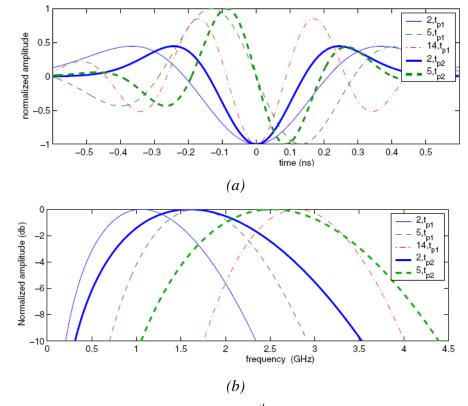

Examples of the waveforms of a Gaussian pulse and its derivatives in both the time and frequency domain are illustrated in  $Figure\ 2.6a$  and  $Figure\ 2.6b$  respectively, taken from [17]. From these Figures the spectral effects of changes made to the order (n) and the width  $(t_p)$  of the Gaussian pulse can be observed. First we will consider the effect of changing the order of the Gaussian pulse, while fixing the pulse width to a constant value. In this case we will refer to the spectral waveforms of  $Figure\ 2.6b$ ,  $2.t_{p2}$  and  $5.t_{p2}$ , where '2' and '5' correspond to the order of the Gaussian pulse and  $t_{p2}$  corresponds to the width. Comparing these two waveforms it can be seen that as the order of the Gaussian pulse is increased, the spectrum is shifted towards a higher frequency range, while the bandwidth of the spectrum remains relatively constant. We now consider the effect of changing the pulse width while keeping the order of the Gaussian pulse constant. Comparing the spectral waveforms of  $2.t_{p2}$  and  $2.t_{p1}$ , where the width of the pulse  $t_{p2}$  is less than  $t_{p1}$ , shows that as the width of the pulse is decreased, the bandwidth is increased. Also, in this case the spectrum is shifted slightly towards a higher frequency range. [17]

Figure 2.6: (a) Time domain waveforms of  $n^{th}$  order Gaussian waveforms, and (b) frequency spectrum of  $n^{th}$  order Gaussian waveforms [17]

Of the derivatives of Gaussian pulses, most literature favors the Gaussian monocycle (first derivative Gaussian) and Gaussian doublet (second derivative Gaussian) for UWB systems [18-23]. These pulses are easily generated and have zero DC components [24]. Although these pulses have a zero DC component, their spectra still goes down to very low frequencies, which are well below the minimum 3.1GHz of the UWB spectra. This is illustrated in *Figure 2.6b*, where the second order Gaussian doublet (*n*=2) does not have a DC component, but the spectra starts at a very low frequency. Whether the spectra of the doublet will be within the UWB spectral range depends on the width of the pulse. As stated before, the shorter the pulse duration, the wider the frequency range it can span. If the pulse width is small enough to span the UWB spectrum, some filtering is still required to remove the lower frequency components.

Given the performance of  $n^{th}$  order Gaussian pulses illustrated in *Figure 2.6*, papers such as [25] and [26] have argued that using a higher order Gaussian pulse is more effective,

as they are able to satisfy the FCC mask without the filtering required for first and second order Gaussian pulses. The only drawback is that it is more complicated to generate higher order Gaussian pulses. Other papers have suggested means of modulating a Gaussian-shaped pulse to shift the spectra upwards into the band of interest. For instance, [24] suggests this can be achieved by modulating the pulse with a stable local oscillator frequency. Others, such as [27] and [28], have suggested generating a sinusoidal Gaussian monocycle or one of its derivatives by means of implementing a 'gated function'. This will 'gate' a sinusoidal input by means of some nanosecond pulse to produce an impulse that resembles the shape of an  $n^{th}$  order Gaussian pulse.

#### 2.4 ADVANTAGES OF IR-UWB TECHNOLOGY

There are several features of IR-UWB signals which make them attractive for a wide range of wireless applications. Some of the major advantages of IR-UWB are presented in detail in the subsequent sub-sections.

#### 2.4.1 Large Capacity and High Data-Rate

The most notable characteristic of UWB signals is that of its extremely wide bandwidth. The benefits of large bandwidth can best be explained by means of Shannon's Capacity equation, which is expressed as:

$$C = B \log \left( 1 + \frac{s}{N} \right) \tag{2.6}$$

where C is the maximum channel capacity (bits/second), B is the channel bandwidth (Hertz), and S/N is the signal-to-noise ratio.

Shannon's capacity equation indicates that there are two factors which can improve the capacity of a channel: an increase in bandwidth, or an increase in the signal-to-noise ratio (SNR). This equation also shows that channel capacity will increase linearly with

bandwidth, but only logarithmically with signal power. Therefore, increasing the bandwidth will have a greater effect on the channel capacity than increasing the signal power. Given that UWB has an abundant amount of bandwidth, from Shannon's equation it can be seen that UWB systems can achieve high capacity (i.e. high data-rates) for wireless communications.

#### 2.4.2 Flexibility in Data Rate versus Transmit Distance

An interesting feature of UWB transmission is that it can be used for either "high data-rate short-link-distance" [7] transmission, or "low data-rate large-link-distance" [7] transmission. This flexibility can be explained in terms of the very low transmit power limitation placed on UWB signals. Given the low transmit power allowed, a UWB system can transmit one bit of information by means of several low-energy pulses. From general transmission theory, it is known that the greater the distance between the transmitter and receiver, the lower the throughput (data-rate) at the receiver end due to increased bit error rate (BER) and increased signal strength degradation. Using the relation that increased link-distance results in lower data-rates, in principle a trade-off can be made between the two quantities. The data-rate of the transmission can be adjusted by varying the number of pulses required to carry one bit of information. The more pulses required to transmit one bit of information, the lower the data-rate of the transmission, therefore the greater the achievable transmission distance, and vice-versa. [7]

## 2.4.3 Low Interference and Low Probability of Detection/Interception

The FCC has regulated the UWB spectrum so that, although it does overlap the spectrums of many other wireless systems due to its large bandwidth, it has a very low power spectral density of -41.3dBm/MHz. Therefore UWB systems operate at the noise floor of these other systems and do not interfere with their performance, as the systems will see the UWB signal as mere noise. As mentioned in *Section 2.1*, ensuring that UWB transmission will not interfere with systems sharing its spectrum is especially important

to aviation, military and GPS (occupying 0.96-1.61GHz), where interference with such systems can cause causalities among users.

The fact that UWB transmissions operate at basically the noise floor of other wireless systems also serves as a means transmission security. The very low power spectral density of UWB transmissions makes unintended detection and interception difficult. This property is of particular interest for military applications, such as covert communications and radar. [8]

## 2.4.4 Multipath Immunity

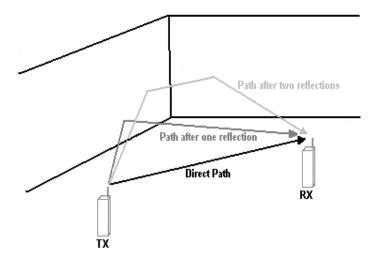

Multipath is the occurrence in which a signal is split into multiple paths as it travels from the transmitter to the receiver. This effect can be caused by a number of factors including reflection, absorption, diffraction, and scattering of the signal energy by objects in between the transmitter and the receiver. The paths will have different lengths, with each path having an arrival delay proportional to the path length; therefore they will arrive at the receiver at different times. This occurrence can be a particular problem in indoor environments as illustrated in *Figure 2.7* below. [8]

*Figure 2.7: Occurrence of multipath in an indoor environment [8]*

In general, if the multipath pulses do not overlap, then they can be resolved at the receiver. In other words, if the separation between multipath pulses is sufficient they can be distinguished from each other. The separation distance that is required between multipath components decreases as the width of the pulse decreases. Given that UWB pulses have extremely short widths (on the order of nanoseconds) it is easier for these pulses to be resolved at the receiver. In principle, through detecting resolvable multipath components (MPCs) one by one, the receiver is able to combine the energy from each MPC to increase signal gain and produce better system performance. [32]

#### 2.5 APPLICATIONS

Although UWB technology is fairly new to the field of wireless communications, its original use has several decades of application for military systems. Its use for military application is obvious from its characteristics of low probability of detection and interception, which allow for secure transmission. Over the years UWB technology has been implemented for the use of radar (automotive radar for collision avoidance), and imaging (ground-penetration-radar, through-wall-imaging, in-wall-imaging) [11]. Since the FCC authorized the unlicensed commercial use of the UWB spectrum in 2002, there has been a great interest in UWB's application to wireless communication. In terms of wireless communication, UWB transmission can be generally separated into categories: low data-rate (LDR) long-link-distance applications, and high data-rate (HDR) short-link-distance applications [11].

LDR mainly targets applications transmitting data at rates for 1Kbps-10Mbps, with distances greater than 10m. These applications are usually used for sensor networks, where very small volumes of data are transmitted over relatively large distances. [11]

The interest of this thesis is UWB's application for HDR short-distance transmission. HDR applications target data-rates between 100Mbps-1Gbps, with distances ranging between 1-10m. The need for high data-rate transmission is of particular interest to applications within the areas of Personal Computer (PC), Mobile, and Consumer Electronics (CE). Applications for these groups are usually for indoor use within a single room. These groups require high data-rates for the use of purposes such as:

- File Transfer: Point-to-point transfer of files such as audio, video, or image files (e.g. loading audio files onto a portable music player). Also network communications (e.g. several computers can send word-documents to a single printer). [11]

- Asynchronous Communication: Transmission of an ongoing, "intermittent stream" of blocks of data (e.g. communication between wireless keyboard or mouse and a PC).

[11]

- Audio or Video Streaming: Transmission of a continuous stream of data at a constant rate (e.g. video transfer between DVD player and television). In this case, data is usually considered to be consumed in real-time by the user; else it may be more effective to use 'File Transfer' instead. [11]

As was mentioned previously, UWB has the potential of achieving very high data-rates according to Shannon's Equation, up to several Gbps. The data-rates of UWB can potentially reach rates that are far greater than that achieved by conventional narrowband systems; therefore offering promising solutions for current and future wireless applications.

# CHAPTER 3: Introduction to Code-Shifted Reference (CSR)

#### 3.1 Previous Implementation Schemes for IR-UWB

#### 3.1.1 Rake Receiver

A common receiver structure is that of the Rake Receiver, also called the all-rake (A-rake) [7]. The Rake Receiver is able to combine the received signal energy in all of the multipath components (MPCs) of the signal, which in turn will increase the signal-to-noise ratio (SNR) and improve the performance of the system. The general structure of the Rake Receiver, *Figure 3.1*, requires that a detecting finger be available for each resolvable MPC. Each of these detecting fingers requires channel estimation, multipath acquisition, and tracking operations in order to match the amplitude, phase and delay of each MPC [1].

Figure 3.1: General Rake receiver structure (with 2 MPCs) [30]

A more practical implementation of the Rake Receiver is known as the Selective Rake Receiver (S-rake) [7], which only combines those MPCs with the strongest energies. This is far less complex than the A-rake receiver, as less detecting fingers are required, due to the reduced number of MPCs to capture. However, the S-rake receiver trades off complexity for performance [7]. A comparison between the MPC acquisition of the A-rake and S-rake receivers is given the *Figure 3.2* below, where *L* denotes the number of MPCs combined by the receiver.

Figure 3.2: Comparison of the principles behind the A-rake (a) and (b) S-rake [31]

As was stated previously in *Section 2.4*, one of the main advantages of UWB signals is their immunity to multipath fading. Within a multipath environment, the received IR-UWB signal may consist of a large number of resolvable MPCs. Therefore, even when the S-rake receiver is considered for UWB transmission, the complexity and cost needed to resolve these MPCs can be high due to the large number of detecting fingers, and the

channel estimation, multipath acquisition, and tracking operations required for each finger.

#### 3.1.2 Transmit Reference Receiver

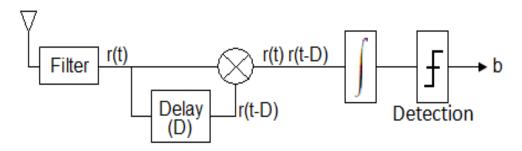

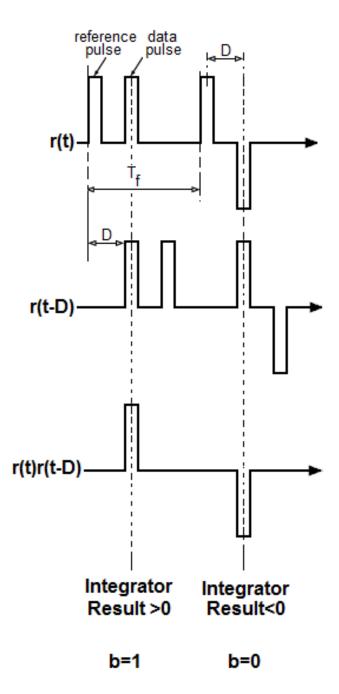

In order to eliminate the need for channel estimation, a method known as the Transmit Reference (TR) Receiver was introduced. This method simultaneously transmits a modulated data pulse and un-modulated reference pulse, which are separated by a delay, D, known by both the transmitter and receiver. Transmission is organised into frames, where each frame is of duration  $T_f$  and consists of a reference pulse followed by a data pulse. As long as the delay between these two pulses is significantly smaller than the channel coherence time (i.e. the minimum time before the channel will become uncorrelated with its previous state), the two pulses can be assumed to suffer the same distortion and multipath fading as they pass through the wireless channel [35].

Figure 3.3: General TR receiver structure [36]

The general structure of the TR receiver is illustrated in *Figure 3.3*. The received signal is delayed by the known delay element, *D*. In this way the reference pulse is used as a template to extract the data pulse. *Figure 3.4* shows the detection procedures of the TR receiver.

Figure 3.4: TR receiver detection procedure

One of the main challenges of the TR system is the implementation of a delay element with ultra-wide bandwidth, which is difficult to realise physically in an integrated circuit [36].

#### 3.1.3 Frequency Shifted Reference

Another scheme that has arisen for UWB transmission is Frequency-Shifted Reference (FSR), which aims to separate the data pulse and reference pulse in the frequency domain rather than the time domain. The motivation behind FSR is that implementation of a frequency shift for a wideband signal is simpler to achieve than the implementation of a wideband delay for the same signal [36]. We recall from the TR method that in order to effectively use the reference pulse as a template for the data pulse, both pulses must undergo the same channel distortion and fading; i.e. the delay time between the two pulses must be significantly less than the coherence time of the channel. For the FSR scheme this constraint becomes that the frequency offset ( $f_0$ ) between the reference and data pulse must be much smaller than the coherent bandwidth of the channel [36].

In [36], the method of Slightly Frequency-Shifted-Reference Receiver is suggested to satisfy the above constrain. To explain this method, transmission can be considered to be in the terms of frames and symbols:

$$T_s = N_f T_f \tag{3.1}$$

where  $T_s$  is the time period per symbol,  $N_f$  is the number of frames where there is one pulse per frame, and  $T_f$  is the time period per frame. A reference pulse sequence and one or more data pulse sequences are simultaneously transmitted; where each data pulse sequence is shifted by a specific frequency offset [36].

In order to ensure orthogonality between the reference pulse sequence and the data pulse sequences, the orthogonality is ensured over each symbol period, rather than by frame period, therefore [36]:

$$f_{offset} = \frac{1}{N_f T_f} = \frac{1}{T_s} \tag{3.2}$$

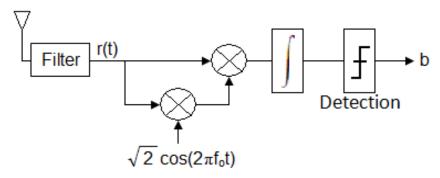

The general structure of the FSR receiver when only one data sequence is transmitted is shown in *Figure 3.5*. The frequency offset,  $f_o$ , is the same offset that was used to shift the data sequences before transmission. On the receiver side this offset will shift the

reference pulse sequence so that it may be used as a template to extract the information from the data pulse sequences.

Figure 3.5: General FSR receiver structure [36]

Due to the analog frequency offsets employed in the FSR scheme, the performance of the system can be affected by frequency errors caused by oscillator mismatch, phase errors caused by multipath fading, and amplitude errors caused by nonlinear amplifiers [1]. Therefore the reference pulse sequence may not provide a perfect template for the data pulse sequence.

# 3.2 CODE-SHIFTED REFERENCE (CSR)

Recently proposed is that of the Code-Shifted Reference (CSR) scheme for the IR-UWB Receiver. In the CSR scheme, rather than being separated by time (TR) or by frequency (FSR), the reference and data pulse sequences are separated by codes [1].

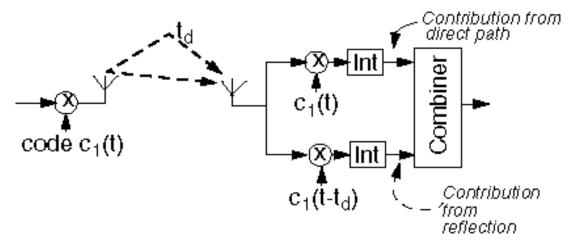

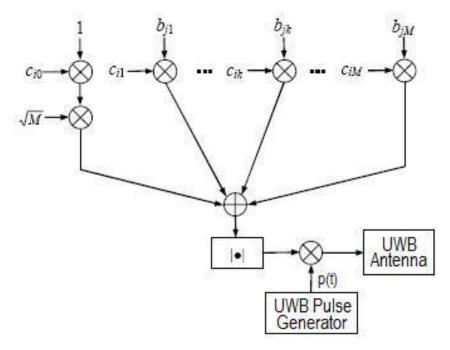

Figure 3.6: General CSR transmitter structure [1]

On the transmitter side of the CSR system, a reference pulse sequence and one or more data pulse sequences are transmitted simultaneously. The general structure of the CSR transmitter is shown in *Figure 3.6*. This structure has been defined mathematically in [1] as:

$$x(t) = \sum_{j=-\infty}^{\infty} \sum_{i=0}^{N_f - 1} p[t - (jN_f + i)T_f] |\sqrt{M}c_{i0} + \sum_{k=1}^{M} b_{jk}c_{ik}|$$

(3.3)

where p(t) is the impulse of duration  $T_p$ , produced by the UWB generator;  $N_f$  is the number of frames transmitted where there is one pulse per frame and each frame duration is  $T_f$ ;  $b_{jk}e\{1,-1\}$  is the  $k^{th}$  information bit that was transmitted during the  $j^{th}$   $N_fT_f$  time period [1];  $c_{ik}e\{1,-1\}$  is the  $i^{th}$  bit of the  $k^{th}$  shifting-code; M is the number of information bits that will be transmitted simultaneously by means of  $N_f$  frames of UWB pulses [1].

It should be noted that for  $N_f = 2^N$  frames at most  $M=2^{N-1}$  information bits can be transmitted [1]. For M bits transmitted there will be  $2^{N-1}+1$  or M+1 shifting codes that will separate the reference pulse sequence from the data pulse sequences. These codes will be orthogonal, i.e. have zero-cross correlation, and will have a length of  $2^N$ .

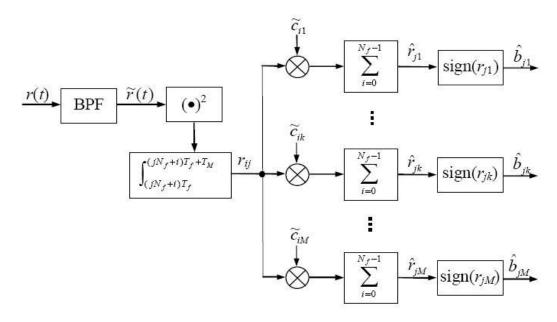

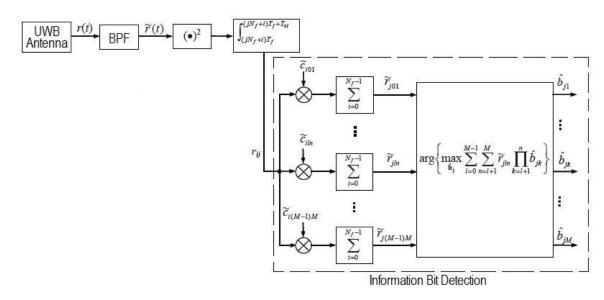

On the receiver side of the CSR systems, M (=2<sup>N-1</sup>) orthogonal detecting codes of length  $2^N$  are used to extract the information from the data sequence. The general structure of the CSR receiver is illustrated in *Figure 3.7*.

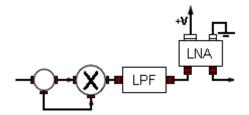

Figure 3.7: General CSR receiver structure [1]

Referring to Figure 3.7, filtering is performed to remove any noise and interference beyond the desired signal band, followed by a square unit and then integrated from  $(jN_f+i)T_f$  to  $(jN_f+i)T_f+T_M$  to obtain  $r_{ij}$ . The value of  $T_M$  varies from  $T_p$  in an additive white Gaussian noise (AWGN) channel to  $T_f$  in a multipath channel with severe delay spread [1]. Although a larger value of  $T_M$ , will result in the collection of more signal energy distributed in different MPCs, this also results in added noise and interference. [1]

The signal,  $r_{ij}$ , is correlated with the M detection codes and then each result is summed independently. The sign of the results of these summations will determine whether the received information bits will be detected as logic '1' or '0', defined in [1] as:

$$\widehat{b_{jk}} = \frac{1 \text{ if } sign(r_{jk}) > 0}{0 \text{ if } sign(r_{jk}) < 0}$$

(3.4)

#### 3.2.1 Differential Code-Shifted Reference (DCSR)

The CSR scheme is able to eliminate some of the issues regarding the complexity of the TR scheme and the performance degradation of the FSR scheme. But the CSR system, like the TR system, spends half of its power transmitting the reference pulse sequence [2]. Therefore the CSR system, although having reduced implementation complexity when compared to the TR system, cannot achieve better BER performance than the TR system. In order to improve system performance, the CSR scheme was extended to the differential CSR (DSCR) as presented in [37]. This performance improvement is achieved by reducing the amount of power used to transmit the reference pulse sequence [37].

The DSCR method makes use of the fact that the CSR scheme can transmit multiple data pulse sequences simultaneously, where each data pulse sequence bears one information bit. In the DCSR scheme, the information bits are differentially encoded so that one data pulse sequence can be used as a reference for another data pulse sequence. Therefore, when M bits are transmitted simultaneously, the amount of power used to transmit the reference pulse sequence can be reduced from  $\frac{1}{2}$  to  $\frac{1}{(M+1)}$ . [37]

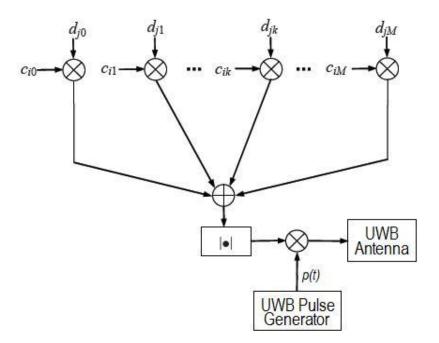

Figure 3.8: General DCSR transmitter structure [37]

The general structure of the DCSR transmitter is shown in *Figure 3.8*. This structure has been defined mathematically in [37] as:

$$x(t) = \sum_{j=-\infty}^{\infty} \sum_{i=0}^{N_f - 1} p[t - (jN_f + i)T_f] |\sum_{k=0}^{M} d_{jk} c_{ik}|$$

(3.5)

where p(t) is the impulse of duration  $T_p$ , produced by the UWB generator;  $N_f$  is the number of frames transmitted where there is one pulse per frame and each frame duration is  $T_f$ ,  $c_{ik}e\{1,-1\}$  is the  $i^{th}$  bit of the  $k^{th}$  shifting-code; M is the number of bits that will be transmitted simultaneously by means of  $N_f$  frames of UWB pulses [37];  $d_{jk}$  is the  $k^{th}$  differentially encoded information bit that was transmitted during the  $j^{th}$   $N_fT_f$  time period, defined in [37] as:

$$d_{jk} = \begin{cases} 1 & k = 0\\ \prod_{l=1}^{k} b_{jl} & \forall k \in \{1, 2, \dots, M\} \end{cases}$$

(3.6)

where  $b_{jl}e\{1,-1\}$  is the  $l^{th}$  information bit that was transmitted during the  $j^{th}$   $N_fT_f$  time period [37].

For DCSR, the number of information bits that can be transmitted in  $N_f$ (=2<sup>N</sup>) frames is determined by M(M+1)/2≤2<sup>N</sup>-1. For example, given:  $N_f$ =4, M=2;  $N_f$ =8, M=3;  $N_f$ =16, M=5. For M bits transmitted there will be M+1 orthogonal shifting codes that will separate the reference bit from the data bits, where the length of each code equal to  $N_f$ .

Take the following example:

Number of frames =  $N_f$  = 4,

Number of Bits = M = 2,

Number of shifting codes required = (M+1) = 3, Code length = 4

Bits to transmit:  $b_1$ =1,  $b_2$ =-1

$$d_{i0} = 1$$

$$d_{il} = b_{il} = 1$$

$$d_{i2}$$

=  $(b_{i1})(b_{i2})$  =  $(1)(-1)$  = -1

Orthogonal shifting codes:  $c_0$ =[1 1 1 1],  $c_1$ =[1 -1 1 -1],  $c_2$ =[1 1 -1 -1]

$$(d_0)(c_0) = 1 \times [1 \ 1 \ 1] = [1 \ 1 \ 1]$$

$$(d_1)(c_1) = 1 \times [1 \ -1 \ 1 \ -1] = [1 \ -1 \ 1 \ -1]$$

$$(d_2)(c_2) = -1 \times [1 \ 1 \ -1 \ -1] = [-1 \ -1 \ 1 \ 1]$$

$$[1 \ -1 \ 3 \ 1] \rightarrow [1 \ -1 \ 3 \ 1] \rightarrow [1 \ 1 \ 3 \ 1]$$

Therefore the pulse sequence transmitted will be of the form:

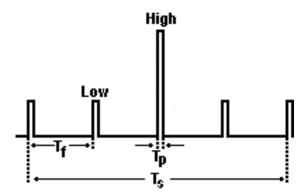

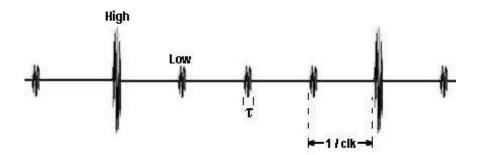

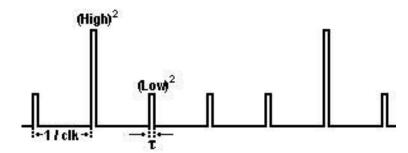

Figure 3.9: DCSR Transmitter Example Results

The front end of the receiver for the DSCR scheme, as shown in *Figure 3.10*, is the same as that for CSR: a BPF to remove noise and interference beyond the desired signal band, followed by a square unit and then integration from  $(jN_f+i)T_f$  to  $(jN_f+i)T_f+T_M$  to obtain  $r_{ij}$ . The only difference is that in the DCSR scheme, for M+1 shifting codes, since the multiplication of these codes can have M(M+1)/2 combinations, M(M+1)/2 orthogonal detection codes are required in order to detect the transmitted information bits [37].

Figure 3.10: General DCSR receiver structure [37]

Continuing with the example used to explain the DCSR transmitter, for the information detection block of *Figure 3.10*:

r<sub>ij</sub>=[1 1 9 1] (squared amplitudes of transmitted signal)

Number of shifting codes required = M(M+1)/2=3, Code length = 4

Orthogonal detection codes:  $c_{01}=[1 -1 1 -1]$ ,  $c_{02}=[1 1 -1 -1]$ ,  $c_{12}=[1 -1 -1 1]$

$$\begin{aligned} &(r_{ij})(c_{01}) = & [1 \ 1 \ 9 \ 1] \times [1 \ -1 \ 1 \ -1] & = & [1 \ -1 \ 9 \ -1] \\ &(r_{ij})(c_{02}) = & [1 \ 1 \ 9 \ 1] \times [1 \ 1 \ -1 \ -1] & = & [1 \ 1 \ -9 \ -1] \\ &(r_{ij})(c_{12}) = & [1 \ 1 \ 9 \ 1] \times [1 \ -1 \ -1 \ 1] & = & [1 \ -1 \ -9 \ 1] \end{aligned}$$

The information bits are determined by means of the following decision rule for joint detection [37]:

$$arg\left\{max_{b_{j}}\sum_{l=0}^{M-1}\sum_{n=l+1}^{M}r_{jln}\prod_{k=l+1}^{n}b_{jk}\right\}$$

(3.7)

Given M=2 and for j=1,

$$\sum_{l=0}^{M-1} \sum_{n=l+1}^{M} r_{jln} \prod_{k=l+1}^{n} b_{jk} = \sum_{l=0}^{1} \sum_{n=l+1}^{2} r_{ln} \prod_{k=l+1}^{n} b_{k}$$

$$= \sum_{n=1}^{2} r_{0n} \prod_{k=1}^{n} b_{k} + \sum_{n=2}^{2} r_{12} \prod_{k=2}^{2} b_{k} = r_{01}b_{1} + r_{02}b_{1}b_{2} + r_{12}b_{2}$$

To find  $arg\{max_b(r_{01}b_1 + r_{02}b_1b_2 + r_{12}b_2)\}$ , means to find the value of bit  $b_k$ , that will result in the maximum for the previously calculated summations,  $r_{ln}$ . In this example the maximum will be +8.

$$r_{01} = +8$$

$\rightarrow$   $r_{01}b_1 = 8$   $\rightarrow$   $b_1 = 1$

$r_{02} = -8$   $\rightarrow$   $r_{02}b_1 b_2 = 8$   $\rightarrow$   $b_1 b_2 = -1$

$r_{12} = -8$   $\rightarrow$   $r_{12}b_2 = 8$   $\rightarrow$   $b_2 = -1$

#### 3.3 PERFORMANCE COMPARISON

The CSR scheme offers advantages over the TR and FSR schemes. Since the data pulses and reference pulse are shifted by means on code rather than time, a wideband delay element is not required; therefore system complexity is reduced when compared with the TR system. Also since digital codes are employed rather than analog carriers to provide the separation between the reference and data pulse sequences, the CSR scheme is able to avoid most of the performance degradation that occurs in the FSR scheme due to errors in frequency, amplitude and phase. [1]

A theoretical analysis of the performance of the CSR scheme compared to other schemes was recently presented in [2]. Also performance comparison between the DCSR and the CSR/TR/FSR schemes was presented in [38]. It should be noted that in these papers comparison on the performance of the systems was made assuming that no inter-pulse interference existed.

The bit error rate (BER) of the CSR receiver in a multipath environment was found as [2]:

$$BER_{CSR} = Q\left(\frac{\sqrt{M}\alpha E_b}{\sqrt{2M\alpha E_b N_0 + N_0^2 (f_H - f_L) N_f T_M}}\right)$$

(3.8)

where  $E_b$  is the received energy per information bit,  $N_o$  is the single-side power spectral density of AWGN, M is the number of information bits transmitted,  $(f_h - f_l)$  is the bandwidth of the UWB signal,  $N_f$  is the number of frames transmitted,  $T_m$  is a time value used in receiver integration (varies from the value of pulse duration,  $T_p$ , in an AWGN channel to the value of frame duration,  $T_f$ , in a multipath channel with severe delay spread [1]), and  $\alpha$  is a constant value ranging from (0,1] according to  $T_m$  ( $\alpha$ =0 for  $T_m$ =0 and  $\alpha$ =1 for  $T_M$ = $T_f$ ) [38].

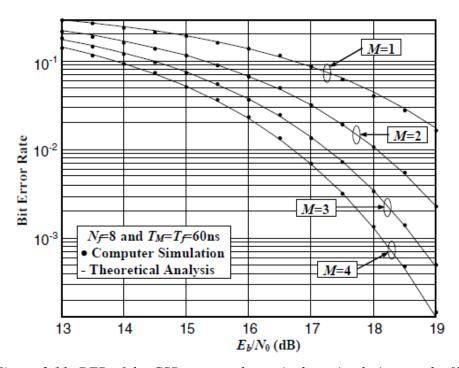

Computer simulation for the BERs of the CSR system as a function of  $E_b/N_o$  was performed in order to verify the theoretically calculated results [2]. These results illustrated in *Figure 3.11* were simulated under the conditions that  $T_f$ =60ns to ensure that inter-pulse interference would not exist, and  $T_M$ = $T_f$  so that  $\alpha$  is fixed at 1 [38].

Figure 3.11: BER of the CSR system: theoretical vs. simulation results [2]

From *Figure 3.11* it can be seen that the simulated results match closely with what are predicted by the theoretically analysis. Also for a fixed number of frames (one pulse per frame) and fixed frame duration, it was found that the BER of the CSR system improved as more information bits were transmitted simultaneously, i.e. for larger values of *M*.

The BER of the DCSR receiver in a multipath environment was found as being bounded by [38]:

$$BER_{DCSR} < 2Q\left(\sqrt{\frac{32(\alpha E_b)^2}{60\alpha E_b N_0 + 9N_f N_0^2 (f_H - f_L) T_M}}\right), \quad for \ M = 2$$

(3.9)

$$BER_{DCSR} < 2Q\left(\sqrt{\frac{27(\alpha E_b)^2}{48\alpha E_b N_0 + 4N_f N_0^2 (f_H - f_L) T_M}}\right) + 2Q\left(\sqrt{\frac{9(\alpha E_b)^2}{12\alpha E_b N_0 + N_f N_0^2 (f_H - f_L) T_M}}\right)$$

$$, for M = 3 \qquad (3.10)$$

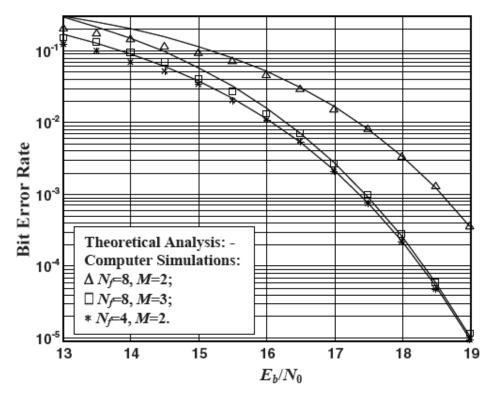

In the same way, computer simulation of the DCSR BER as a function of  $E_b/N_o$  was performed [38]. The results illustrated in *Figure 3.12* were also simulated under the conditions that  $T_f$ =60ns to ensure that inter-pulse interference would not exist, and  $T_M$ = $T_f$  so that  $\alpha$  is fixed at 1 [38].

Figure 3.12: BER of the DCSR system: theoretical vs. simulation results [38]

As was the case with CSR, it can be seen that for a fixed number of frames of fixed duration, as the number of bits transmitted simultaneously increases the performance of the DCSR system improves. This Figure also shows that if the frame to bit ratio is reduced, (4:2 as opposed to 8:2) the performance is also improved.

For the performance comparison of the DSCR and CSR systems with the FSR and TR systems, [2] provided the following equations for the BER of the FSR system (under AWGN environment) and the TR system (under multipath environment):

$$BER_{TR} = Q\left(\frac{\alpha E_b}{\sqrt{2\alpha E_b N_0 + 2N_0^2 (f_H - f_L) T_M}}\right)$$

(3.11)

$$BER_{FSR} = Q\left(\frac{\sqrt{M}E_b}{\sqrt{(2M+1/2)E_bN_0 + N_0^2(f_H - f_L)N_f T_f}}\right)$$

(3.12)

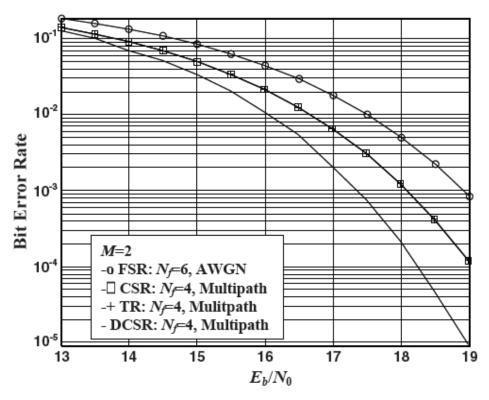

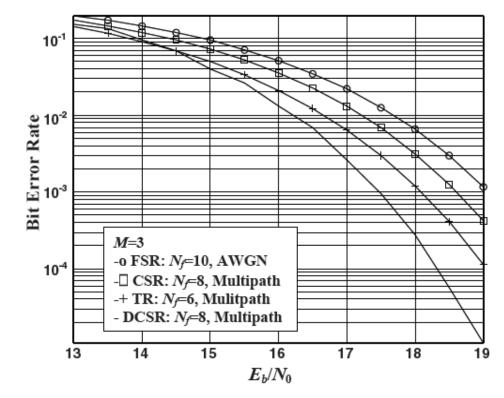

Using these equations and the BER equations derived for DCSR and CSR, comparison was made between the systems for instances where M=2 and M=3 as shown in *Figure 3.13* and *Figure 3.14* respectively.

Figure 3.13: BER comparison between DCSR, CSR, FSR and TR, M=2 [38]

Figure 3.14: BER comparison between DCSR, CSR, FSR and TR, M=3 [38]

Referring to the cases presented in these Figures, the FSR system has the worst performance, while the DCSR system has the best performance. For the FSR system, the number of bits that can be transmitted simultaneously is limited by the number of analog carriers available [2]. For  $N_f$ =6, as shown in *Figure 3.13*, there are only two analog carriers available, and M can only be '1' or '2' [2]. Therefore the highest achievable bit-to-pulse ratio ( $M/N_f$ ) for the FSR system when  $N_f$ =6 is 1/3 (or 2/6) [38]. Comparing this result to the other systems shown in *Figure 3.13*, their highest achievable bit-to-pulse ratio is  $M/N_f$ =½ (or 2/4). When M=3, the FSR system requires  $N_f$ =10, while the TR system requires  $N_f$ =6. In general the FSR system will achieve a bit-to-pulse ratio of less than ½, while the TR system will achieve a bit-to-pulse ratio equal to ½. For the CSR and DSCR systems, the bit-to-pulse ratio can be up to ½ and has the flexibility to transmit less than ½ as shown in *Figure 3.14* where 3 bits are transmitted simultaneously within 8 frames, although a max of 4 bits could have been transmitted with 8 frames.

From Figure 3.13 it can be seen that for  $M/N_f=1/2$ , the CSR system can achieve the same performance as the TR system and no better [2]. Both schemes use half of the available power to transmit the reference pulses. Recall that DCSR scheme was proposed as an extension of the CSR scheme in order to improve system performance by reducing the power to transmit the reference pulses from  $\frac{1}{2}$  to  $\frac{1}{M+1}$  [37].

In the CSR scheme the power required for the reference pulses is set as  $(\sqrt{M})^2$ , and for each data bit it is  $(1)^2$ ; therefore the reference power to total power can be expressed as:

$$\frac{(ref\_amplitude)^2}{(ref\_amplitude)^2 + \sum (data\_amplitude)^2} = \frac{\left(\sqrt{M}\right)^2}{\left(\sqrt{M}\right)^2 + (M \times (1)^2)} = \frac{M}{M + M} = \frac{1}{2}$$

(3.13)

In the DSCR scheme, the power required for the reference pulses has been reduced to  $(1)^2$ , due to the differentially encoded data pulse sequences acting as references for other data pulse sequences. Therefore *Equation 3.13* becomes:

$$\frac{(ref\_amplitude)^2}{(ref\_amplitude)^2 + \sum (data\_amplitude)^2} = \frac{(1)^2}{(1)^2 + (M \times (1)^2)} = \frac{1}{M+1}$$

(3.14)

Given the previous comparisons it can be concluded that the advantages of high bit-topulse ratio and reduced reference power enable the DSCR scheme to achieve better BER performance than the CSR, FSR, and TR schemes [38].

In terms of sensitivity to noise and interference, the FSR scheme is more sensitive than TR, CSR and DSCR [2]. This is due to that fact that the integration time of the FSR receiver must be fixed at  $T_f$  (frame duration), whereas in the case of the CSR, DCSR and TR schemes, the integration time can vary between  $T_p$  (pulse duration) in an AWGN channel and  $T_f$  (frame duration) in a multipath delay channel with sever delay spread [2]. The larger the integration value  $(T_f > T_p)$ , although more signal energy can be collected from the resolvable MPCs, it will also add more noise and interference [1].

Another issue for comparison is that of peak-to-average-power-ratio (PAPR):

$$PAPR = \frac{|A_{peak}|}{A_{rms}} = \frac{|A_{peak}|}{\sqrt{\frac{\sum_{i=1}^{M} (A_i)^2}{M}}}$$

(3.15)

Independent of the number of bits transmitted (M), the TR scheme is able to achieve PAPR=0dB, given that all the pulses have the same amplitude:

$$PAPR_{TR} = \frac{|A|}{\sqrt{\frac{M(A)^2}{M}}} = \frac{A}{A} = 1$$

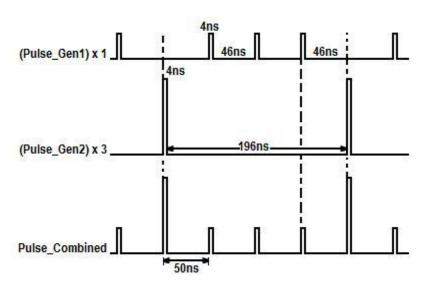

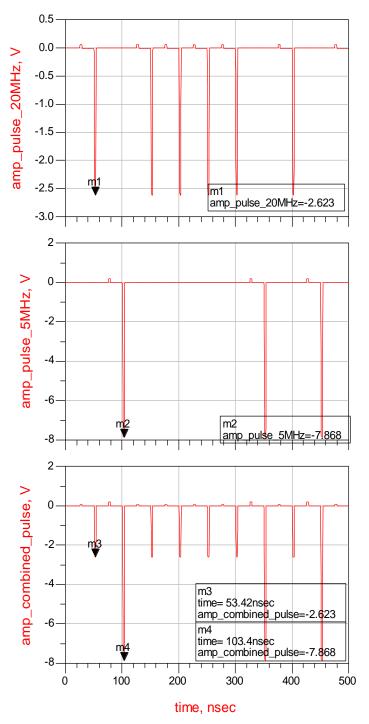

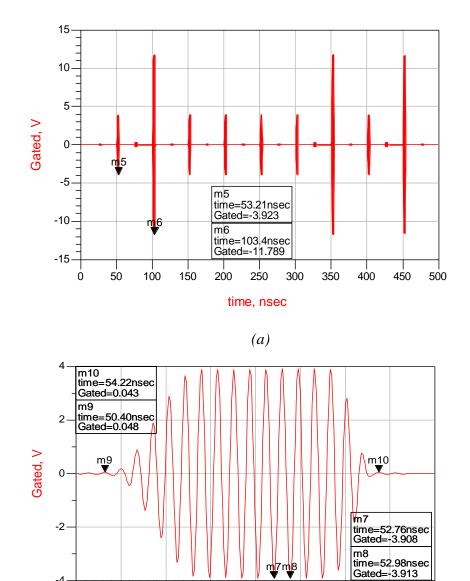

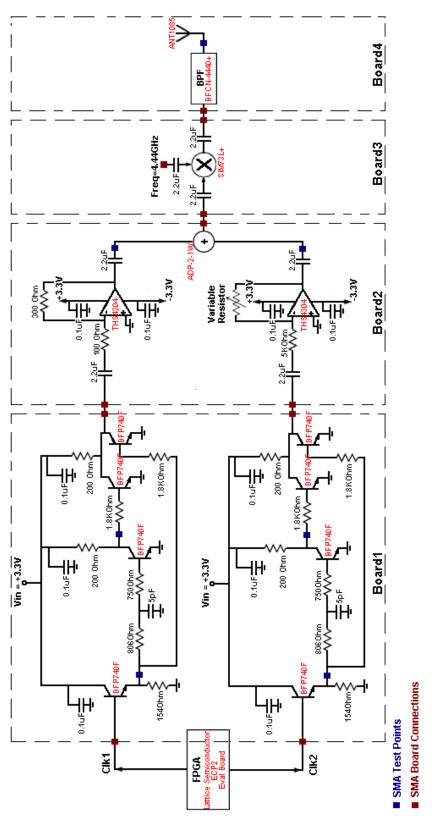

(3.16)