# SOFT ERROR TOLERANT DESIGN OF STATIC RANDOM ACCESS MEMORY BITCELL

by

# Lixiang Li

Submitted in partial fulfilment of the requirements for the degree of Master of Applied Science

at

Dalhousie University Halifax, Nova Scotia September 2015

© Copyright by Lixiang Li, 2015

# **Table of Contents**

| List of Tables                                                        | v    |

|-----------------------------------------------------------------------|------|

| List of Figures                                                       | vi   |

| Abstract                                                              | ix   |

| List of Abbreviation and Symbols Used                                 | X    |

| Acknowledgement                                                       | xiii |

| Chapter 1 Introduction                                                | 1    |

| 1.1 Fundamentals of SRAM                                              | 1    |

| 1.2 Fundamentals of Soft Errors                                       | 2    |

| 1.2.1 Mechanism of Soft Errors                                        | 3    |

| 1.2.2 Sources of Soft Errors                                          | 5    |

| 1.2.2.1 Alpha Particle                                                | 5    |

| 1.2.2.2 Neutron                                                       | 6    |

| 1.2.2.3 Proton                                                        | 8    |

| 1.2.2.4 Heavy Ions                                                    | 8    |

| 1.3 Radiation Hardened By Design (RHBD)                               | 9    |

| 1.3.1 Current RHBD Approaches                                         | 9    |

| 1.3.2 RHBD SRAM Bitcells                                              | 10   |

| 1.3.3 Layout Design Through Error Aware Transistor Positioning (LEAP) | 10   |

| 1.4 Motivation and Thesis Outline                                     | 11   |

| Chapter 2 Existing SRAM Bitcell Designs                               | 13   |

| 2.1 6T SRAM Bitcell                                                   | 13   |

| 2.2 Dual Interlock Storage Cell                                       | 15   |

| 2.3 Quatro Cell                                                               | . 18 |

|-------------------------------------------------------------------------------|------|

| Chapter 3 Soft Error Resilience Layout Technique                              | . 22 |

| 3.1 Charge Sharing and Pulse Quenching                                        | . 22 |

| 3.1.1 Charge Sharing                                                          | . 22 |

| 3.1.2 Pulse Quenching                                                         | . 23 |

| 3.2 Interleaving and Guard Contact                                            | . 25 |

| 3.2.1 Interleaving                                                            | . 25 |

| 3.2.2 Guard Ring and Guard Drain                                              | . 27 |

| 3.3 Layout Design Through Error Aware Transistor Positioning (LEAP) Technique | . 29 |

| Chapter 4 Proposed SRAM Bitcell Structure                                     | . 34 |

| 4.1 Proposed SRAM Bitcell and Basic Operation                                 | . 34 |

| 4.2 SEU Correction Capability                                                 | . 39 |

| 4.3 Read & Write Speed, Power Consumption and Area Overhead                   | . 43 |

| 4.4 Layout Design and LEAP Implementation                                     | . 46 |

| 4.5 3D TCAD Simulation                                                        | . 49 |

| Chapter 5 Proposed 6T Bitcell Layout                                          | . 56 |

| 5.1 Proposed Layout and Traditional Layout of 6T Bitcell                      | . 56 |

| 5.2 Array Organization                                                        | . 61 |

| 5.3 Simulation Result                                                         | . 63 |

| Chapter 6 Architecture and Peripheral Circuit of SRAM Test Chip               | . 66 |

| 6.1 Address Decoder                                                           | . 66 |

| 6.2 Pre-charge Circuit and Sense Amplifier                                    | . 67 |

| 6.3 Write Driver                                                              | . 69 |

| 6.4 Level Shifter and Bitline Sensing Time Control                  | 69  |  |

|---------------------------------------------------------------------|-----|--|

| Chapter 7 Test Chip and Experimental Result                         |     |  |

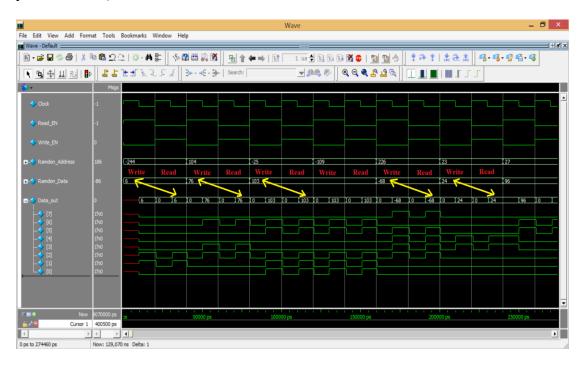

| 7.1 Verilog Modeling of the Test Chip.                              | 73  |  |

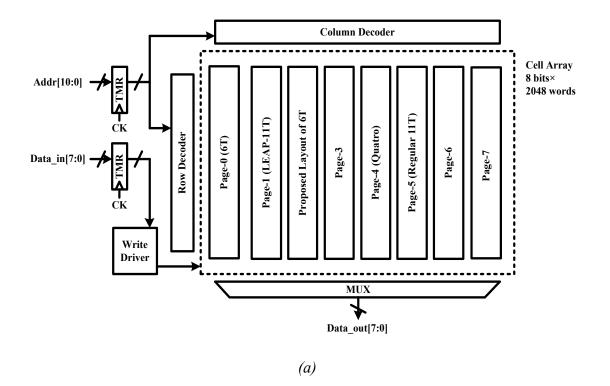

| 7.2 Test Chip and Experimental Setup                                | 75  |  |

| 7.3 Alpha Testing Result                                            | 79  |  |

| 7.3.1 Alpha Testing Result of 11T                                   | 79  |  |

| 7.3.2 Alpha Testing Result of Proposed Layout of 6T                 | 83  |  |

| 7.4 Proton Testing Result                                           | 84  |  |

| 7.4.1 Proton Testing Result of 11T                                  | 84  |  |

| 7.4.2 Proton Testing Result of Proposed Layout of 6T                | 85  |  |

| 7.5 Heavy Ions Result                                               | 86  |  |

| 7.5.1 Heavy Ions Testing Result of 11T                              | 87  |  |

| 7.5.2 Heavy Ions Testing Result of Proposed Layout of 6T            | 89  |  |

| 7.6 Experimental Result Comparison and Analysis                     | 90  |  |

| 7.6.1 Experiment and Simulation Comparison of 11T                   | 90  |  |

| 7.6.2 Experiment and Simulation Comparison of Proposed Layout of 6T | 94  |  |

| Chapter 8 Conclusion and Discussion                                 | 96  |  |

| Bibliography                                                        | 100 |  |

# **List of Tables**

| Table 7.1 Proton testing result                                            | 85 |

|----------------------------------------------------------------------------|----|

| Table 7.2 List of heavy ions.                                              | 86 |

| Table 7.3 Experimental and simulation result comparison of 11T and 6T      | 91 |

| Table 7.4 Experimental and simulation result comparison of 11T and Quatro  | 92 |

| Table 7.5 Experimental and simulation result comparison of proposed layout | 94 |

# **List of Figures**

| Figure 1.1 Architecture of a SRAM                                                                                                                                                                                                                                   | . 2 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 1.2 Charge generation and collection in a PN junction                                                                                                                                                                                                        | . 4 |

| Figure 1.3 Theoretical sea-level cosmic ray (Flux of comic ray in New York City)                                                                                                                                                                                    | . 7 |

| Figure 2.1 (a) Schematic of traditional 6T SRAM bitcell (b) 6T bitcell composed of tw back-to-back inverters and two access transistors A1, A2                                                                                                                      |     |

| Figure 2.2 Schematic of DICE bitcell                                                                                                                                                                                                                                | 16  |

| Figure 2.3 Recovery waveform of logic when X2 is flipped from 1 to 0                                                                                                                                                                                                | 17  |

| Figure 2.4 Recovery waveform of logic when X1 is flipped from 0 to 1                                                                                                                                                                                                | 18  |

| Figure 2.5 Schematic of Quatro-10T bitcell                                                                                                                                                                                                                          | 19  |

| Figure 2.6 Quatro cell recover when Node A is flipped from 1 to 0                                                                                                                                                                                                   | 20  |

| Figure 2.7 Quatro cell is upset because Node A is flipped from 0 to 1                                                                                                                                                                                               | 21  |

| Figure 3.1 Two-dimensional slice of three PMOS transistors depicting the electric signal and the charge sharing signal caused by an ion strike                                                                                                                      |     |

| Figure 3.2 Schematic of an interleaving SRAM                                                                                                                                                                                                                        | 26  |

| Figure 3.3 Schematic of a non-interleaving SRAM.                                                                                                                                                                                                                    | 27  |

| Figure 3.4 Illustration of layout for guard ring                                                                                                                                                                                                                    | 28  |

| Figure 3.5 Cross section view of layout for guard drain                                                                                                                                                                                                             | 29  |

| Figure 3.6 A downward transient is generated when radiation strike a reversed biase NMOS transistor                                                                                                                                                                 |     |

| Figure 3.7 An uprising transient is generated when radiation strike a zero biased PMC transistor                                                                                                                                                                    |     |

| Figure 3.8 LEAP principle for an inverter with transistor alignment. (a) Reduced charge collection when a particle hits both NMOS and PMOS drain nodes of an invert simultaneously. (b) Transistor alignment to reduce charge collection in the horizont direction. | ter |

| Figure 4.1 Proposed 11T cell 34                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.2 Simulation waveforms of a read operation                                                                                                                                                              |

| Figure 4.3 Simulation waveforms of a write operation                                                                                                                                                             |

| Figure 4.4 Recovery simulation waveforms of internal node A, B, C, D when A is subjected to "1 -> 0" upset                                                                                                       |

| Figure 4.5 Simulation waveforms show that the whole cell flips when node "A" is subjected to "0 ->1" SEU                                                                                                         |

| Figure 4.6 Simulation waveforms show that node B takes 11.5ns to recover from "0 -> 1" SEU                                                                                                                       |

| Figure 4.7 Leakage current of 11T, Quatro and 6T cell                                                                                                                                                            |

| Figure 4.8 Write time of 11T, Quatro and 6T cell                                                                                                                                                                 |

| Figure 4.9 Read time of 11T, Quatro and 6T cell                                                                                                                                                                  |

| Figure 4.10 (a) Illustration of 11T layout (b) 11T layout in TSMC 65nm bulk technology                                                                                                                           |

| Figure 4.11 (a) Illustration of LEAP-11T layout (b) LEAP-11T layout in TSMC 65nm bulk technology                                                                                                                 |

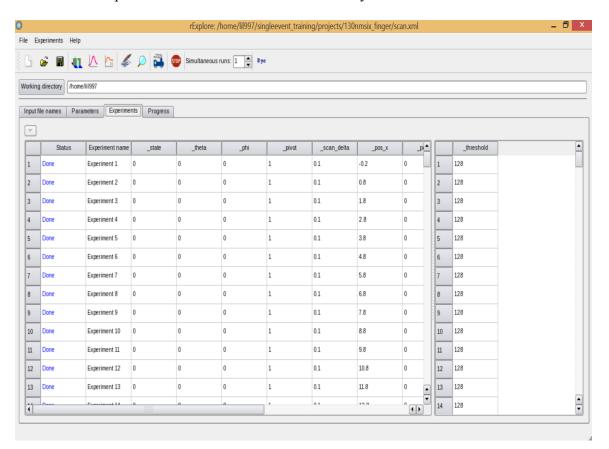

| Figure 4.12 GUI of Accuro tool                                                                                                                                                                                   |

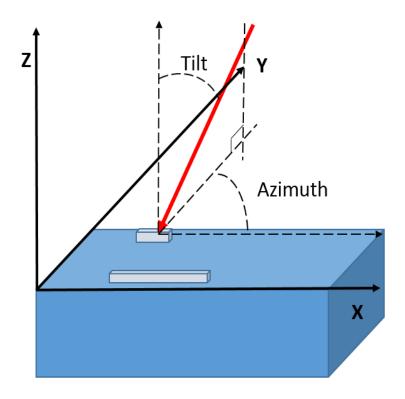

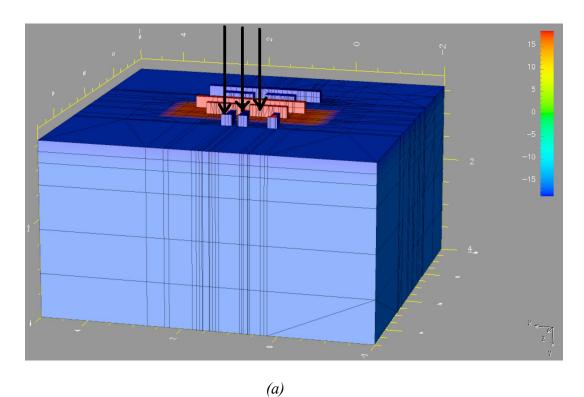

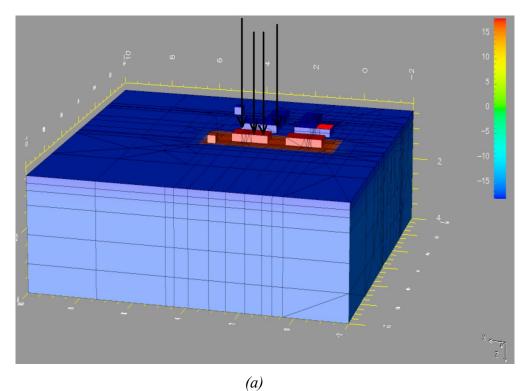

| Figure 4.13 Illustration of Tilt and Azimuth for an incoming radiation strike in Accuration                                                                                                                      |

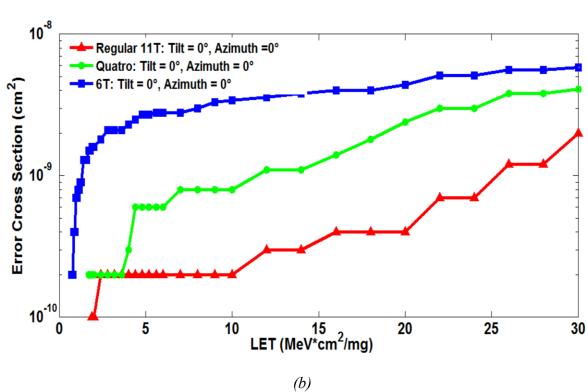

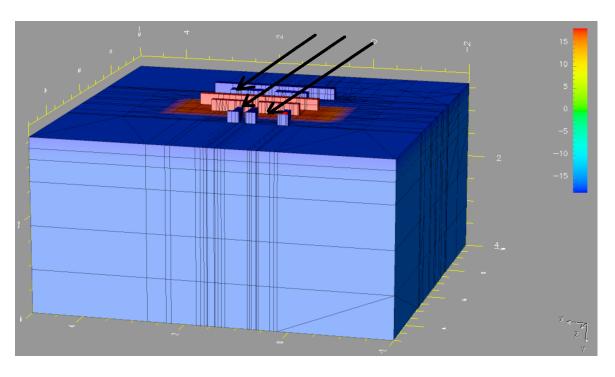

| Figure 4.14 (a) Radiation strikes LEAP-11T bitcell when Tilt = $0^{\circ}$ , Azimuth = $0^{\circ}$ (b) Error Cross Section of 6T, Quatro and regular 11T cell when Tilt = $0^{\circ}$ , Azimuth = $0^{\circ}$ 53 |

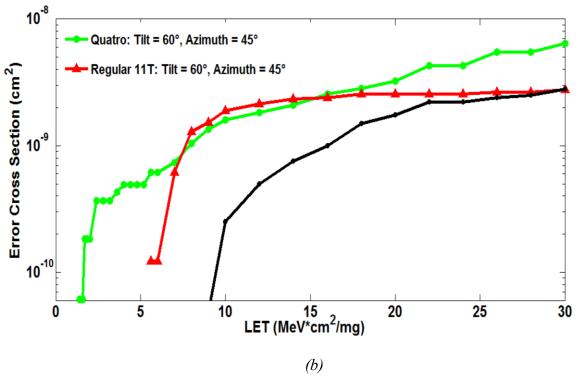

| Figure 4.15 (a) Radiation strikes LEAP-11T bitcell when Tilt = 60°, Azimuth = 45° (b) Error cross section of Quatro cell, regular 11T cell and LEAP-11T cell when Tilt = 60° Azimuth = 45°                       |

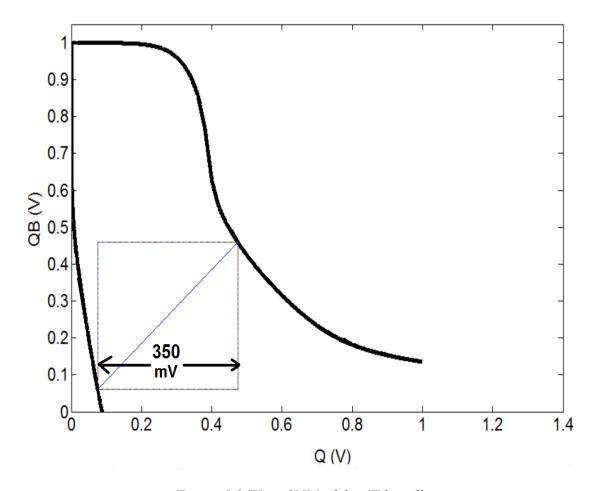

| Figure 5.1 Read SNM of the 6T bitcell                                                                                                                                                                            |

| Figure 5.2 Write SNM of the 6T bitcell                                                                                                                                                                           |

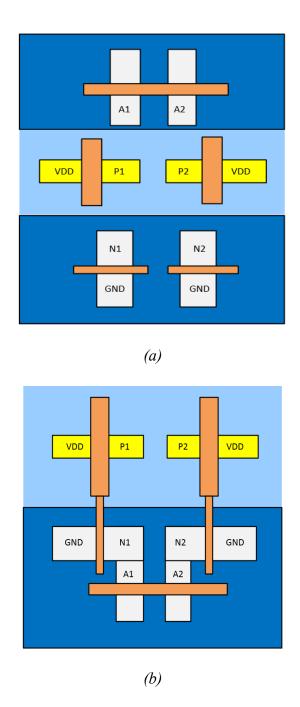

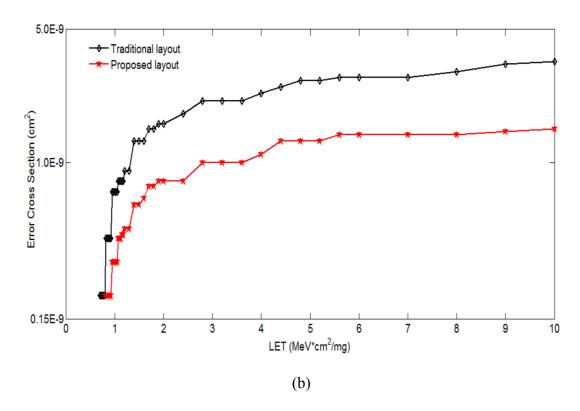

| Figure 5.3 (a) Proposed layout of 6T bitcell (b) Regular Layout of 6T SRAM cell 59                                                                                                                               |

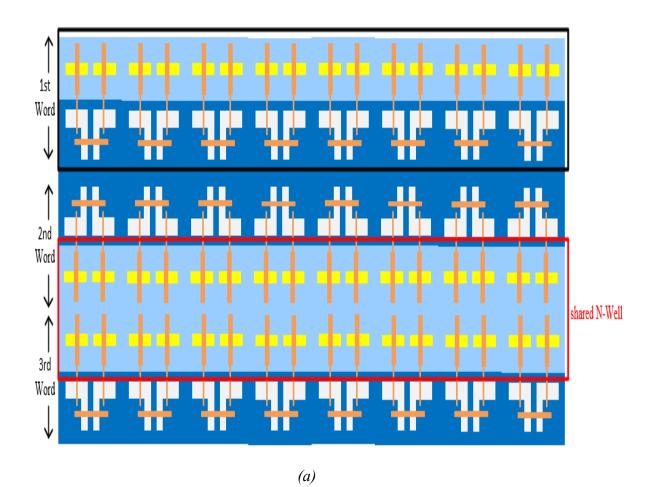

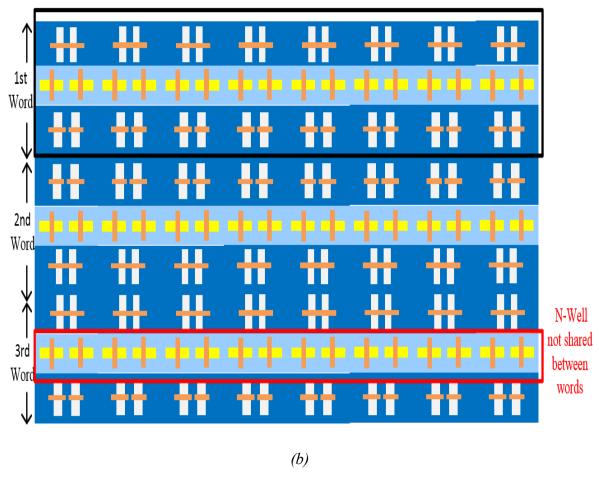

| Figure 5.4 (a) Array organization of regular layout of 6T SRAM cell (b) A organization of proposed layout of 6T bitcell                                          |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 5.5 (a) Radiation strike 6T when Tilt = $0^{\circ}$ and Azimuth = $0^{\circ}$ (b) Simulation cross section between traditional layout and proposed layout |      |

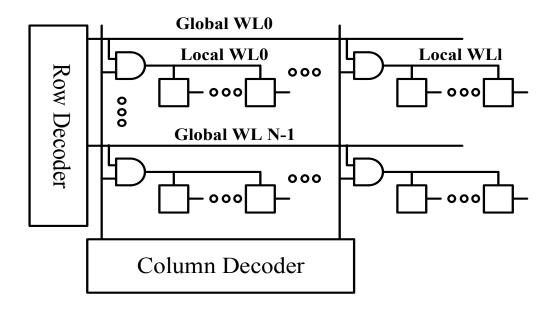

| Figure 6.1 Row and column decoders generating wordlines                                                                                                          | 67   |

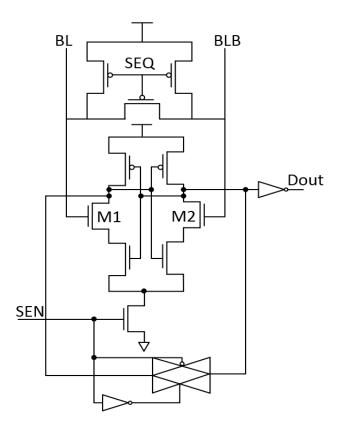

| Figure 6.2 Schematic of pre-charge circuit and sense amplifier                                                                                                   | 68   |

| Figure 6.3 Write driver circuit                                                                                                                                  | 69   |

| Figure 6.4 Schematic of level shifter                                                                                                                            | 70   |

| Figure 6.5 Wait time control circuit.                                                                                                                            | 72   |

| Figure 7.1 Verilog model simulation of the test chip                                                                                                             | 74   |

| Figure 7.2 (a) Block diagram of SRAM test chip (b) Die photo of SRAM chip                                                                                        | 76   |

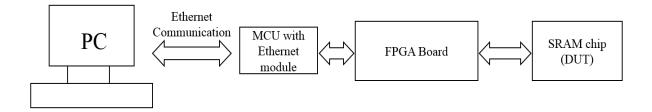

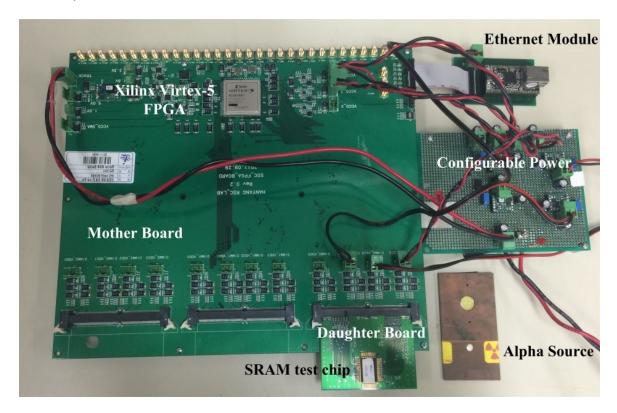

| Figure 7.3 Illustration of testing setup                                                                                                                         | 77   |

| Figure 7.4 Photo of the alpha testing system                                                                                                                     | 78   |

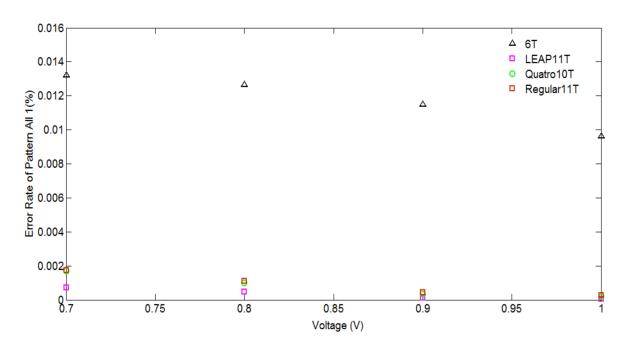

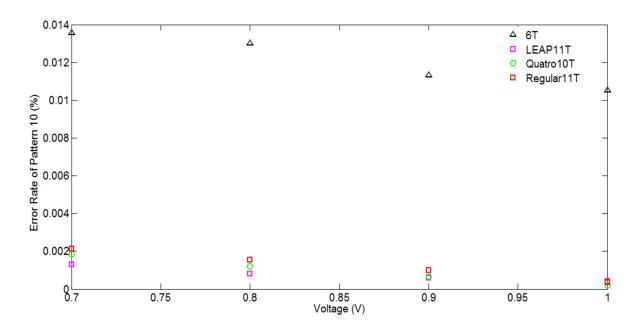

| Figure 7.5 Soft error rate comparison when data pattern is 11111111                                                                                              | 80   |

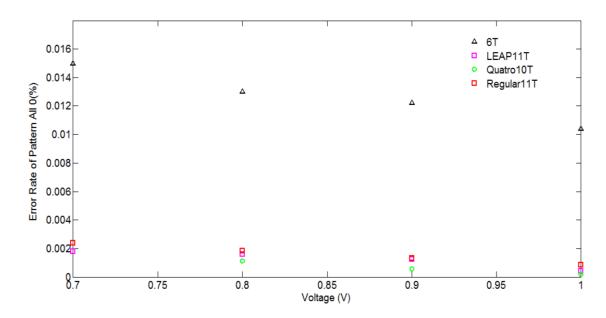

| Figure 7.6 Soft error rate comparison when data pattern is 00000000                                                                                              | 81   |

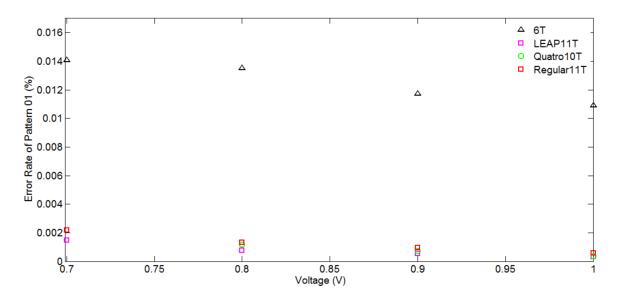

| Figure 7.7 Soft error rate comparison when data pattern is 01010101                                                                                              | 81   |

| Figure 7.8 Soft error rate comparison when data pattern is 10101010                                                                                              | 82   |

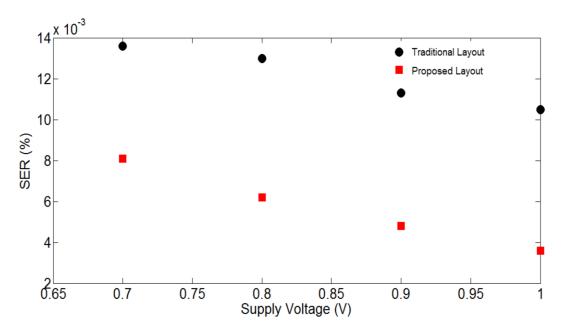

| Figure 7.9 Alpha testing SER of proposed layout and traditional layout of 6T                                                                                     | 84   |

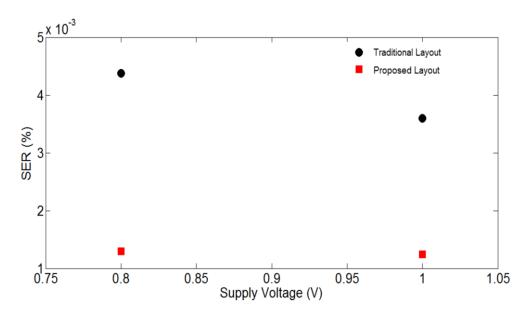

| Figure 7.10 Proton testing SER of proposed layout and traditional layout of 6T                                                                                   | 86   |

| Figure 7.11 Error cross section comparison of three bitcells in all 0 patterns                                                                                   | 87   |

| Figure 7.12 Error cross section comparison of three bitcells in all 1 patterns                                                                                   | 88   |

| Figure 7.13 Error cross section comparison of three bitcells in checkerboard 01 patter                                                                           | rn89 |

| Figure 7.14 Error cross section of proposed layout and traditional layout of 6T                                                                                  | 90   |

### Abstract

Static Random Access Memories (SRAMs) are commonly used in most of electronics. Due to the scaling of silicon technologies, the soft errors induced by energetic particles are becoming a significant reliability concern. This thesis presents two new Radiation-Hardened-by-Design (RHBD) bitcell designs for SRAMs. The effectiveness of the proposed RHBD bitcell designs are evaluated by using Simulation Program with Integrated Circuit Emphasis (SPICE) and Technology Computer Aid Design (TCAD) tools. The designs are implemented using Taiwan Semiconductor Manufacture Company (TSMC) 65 nm technology, and are validated in three different radiation experiments (alpha, proton and heavy ion particles).

This thesis has thoroughly introduced the SRAM bitcell topology, layout design, SRAM peripheral circuits, SPICE simulation, TCAD simulation and radiation experiments. The comparison of simulation and experimental results are clearly made. The thesis has presented designs which are more soft error tolerant in certain Linear Energy Transfer (LET) ranges compared to the reference bitcells.

# List of Abbreviation and Symbols Used

ASIC- Application Specific Integrated Circuit

**BL-** Bitline

BLB- Bitline Bar

CAMBR- Center for Advanced Microelectronics & Bio Molecular Research

CMC- Canadian Microsystem Corporation

CMOS- Complementary Metal Oxide Semiconductor

CVSL- Cascode Voltage Switching Logic

DICE- Dual Interlocked Storage Cell

DIMM- Dual In-line Memory Module

DRC- Design Rule Check

DRAM- Dynamic Random Access Memory

**DUT-** Device under Test

**ECC- Error Correction Code**

FF- Flip Flop

FPGA- Field Programmable Gate Array

GDSII- Graphic Database System 2 Format

GUI- Graphical User Interface

IC- Integrated Circuit

ITRS- International Technology Roadmap for Semiconductors

LEAP- Layout Design through Error Aware Transistors Positioning

LET- Linear Energy Transfer

MBU- Multi Bit Upset

MCU- Multi Cell Upset

MeV- Mega Electron Volt

MRC - Microelectronic Research Center

NMOS- N Type Metal Oxide Semiconductor

PMOS- P Type Metal Oxide Semiconductor

RCI- Robust Chip Inc.

RHBD- Radiation Hardening By Design

RTL- Register Transfer Level

SA- Sense Amplifier

SBU- Single Bit Upset

SEE- Single Event Effect

SEMU- Single Event Multiple node Upset

SER- Soft Error Rate

SET- Single Event Transient

SEU – Single Event Upset

SNM – Static Noise Margin

SoC- System on Chip

SPICE - Simulation Program with Integrated Circuit Emphasis

SRAM- Static Random Access Memory

SRNM- Static Read Noise Margin

STI- Shallow Trench Isolation

SWNM- Static Write Noise Margin

TCAD- Technology Computer Aided Design

TRIUMF- Tri-University Meson Facility

VHDL- Very High Speed Hardware Description Language

VLSI- Very Large Scale Integration

TMR- Triple-Modular-Redundancy

VTC- Voltage Transfer Characteristic

# Acknowledgement

Graduate study is a solitary and grinding process, but I think it is the experience of it that makes a difference in life. First of all, I would like to thank my supervisor Dr. Yuan Ma for letting me explore the field of my research interest and for always being accessible to me. And second, I also want to thank my co-supervisor Dr. Li Chen in the University of Saskatchewan for giving me an opportunity to be exposed to soft error tolerant designs. And I also would like to thank Dr. Yajun Pan and Dr. Jean-Francois Bousquet for taking the time and being in my committee.

I also appreciate the time being with all the colleagues at Dalhousie University and University of Saskatchewan.

Last but not least, I would like to thank my families, without whom I wouldn't be who I am as person today. Hopefully I can make them proud by doing what I do.

# **Chapter 1 Introduction**

Static Random Access Memory (SRAM) is an important component of integrated circuits and Systems on Chip (SoC). Its faster read and write speed compared to other type of memories makes it desirable in many speed contingent applications. However, there are drawbacks of SRAM, with one being the large area penalty and another being the susceptibility to radiation damage.

As of 2014, embedded memories usually occupy over 50 % of the area of most SoCs [1]. A soft error is a type of data or logic corruption resulting from a radiation strike. When a ray of radiation strikes the SRAM cells, radiation particles either bring in charges (positive and negative), or the particles react with the silicon nuclei in the substrate and produce charge. The charge is mainly deposited in the drain areas of the substrate, causing logic corruptions. In the past few decades, a significant amount of research has been conducted on reducing the area penalty and the soft errors of SRAMs.

#### 1.1 Fundamentals of SRAM

SRAM is a type of volatile memory, which means it can only store data when its power supply is turned on. When the power is turned off, the data will be lost. The users can read any data given the address of the data, or the users can write data to a specific address. Most SRAMs are manufactured in CMOS technology. As the CMOS process is currently the dominant technology for integrated circuit fabrication, SRAM can be easily integrated with different kinds of circuits into a single chip. SRAMs are widely used for register files and memory caches.

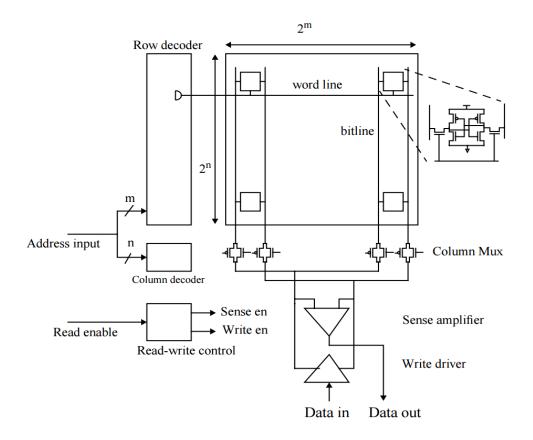

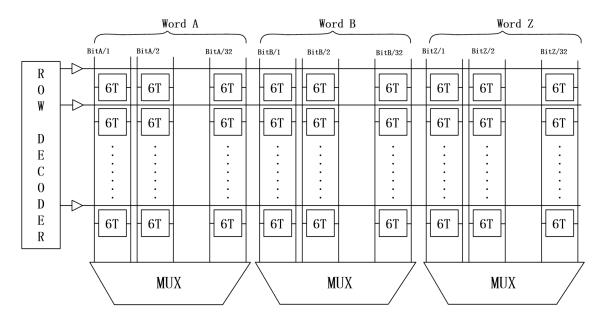

A SRAM cell is composed of a memory bitcell array, address decoders (column and row decoders), multiplexers, sense amplifiers, write drivers and pre-charged circuities. A typical architecture of a SRAM is illustrated in Figure 1.1.

As seen in Figure 1.1, the memory bitcell array is  $2^m \times 2^n$ , and it is composed of 6-transistor (6T) bitcells. Each bitcell is connected to two bitlines, and the bitlines are connected to sense amplifiers. The sense amplifiers read in the small differential input of the bitlines and speed up the generation of the output data. The outputs of the sense amplifiers are then connected to the column multiplexers. In each read operation, only one column multiplexer is turned on and its output can be transferred to the output pins for the user to read. In each write operation, the data first goes through the write driver circuits and then the data are loaded into the bitlines and written into bitcells. In both read and write operations, the address decoders (read and write decoders) generate a word line signal to access a byte of data. A detailed analysis of the SRAM circuitry can be found in Chapter 6.

Figure 1.1 Architecture of a SRAM

#### 1.2 Fundamentals of Soft Errors

The prediction and study of soft errors in electronics can be dated back to the 60s. In 1961, J. T. Wallmark first raised the issue of soft errors in [2]. In 1975, four "anomalies" were found in satellites and reported in [3]. In 1979, Intel Corp. found soft errors in Dynamic Radom Access Memory (DRAM).

As the microelectronic circuits continue to shrink in size, soft errors have become an increasingly important issue. In the past decade, many telecommunication companies have suffered from soft errors and have dedicated significant customer services to this. For instance, the high end server crash from Sun Microsystem is reported in [4]; Cisco's

network glitch in 2005 had significant financial consequences [5]. The Semiconductor Industry Association (SIA) roadmap has identified soft errors as the major threat to reliable operation of electronic systems in the future [6]. Therefore, much research has been conducted to study the soft errors mechanism in analog and digital circuits.

### 1.2.1 Mechanism of Soft Errors

Both "single event transient" (SET) and "single event upset" (SEU) can be categorized as soft errors. SET is an undesirable transient pulse usually generated in combinational logic circuits under radiation strike and propagates through the logic chain, in which the output is based on a logical relation to the inputs with no capability of retention. If a SET propagates to the input of a latch or a flip-flop during a latching clock signal, the erroneous input will be latched and stored and this causes a SEU. In older technologies, a SET is hard to propagate because it usually does not produce a full output swing or is quickly attenuated because of large load capacitances and large propagation delays. In advanced technologies, where the propagation delay is reduced and the clock frequency is high, SET can traverse many logic gates easily, and the probability that a SET is locked in a latch and causes SEU increases. It should be noted that there is another similar effect that is caused by radiation in electronics called Single Event Latch-up (SEL). The mechanism of SEL is the same as a classical electrical latch-up. A SEL can result in a high operating current, and it must be cleared by resetting the power. SELs can also cause permanent damage to the device if the latch-up current is very high.

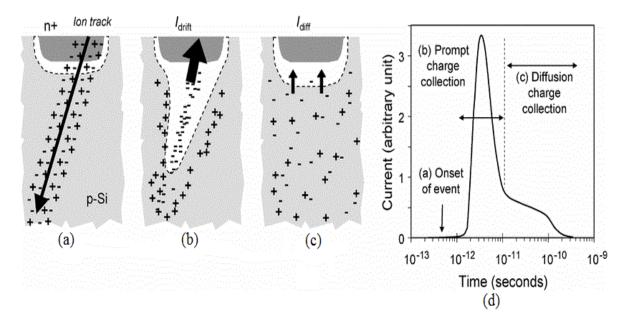

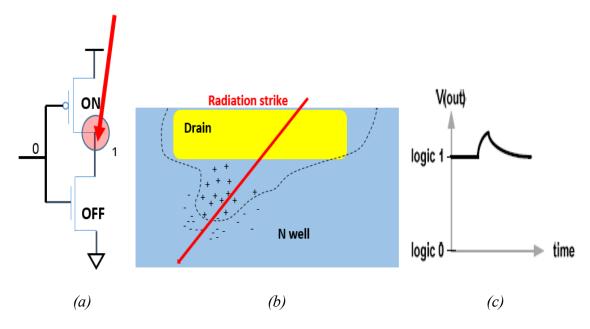

Figure 1.2 (a) shows a scenario when a ray of radiation strikes the drain area of an N-type Metal Oxide Semiconductor (NMOS) transistor [7]. As can be seen in Figure 1.2 (a),

the radiation brings in different charge (positive and negative). If the radiation particle is a proton or a neutron, it can react with the silicon nuclei and create secondary charge. The nature of the built-in electric field in the PN junction between the drain area and the substrate of the NMOS transistor leads to the negative charge being collected in the N+ diffusion area and the positive charge being deposited at the substrate, as shown in Figure 1.2 (b). Therefore, a transient current spike can be observed at the drain node, as shown in Figure 1.2 (d). The current spike can consequently induce a voltage spike. The voltage spike is undesirable and can be locked by any memory or latch unit. Eventually the charge collected at the drain and the substrate will diffuse and get neutralized over time as can be seen in Figure 1.2 (c).

Figure 1.2 Charge generation and collection in a PN junction

#### 1.2.2 Sources of Soft Errors

Sources of soft errors can come from the packaging material of the chip, terrestrial environment and space environment. In different environments, different radiation sources cause the soft errors. The most common sources of the soft errors are "alpha particle", "proton", "neutron" and "heavy ions". The following is an introduction of these sources of soft errors and how they cause "upsets" in integrated circuits.

#### 1.2.2.1 Alpha Particle

An alpha particle is composed of two protons and two neutrons, and it can be emitted from unstable radioactive isotopes. The most common radioactive isotopes are Uranium-235, Uranium-238, and Thorium-232. They can be found in commonly used packaging materials of integrated circuit chips. These radioactive isotopes can release energies within the range from 4 MeV to 9 MeV. The soft errors in DRAM found by Intel in the late 1970s were caused by traces of Uranium and Thorium in the packaging materials. Since the alpha particle carries a positive charge, it can create an ionized path as it travels through the silicon until it loses all of its energy. The higher the energy, the further it travels. The usual travel length of an alpha particle with less than 10 MeV energy is < 100 µm. Therefore, the alpha particle outside of the package material is not a concern for soft errors. Currently, many foundries have reduced or eliminated the radioactive isotopes in the packaging material, and soft errors caused by alpha particles are subsequently reduced.

In this thesis, an alpha particle radiation experiment is conducted on the fabricated design using Americium-241 alpha source with 2.5 uCi activity and 4.61e<sup>7</sup> a/cm<sup>2</sup>/h

emissivity in the University of Saskatchewan to evaluate the soft error tolerance of the proposed design. The details of the alpha particle radiation experiment can be found in Chapter 6.

#### 1.2.2.2 Neutron

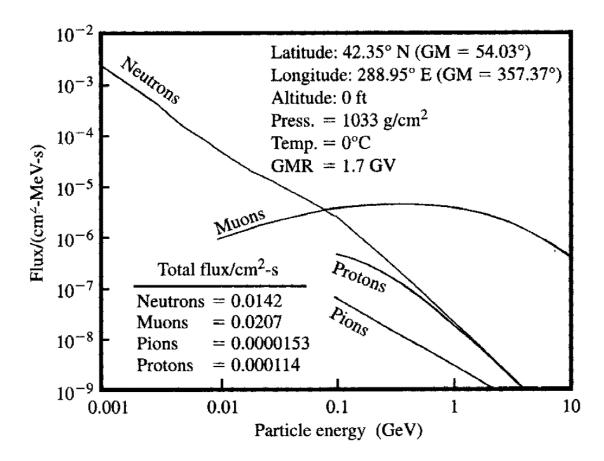

Neutrons are one of the major sources of soft errors in a terrestrial environment. They originate from the near-earth space environment. In the near-earth space environment, neutrons usually have very high energy, and they can react with the upper atmosphere of the earth. The reacting collisions, modulated by the earth's magnetic field, can generate high-energetic recoil particles, such as high energy neutrons, muons and pions. Out of these particles, only the charge-less high energy neutrons have the potential to reach the earth's surface to interact with semiconductor devices. The remaining energy is about 1-500 MeV when they reach the earth's surface. The terrestrial radiation environment consists of about 92 % neutrons, 4 % pions and 2 % protons [8]. The distribution and flux of the particles at New York City typifies the theoretical calculation at the sea level, as can be shown in Figure 1.3 [9]. As can be seen from the figure, neutrons are dominant compared to others particles, and therefore, a prominent source of soft errors compared to other particles in the terrestrial environment.

Figure 1.3 Theoretical sea-level cosmic ray (Flux of comic ray in New York City)

For a high-energy neutron to cause a soft error, it must produce ionized particles by colliding with the silicon nucleus and undergo impact ionization with the silicon nuclei. This kind of collision generates alpha particles and other heavier ions, producing electron-hole pairs, but with higher energies than a typical alpha particle from packaging impurities. In 1993, the neutron-induced soft errors were found in a computer onboard a commercial aircraft [10].

#### 1.2.2.3 Proton

High energy protons are the biggest concern for soft errors in the near-earth space environment. Protons have the same indirect ionization mechanism as neutrons. The details of proton-induced soft errors are investigated in [11]-[17]. A proton carries a positive charge, but the indirect ionization between the proton and silicon nuclei can actually generate a lot more charge than that from a proton itself. High energy protons can also be generated by a reaction between heavy ions and silicon dopants. Elastic scattering and spallation reactions between Si (p, p) Si<sup>28</sup>, Si (p, He<sup>4</sup>) Mg<sup>25</sup>, and Si<sup>28</sup> (p, p He<sup>4</sup>) Na<sup>24</sup> can transfer a large fraction of proton energy to the recoils and fragments [18]. In the terrestrial environment, low energy protons are usually absorbed in the atmosphere or shielded by the package of the circuit chip, and therefore do not pose soft error threats.

In this thesis, a high energy proton radiation experiment is conducted on the fabricated SRAM chips in TRIUMF (Tri-University Meson Facility), Vancouver, British Columbia, Canada. All protons were incident normally, and their average energy is 63 MeV. The proton testing will be discussed in Chapter 6.

## 1.2.2.4 Heavy Ions

A heavy ion by definition is any ion that has more than two atoms. It is a major source of the soft errors in the space environment, and it has very high Linear Energy Transfer (LET) level. LET is used to measure the energy of a radiation strike and it is measured in terms of energy lost per unit length. A heavy ion can cause the soft errors via direct ionization. Heavy ions are abundant in cosmic rays in the space environment. The effects heavy ions have on integrated circuits have been observed in space and aircraft

electronics. Some heavy ions can also react with silicon dopants (especially Borons) to generate neutrons and protons. In this thesis, the heavy ions experimental result is also presented and it will be discussed in Chapter 7.

#### 1.3 Radiation Hardened By Design (RHBD)

To reduce radiation-induced soft errors in SRAMs, different approaches have been proposed, and they can be categorized into two types as Radiation Hardened by Process (RHBP) approach and Radiation Hardened by Design (RHBD) approach. RHBP requires manufacturing variations away from and the standard mainstream process, i.e. the Complementary Metal Oxide Semiconductor (CMOS) process, and therefore it is expensive to be implemented. On the other hand, RHBD is easier to implement, and is favorable in research and industries for various applications.

#### 1.3.1 Current RHBD Approaches

Error Correction Code (ECC) can be loosely categorized as RHBD. It is the most popular approach to reduce the soft error rate for SRAM because of the regular nature of the memory array [19]-[21]. Through adding more bits in a word, the soft errors in single or multiple bits can be corrected by ECC, and the protection abilities of different ECCs (amount of errors can be corrected) depend on different specific algorithms. As a system-level hardening approach, ECC commonly involves less custom-design tasks which relatively ease the implementations. However, ECC can increase the access time of SRAM and therefore slow down the performance of the whole system.

Circuit duplication (including "Triple Module Redundancy" and "Built-in Soft-Error-Resilience (BiSER)") with the combination of a voting circuitry is another RHBD approach that addresses soft error problem, but this technique generates undesirable power and area overhead. Additionally, current versions of this technique cannot handle Multi-bit Upsets (MBUs).

#### 1.3.2 RHBD SRAM Bitcells

Many radiation hardened SRAM bitcell structures have been proposed, among which Dual Interlock Storage Cell (DICE) [22] and Quatro cell [23] are most favorable. A lot of researches [24]-[27] have been conducted on these structures. A DICE bitcell has twelve transistors and consumes almost twice as much area as a traditional 6T bitcell. It is, however, very effective in correcting SEU when radiation only affects one node in the bitcell. As technology continues to advance, Quatro cells exhibit better soft error resilience than DICE bitcells, especially when LET is very high. In [27], it is reported that Quatro cell exhibits better soft error rate than DICE cell in 40 nm technology.

#### 1.3.3 Layout Design Through Error Aware Transistor Positioning (LEAP)

For the radiation hardened physical layout design, traditional layout techniques consist of spacing, sizing and adding contact. As the transistor size continues to shrink, charge sharing becomes very prominent [28] [29]. Recently, a technique called pulse quenching is taking advantage of the charge sharing to reduce the width of SET for combinational logic circuits. Another layout technique called "Layout Design Through Error Aware Transistor Positioning (LEAP)" was developed in [30] [31]. It is reported in [32] [33] that

this technique is implemented in the layout of D flip-flops and DICE flip-flops in 180 nm and 28 nm technology, and their soft error tolerances have been greatly improved.

#### 1.4 Motivation and Thesis Outline

The objective of this thesis is to design soft error tolerant SRAM bitcell structures that have relatively low area penalty. Both schematic and layout approach are used in designing bitcells.

Since SRAMs are widely used in memory caches, register files and SoCs, the data in the SRAMs can be severely corrupted under radiation strikes; therefore, it is important to design a SRAM that is robust in a radiation environment. In this thesis, a soft error robust SRAM bitcell design is proposed and a RHBD approach is adopted to further improve the soft errors tolerance. To evaluate the proposed SRAM bitcell design, a test chip is fabricated using 65 nm CMOS technology. Different radiation experiments have been carried out for evaluations, and comparison between simulation and experiments are presented in this thesis.

The thesis outline is as followed. Chapter 2 introduces the SRAM bitcells that are widely used in the industry and research and they will be used as reference to compare the proposed structure. Chapter 3 provides an overview on the layout techniques that are used for soft error protection. Chapter 4 introduces the proposed 11T bitcell's schematic and layout implementation with LEAP technique, as well as the Simulation Program with Integrated Circuit Emphasis (SPICE) and Technology Computer Aid Design (TCAD) simulation results. Chapter 5 introduces the proposed layout for traditional 6T bitcell and presents the TCAD simulation results. Chapter 6 introduces the test chip's architecture

and peripheral circuits. Chapter 7 presents the functional and radiation experimental setup for the test chip, the alpha particle, proton, and heavy ions radiation experiment results of both proposed structures, as well as the comparisons between the simulation and the experimental results. Chapter 8 concludes the proposed structures and thesis.

### **Chapter 2 Existing SRAM Bitcell Designs**

Overall the years, many different designs have been proposed for SRAM bitcell structures. This Chapter introduces several SRAM bitcells that are used in both industry and academic research. Section 2.1 introduces the 6T bitcell, which is most commonly used in the industry because of its compact size. Section 2.2 introduces DICE bitcell and section 2.3 introduces Quatro bitcell, and their single event upset correction mechanism is also analyzed.

#### 2.1 6T SRAM Bitcell

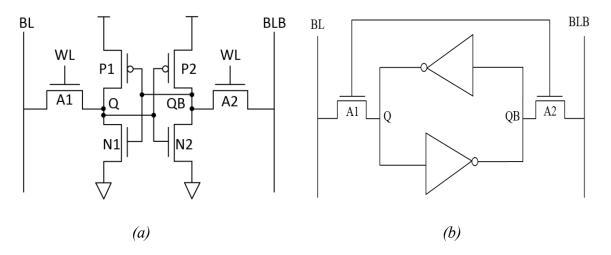

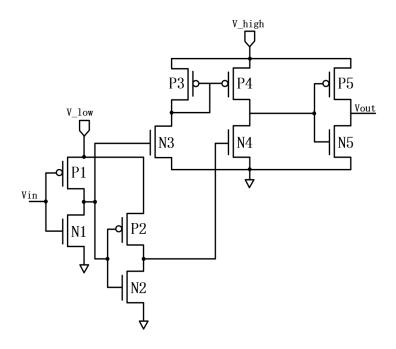

In microelectronics, a cross-coupled inverter pair is the foundation of the static storage elements, including SRAMs, register files, latches and flip-flops. The crossed-coupled inverter can constantly refresh its logic through a strong positive feedback using two inverter pairs. The most popular and widely implemented structure in commercial SRAMs is the conventional 6-Transistor (6T) structure as shown in Figure 2.1 (a) (b). As shown in the Figure 2.1 (a), the 6T cell contains a pair of cross-coupled inverters (*P1*, *N1* and *P2*, *N2*), which can hold the states, and a pair of access transistors (*N3* and *N4*), which are used to read/write the state from/into the nodes. Two internal nodes *Q* and *QB* are used to store logics. Two inverter pairs *P1*, *N1* and *P2*, *N2* have positive feedback on each other to constantly refresh logic. Two access transistors *A1*, *A2* are controlled by *WL* signal and they connect *Q*, *QB* to *BL*, *BLB*.

Figure 2.1 (a) Schematic of traditional 6T SRAM bitcell (b) 6T bitcell composed of two back-to-back inverters and two access transistors A1, A2

In read operation, BL and BLB are first pre-charged to high. WL is activated and then A1, A2 are turned on. The BL or BLB starts to be pulled down depending on what logic stores in Q and QB. In order to pull down the voltage in BL/BLB, the size of N1, N2 needs to be bigger than A1, A2 to make sure that the original logic will not be corrupted in the cell. In general,  $(W_{N1}/L_{N1})/(W_{A1}/L_{A1})$  or  $(W_{N2}/L_{N2})/(W_{A2}/L_{A2})$  (bitcell ratio) can vary from 1.25 to 2.5 in various applications [34]. The voltage difference developed in BL and BLB will overcome the offset of the sense amplifier, which will swing the output to be a complete digital logic.

In write operation, the data will first be loaded in BL and BLB. After WL is turned on, the data starts to write into Q and QB. In order to guarantee a successful write operation, the access transistor should have a bigger drivability than the pull-up transistors P1, P2. In general, a successful write operation can be guaranteed by choosing the  $(W_{AI}/L_{AI})/(W_{PI}/L_{PI})$  or  $(W_{A2}/L_{A2})/(W_{P2}/L_{P2})$  (pull-up ratio) less than or equal to 1.

As indicated in [35], there are two important aspects in SRAM design, one is cell size and the other is the stability. For the size, the 6T bitcell has the least area penalty and therefore is very favorable in many applications in the industry. But for the stability, the 6T design is very vulnerable to radiation strike. Once one of the two internal nodes is flipped by radiation, the positive feedback can easily flip the content of the whole cell.

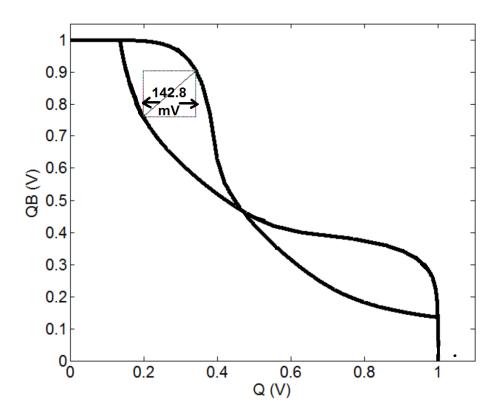

Static Noise Margin (SNM) is defined as the maximum static spurious noise that a bitcell can tolerate while still maintaining a reliable operation. SNM is a very important design metric and a good design should have sufficient SNM to withstand dynamic noise from different sources, such as coupling, soft errors, supply voltage fluctuations, and change in voltage dependent capacitances in the bitcells.

### 2.2 Dual Interlock Storage Cell

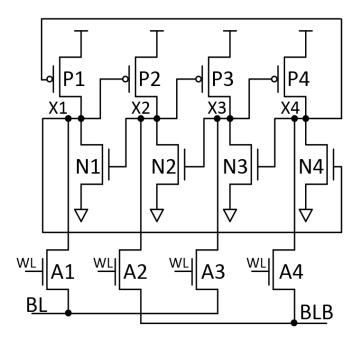

A dual interlock storage cell (DICE) consists of eight interlocked inverters and four access transistors as shown in Figure 2.2, and is first proposed in [22]. Unlike traditional 6T cells, four internal nodes A, B, C, D are used to store logics, instead of two nodes. The two logic states stored in the cell are either "1, 0, 1, 0" or "0, 1, 0, 1". So by using redundant nodes to store logic, DICE is a lot more robust than the traditional 6T cell. Many previously proposed designs [24] [25] [36] are all based on DICE.

Figure 2.2 Schematic of DICE bitcell

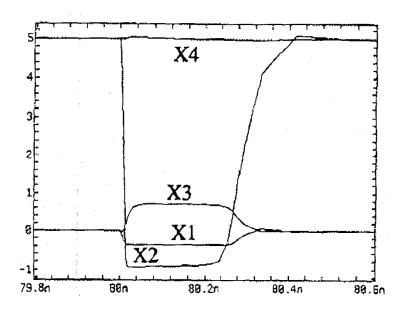

The fundamentals of SEU recovery mechanism of DICE is explained as followed. Suppose the original logic 0, 1, 0, 1 is stored in the cell, and a ray of radiation is striking N2 which pulls the voltage of node X2 from 1 to 0. In this case, node X2 turns off N1 and turns on P3. Therefore, P3, N3 are both turned on at the same time in this moment, but node X3 can maintain a relatively low voltage and the logic is not affected (pull-down NMOS has stronger drivability than pull-up PMOS in memory design). Both P1 and N1 are turned off at this moment, X1 is kept floating and can be maintained at a very low voltage; therefore the logic is considered not affected. Eventually after the SET is gone, X2 can recover back to 1. Figure 2.3 shows the recovery waveform [22]. As can be seen from the waveform, node X2 is pulled down completely from 1 to 0, but the voltage of node X3 only rises up a bit and doesn't change its logic. Eventually node X1 recovers back to 1, and X3 also goes back to 0 completely.

Figure 2.3 Recovery waveform of logic when X2 is flipped from 1 to 0

In the same logic when XI, X2, X3, X4 are still 0, 1, 0, 1, when radiation strike PI and flip XI from 0 to 1, the recovery mechanism is as follows. In this case, XI is flipped from 0 to 1, so node XI will turn on N4 and turn off N2. Node D will actually be changed to 0 (in memory design pull-down, NMOS has stronger drivability than pull-up PMOS). For node X2, because N2 and P2 are both turned off, it is floating and therefore considered as unaffected. So XI and X4 are affected, but X2 and X3 are unaffected. As NI is kept turned on by node X2, after the SET is gone, XI can recover back to low voltage. As soon as X recovers, X4 recovers back to 1. The following Figure 2.4 shows the recovery waveform. As shown in the figure, XI recovers back to 0 at around 75.3 ns, and X4 recovers at around 75.4 ns.

Figure 2.4 Recovery waveform of logic when X1 is flipped from 0 to 1

In legacy technologies, DICE cell has been proven to be very effective in mitigating soft errors. In the sub-100 nm technology, however, DICE is not as superior as traditional design because the radiation can affect several nodes simultaneously due to shrinking device dimension. It has been verified that at 40 nm technology, DICE-FF exhibits only 1.4X improvement over the DFF in neutron and proton environments [37]. It is reported that DICE has a total of 6 sensitive node pairs, and another RHBD bitcell called Quatro [23] has sensitive node pairs of 4 [27]. It has been reported that Quatro bitcell exhibits a better soft error rate than DICE cell in 40 nm technology.

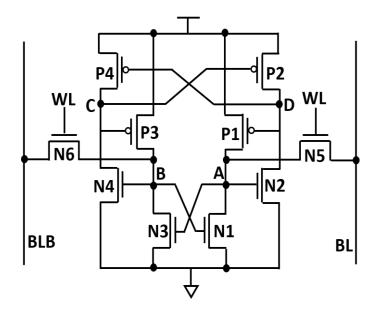

#### 2.3 Quatro Cell

Quatro cell is initially proposed in [23], and it is composed of ten transistors, as shown in Figure 2.5. This cell also has four internal nodes (A, B, C, D). Unlike the DICE cell

where the four internal nodes are dual interlocked, the four nodes in Quatro cell are in a CVSL logic. Quatro cell only uses ten transistors and has less area overhead compared to DICE bitcell.

Figure 2.5 Schematic of Quatro-10T bitcell

Quatro cell also has soft error correction capability. Supposing the logic state stores in A, B, C, D are 1, 0, 1, 0 respectively, if a ray of radiation strikes *N1* and pulls node A down to logic 0, *N2* and *N3* will be turned off, so node B and C are floating. The voltage of B and C can be kept at 1, so after the transient is gone, node A can recover back to 0 because *N1* is kept turned on by node B and *P1* is kept turned off by node C. Figure 2.6 shows recovery waveform after node A is flipped from 1 to 0. Node B, C, and D are basically not affected, and node A recovers back to voltage 1 at about 200 ps.

Figure 2.6 Quatro cell recover when Node A is flipped from 1 to 0

There are scenarios when Quatro cell is sensitive to SEU. For instance, when the logic stores in A, B, C, D are 0, 1, 0, 1, if a ray of radiation strikes *P1* and flips the voltage from 0 to 1, node A consequently turns on *N2* and *N3*, so *N2* and *N3* are able to pull node A and C down to very low voltage (pull-down NMOS has higher drivability than pull-up PMOS in SRAM bitcell). Therefore, nodes A, B, C are flipped, and the cell's logic will be flipped. As long as three nodes are flipped in a cell, the cell is not able to recover. Figure 2.7 shows the flipping waveform.

In Quatro bitcell there are two nodes that are sensitive to SEU. When the logic state is 0, 1, 0, 1, node A is sensitive to  $0 \rightarrow 1$  upset. When the logic state is 1, 0, 1, 0, node B is sensitive to  $0 \rightarrow 1$  upset.

Figure 2.7 Quatro cell is upset because Node A is flipped from 0 to 1

# **Chapter 3 Soft Error Resilience Layout Technique**

Using layout design to improve radiation tolerance of a design is one of the common approaches in the research community. In this chapter, several layout design techniques are introduced. Section 3.1 introduces charge sharing and pulse quenching mechanisms. Section 3.2 introduces interleaving and guard contact. Section 3.3 introduces LEAP technique.

#### 3.1 Charge Sharing and Pulse Quenching

Charge sharing is a physical mechanism when a ray of radiation deposits charge in the circuit, the charge can affect many transistors in the vicinity of the striking spot because the transistors now are becoming very small. And pulse quenching is a mechanism that charge sharing is being taken advantage of to reduce the pulse width of SET in combinational logic circuits.

#### 3.1.1 Charge Sharing

When an energetic particle strikes a circuit node, the charge will be deposited at the N+/P+ drain area or silicon substrate via direct or indirect ionization. The total charge collected at a struck node is the sum of drift, diffusion, and bipolar amplification components. As a result of the interaction between the energetic particles and silicon, the charge deposited is subject to charge sharing with other nodes in proximity. Especially in advanced (sub-100 nm) technology, the nodal spacing and capacitance become very small, and the critical charge that is required to upset a logic also lessens. So RHBD design that used to have soft error protection against SEU doesn't have the same

effectiveness in advanced process and technology. For instance at legacy technology, DICE-FF used to have orders of magnitude difference in failures-in-time (FIT) rates when compared to the D flip-flop (DFF), but due to charge sharing, at 40 nm technology, DICE-FF exhibits only 1.4X improvement over the DFF in neutron and proton environments [37]. The details of charge sharing have been described in [29] [38]-[41].

In scaled bulk CMOS technologies, the close proximity of transistors at the nanometer scale means that the charge track may encompass multiple transistors on an integrated circuit (IC). Multiple SETs in a circuit will be generated simultaneously when multiple transistors collect charge from a single ion hit. These multiple transients may or may not interfere with each other depending on the electrical relationship between the associated nodes.

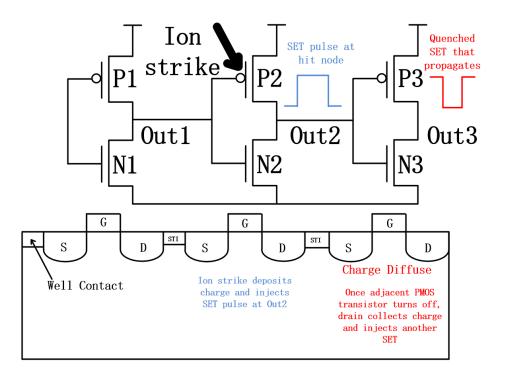

# 3.1.2 Pulse Quenching

Conventionally, charge sharing is viewed as a mechanism that is detrimental to the reliability of microelectronics, but recently a phenomenon called "pule quenching" was discovered and used to take advantage of charge sharing to mitigate the soft error rate of combinational logic circuits [42]-[44]. This technique can be utilized to reduce the pulse width of SET. For combinational logic circuits, where transistors in close proximity are usually electrically related, the SETs generated at two nodes can interfere with each other to alter the overall SET pulse observed at the output of the circuit [45]. When the electrically coupled nodes charge simultaneously, pulse quenching effects [42] reduce the overall SET pulse width partially or completely, which results in decreased SE vulnerability. In analog or digital circuits, the charge sharing effects can be used

intentionally to reduce the SET pulse widths, resulting in lower overall circuit vulnerability [46], [47].

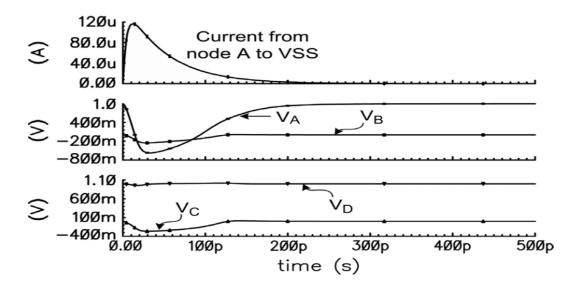

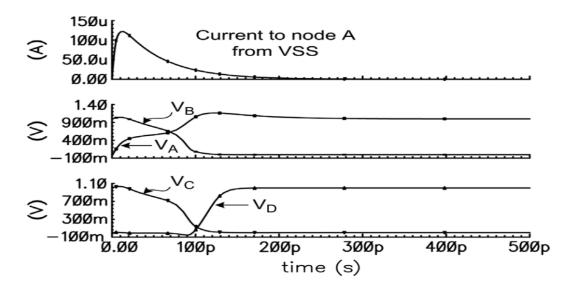

Figure 3.1 shows a schematic of a three-stage inverter chain. Out1, Out2, and Out3 are the outputs of the three inverters (Inverter1, Inverter2, and Inverter3) respectively. As shown in the figure, assuming a voltage 0 is the input to the chain; Out1 is voltage 1, Out2 is voltage 0, and Out3 is voltage 1. In this scenario, N1, P2 and N3 transistors are off and they are very vulnerable to radiation strike. When a ray of radiation strikes P2 transistor, an upward transient will be generated at Out2 (shown as the blue transient). This transient at Out2 will propagate to Out3 and Out3 will produce a downward transient that has the same pulse width.

If P3 transistor is placed close enough to P2 transistor, P2 will also be affected by the radiation. In fact, when P3 is affected by the radiation, it is beneficial in helping reduce the pulse width at Out3 because when N3 is turned on by the upward transient, P3 can collect a positive charge to fight against the downward transient at Out3. Therefore, the pulse width at Out3 (shown as the read transient) is smaller than Out2. This phenomenon is called "pulse quenching" (the pulse width at Out3 is truncated).

The effect of pulse quenching depends on the proximity of P2 and P3 and the technology that is being used. There are layouts that specifically take advantage of this phenomenon.

Figure 3.1 Two-dimensional slice of three PMOS transistors depicting the electrical signal and the charge sharing signal caused by an ion strike

# 3.2 Interleaving and Guard Contact

Interleaving is one of the most common ways of designing layout of SRAM. And placing guard contacts is also a conventional way in designing the layout to reduce the soft error rate.

#### 3.2.1 Interleaving

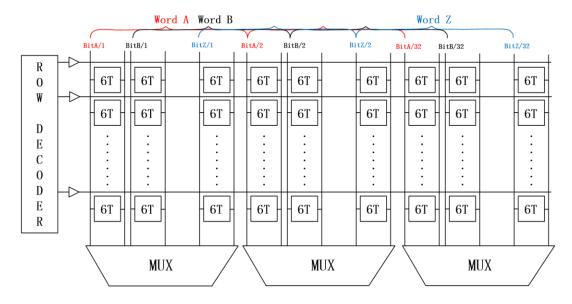

For memory design, the collision of high-energy particles with semiconductor atoms may affect multiple cells. A Multiple Cell Upset (MCU) occurs when a single energetic particle affects two or more bits in the same data word. Bit interleaving technique eliminates MCU events from a single particle hit in SRAMs. Bit interleaving arranges SRAM words in a way that an adjacent bit in the same word is not placed together in the

layout, so that physically adjacent bit lines are mapped to different words. The bit interleaving technique separates two consecutive bits mapped to the same word and replaces with a bit from another word. If the bit interleaving distance is greater than the spread of a multiple cell hit, it results in multiple Single Bit Upsets (SBUs) in multiple words instead of an MBU in a single word. In a bit-interleaved memory, the single-bit error correction algorithm can be used to detect and correct all errors. Figure 3.2 shows the basic structure of interleaving SRAM array.

Figure 3.2 Schematic of an interleaving SRAM

Figure 3.3 Schematic of a non-interleaving SRAM

As can be seen from Figure 3.2, when radiation strike Bit A/1 and charge are shared by adjacent bits, Bit A/2 will not be affected because Bit B/1 is the cell that is placed adjacent to Bit A/2. So Bit A/1 and Bit B/1 are flipped by radiation, but they can easily be corrected by ECC. This is how bit interleaving is advantageous when an MCU occurs. In non-interleaved memory array (Figure 3.3), when an MCU occurs, adjacent cells in the same word may be affected. When the system reads this word, single-bit ECC cannot correct it, which leads to data corruption.

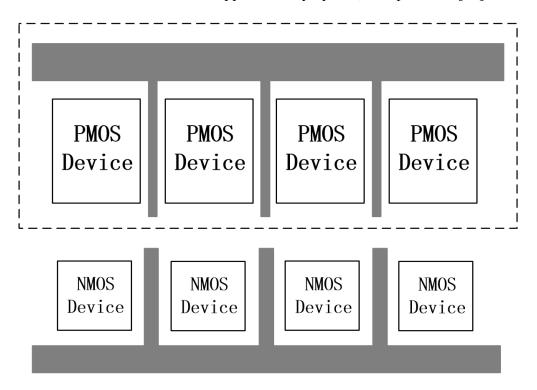

#### 3.2.2 Guard Ring and Guard Drain

Guard ring is a layout technique that uses P+ (N+) diffusion region to surround the N-well (P-substrate), so that the charge collected by the nearby drain node can be minimized. The illustration of guard ring is shown in Figure 3.4. As can be seen from the figure, PMOS and NMOS transistors are surrounded by P+ tap and N+ tap respectively,

and vdd and gnd are applied on P+ tap and N+ tap respectively. By surrounding the PMOS and NMOS transistors, area penalty will be incurred. Guard ring is very effective in mitigating the soft error rate for PMOS device, but it doesn't offer significant improvement for NMOS device. This is because the mechanism of SEU is bipolar effect for PMOS, and for NMOS, drift and diffusion are the major mechanisms. By placing the P+ diffusion around the PMOS and applying vdd voltage, the potential of the N-well can be maintained at a high voltage and it is harder for radiation to lower the N-well potential, therefore the bipolar effect is reduced. By using the guard ring, the soft error rate of PMOS device can be reduced approximately by half, as reported in [48].

Figure 3.4 Illustration of layout for guard ring

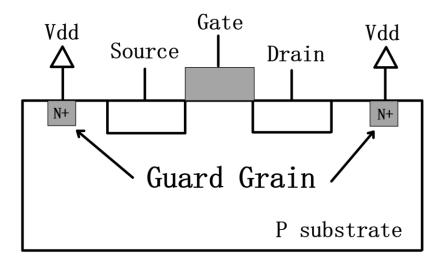

For NMOS device, guard ring is not effective because of drift and diffusion. Another technique called guard drain is proposed. This technique was first developed by Gambles and other researchers at the Microelectronic Research Center (MRC) at the University of

New Mexico and this technique has also been used in design projects by MRC and its successor, the Center for Advanced Microelectronics & Bio molecular Research (CAMBR) at the University of Idaho [49]. It is similar to guard ring in that layout, N+ tap is also used to surround the NMOS device. However, instead of applying gnd on N+ tap, vdd is applied. In this way, a reversed biased PN junction is formed in the P-substrate. This reversed biased PN junction will collect charge when radiation strikes nearby nodes and the charge that are deposited at the drain node will be reduced. A cross section view of the guard drain technique is illustrated in Figure 3.5.

Figure 3.5 Cross section view of layout for guard drain

#### 3.3 Layout Design Through Error Aware Transistor Positioning (LEAP) Technique

Recently a new layout design technique named "Layout Design Through Error Aware Transistor Positioning (LEAP)" was proposed in [30] [31]. The LEAP technique is based on the following procedure:

- (1) Analyze the circuit response to a single event for each individual drain contact node in the layout [50].

- (2) Place each drain contact node in the layout based on the above analysis, such that multiple drain contact nodes act together to cancel (fully or partially) the overall effect of the single event on the circuit [50].

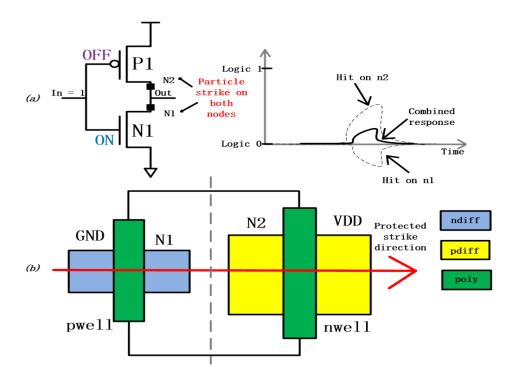

LEAP is a technique that doesn't require changes on the circuit's schematic. Only by changing the layout and poisoning PMOS and NMOS transistors in a particular way can the soft error rate of the circuit or the system be drastically reduced. The following explains of basic mechanism of LEAP.

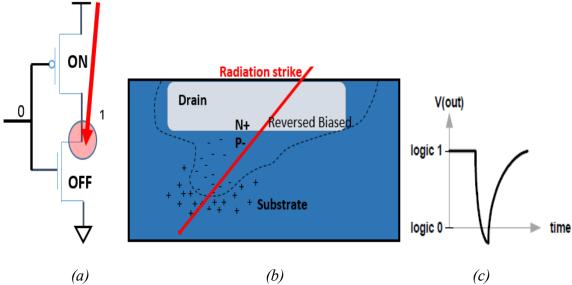

Take an inverter for example as shown in Figure 3.6 (a). The input of the inverter is 0 and the output is 1, therefore the NMOS transistor is reversed biased. When a ray of radiation strikes the drain area of NMOS, the ionized charge will be collected by the reversed biased PN junction. For a reversed biased PN junction in NMOS transistor, the N+ drain will collect the negative charge and the positive charge will deposit in the P-substrate, as shown in Figure 3.6 (b). Therefore all the negative charge in the drain area will generate a current spike which results in a downward voltage transient at the output, as shown in Figure 3.6 (c).

Figure 3.6 A downward transient is generated when radiation strike a reversed biased NMOS transistor

For the PMOS transistor, it is a similar situation. Take the same inverter as shown in Figure 3.7 (a). The input of the inverter is 0, and the output is 1, therefore the PMOS transistor is zero biased. If a ray of radiation strikes the drain area of PMOS, the zero biased PN junction will also collect charge. For zero biased PMOS transistor, P+ drain will collect the positive charge and negative charge will deposit in N- substrate, as shown in Figure 3.7 (b). The collected positive charge in P+ drain will generate a current spike, which results in an upward voltage transient in the output, as shown in Figure 3.7 (c).

Figure 3.7 An uprising transient is generated when radiation strike a zero biased PMOS transistor

So the LEAP technique essentially places the NMOS and PMOS in certain position so that the radiation is likely to affect both of them at the same time. The negative charge collected by the NMOS and the positive charge collected by the PMOS can (partially or fully) cancel each other, therefore the risk of SET and SEU can be reduced. Illustrated in Figure 3.8 (a), the input of the inverter is 1 and output is 0. When a ray of radiation affects the drain area of NMOS and PMOS simultaneously, the SET spike is reduced. The waveform shows the reduced spike (solid curve) as opposed to original spike (dash curve) in the waveform. Figure 3.8 (b) shows the layout of the inverter when they are affected by the radiation. They are aligned horizontally so that the charge cancellation can be very prominent in this direction.

Figure 3.8 LEAP principle for an inverter with transistor alignment. (a) Reduced charge collection when a particle hits both NMOS and PMOS drain nodes of an inverter simultaneously. (b) Transistor alignment to reduce charge collection in the horizontal direction

The effectiveness of LEAP has been thoroughly evaluated in [32] [33] [50]. In 180 nm technology, a LEAP-DICE flip-flop demonstrated 5X better soft error rate than regular DICE flip-flop and 2000X better than regular D flip-flop. It has 40 % area overhead compared to regular DICE flip-flop [32]. In 28 nm bulk technology, LEAP D flip-flop has reduced soft error up to 4X compared to regular D flip-flop, and LEAP DICE flip-flop has reduced soft error over two folds [33].

# **Chapter 4 Proposed SRAM Bitcell Structure**

In the chapter, the proposed SRAM bitcell is presented and the basic read and write operation are illustrated in section 4.1. Section 4.2 discusses the SPICE simulation on the soft error correction capability of the proposed bitcell. Read and write operation speed, and static power consumption are analyzed in section 4.3. Section 4.4 discusses the layout design and the implementation of LEAP technique. Section 4.5 presents the simulation soft error robustness evaluation results of the proposed and make comparison to 6T and Quatro bitcell.

## 4.1 Proposed SRAM Bitcell and Basic Operation

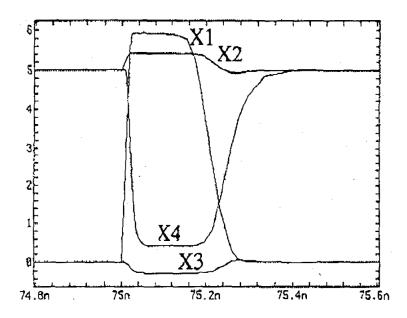

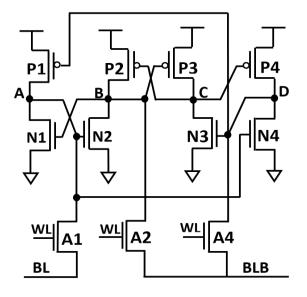

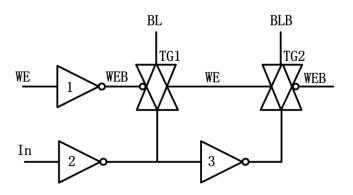

The proposed SRAM Bitcell design is shown in Figure 4.1. It is composed of 11 transistors, and four nodes A, B, C, D are used to store two stable logic states (1010 and 0101), like DICE and Quatro. A positive feedback mechanism between A, B, C and D is used to maintain the states. The detailed analysis of the bitcell structure is as follows:

Figure 4.1 Proposed 11T cell

As shown in Figure 4.1, there are four internal nodes A, B, C, and D. Each node is driven by a pair of pull-down NMOS and pull-up PMOS transistors. Nodes A, B, C, D are driven by P1,N1 pair, P2, N2 pair, P3,N3 pair and P4,N4 pair respectively. Node A connects to N2 and N4 transistor, node B connects to N1 and P3 transistor, node C connects to P2 and P4 transistor, and node D connects to N3 and P1 transistor. Three access transistors A1, A2, A4 are connecting to nodes A, B, D respectively, and they will be turned on in read and write operation. BL is connected to A1, and BLB is connected to A2 and A4. The proposed 11T cell is an asymmetrical structure, but it has differential read and write capability. It should be noted that the 11T cell adopts the features of a Quatro cell in terms of interconnection topology between four pull-up transistors P1-P4 and four pull-down transistors N1-N4. It is noted that, nodes A and B are the outputs of a Cascode Voltage Switching Logic (CVSL) structure, so are nodes B and C. Another way of looking at this structure is that node A connects to the gates of two pull-down NMOS transistors, and node C connects to the gates of two pull-up PMOS transistors, respectively. Nodes B and D both connect to the gate of one pull-down NMOS and the gate of one pull-up PMOS transistor.

There are two logic states that can be stored in the cell (1010 and 0101), so the voltage of node A and C are always complementary to node B and D. Supposed node A and C store voltage 1, node A will turn on N2 and N4 and node C will turn off P2 and P4. So node B and D are disconnected from the VDD and connect to GND, which make their voltage 0. So this is the positive feedback between the four internal nodes, even though it is an asymmetrical structure, it is a similar situation in another logic state when node A and C store voltage 0.

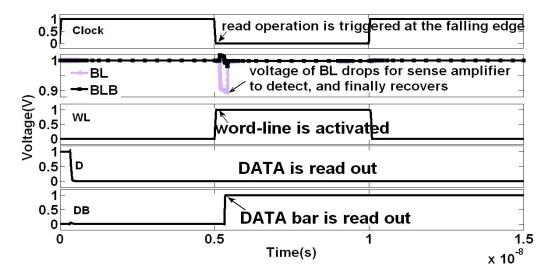

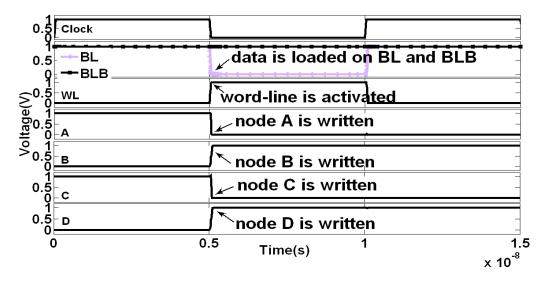

In the following analysis, for clear explanation, we define "STATEO" as {A, B, C, D} = {0, 1, 0, 1}, and "STATEI" as {A, B, C, D} = {1, 0, 1, 0}. For "STATEO", in read operation, BL and BLB are pre-charged to high voltage in the first half of the cycle. And then the word-line WL signal turns on AI, A2 and A4 transistors, node A starts to discharge BL while BLB remains at high voltage. To ensure a stable read operation, pull-down transistor NI should have larger drivability than access transistor AI, so NI can drive BL from "1" to "0" and not the other way. The differential read situation resembles the 6T cell's, and a Cell Ratio (CR)  $(W_{NI}/L_{NI})/(W_{AI}/L_{AI})$  between 1.25 and 2.5 should be sufficient to ensure a stable read [51]. Similarly, in "STATEI", node B and D will discharge BLB, so N2 and N4 transistors should have larger drivability than A2 and A4 transistors. Figure 4.2 shows a complete read operation of the 11T cell.

As shown in Figure 4.2, at the first half of the clock cycle when the voltage of the clock signal is high, BL and BLB equal 1, and WL signal is turned off. At the falling edge of the "Clock" signal (starting second half of the clock cycle), the word-line (WL) is activated and BL starts to be pulled down by transistor N1. After BL drops to a certain voltage, the sense amplifier is triggered and generates outputs "D" and "DB". The content of the cell is read out. How long does the sense amplifier wait before it is triggered depends on how fast does the differential voltage is developed between BL and BLB. The waiting time of sense amplifier can be controlled by designer and the wait time can be drastically different in various operation voltages.

Figure 4.2 Simulation waveforms of a read operation

In the write operation, instead of pre-charging *BL* and *BLB*, two bit lines will be loaded with values to be written. For example, when trying to write "*STATE0*" into the cell, *BL* will be pulled down to "0", and *BLB* will be charged up to "1". After the access transistors are turned on, the value can be loaded into the bitcell.

Contrary to the read operation, *BL* and *BLB* in write operation need to drive the data into the nodes. So the battle between access transistors and pull-up transistors dictates that access transistors *A1*, *A2*, *A4* should have larger drivability than transistors *P1*, *P2* and *P4*. Also, the reason of these three access transistors are needed is that when writing "STATE0" to the cell, "1" must be written to both node B and D before "0" can be written to node C. When three nodes are written, the cell's logic is changed. It is a similar situation when trying to write "STATE1" to the cell, but at this time *BLB* needs to pull down the voltage of two nodes (B and D). Therefore, in order to ensure a good write speed, *P2* and *P4* transistors can be downsized a bit (reduce channel width or increase channel length), so that the voltage of node B and D can be pulled down fast enough

through A2 and A4. But overall, since BLB is driving two nodes in each cell while BL is only driving one, the operation on BLB is relatively slower than BL when a large number of cells are connecting to the bit line.

A complete write operation is shown in Figure 4.3. At the first half of the clock cycle when the voltage of clock is high, WL is turned off, BL and BLB are pre-charged to high (the same as read operation so far). At the falling edge of "Clock" signal (starting the second half of the clock cycle), BL and BLB are loaded with the data value and WL is activated. As soon as WL is activated, BL and BLB can drive the data into the internal node. As shown in the diagram, expected values are all written into A, B, C and D. The write operation speed largely depend on the ratio between access transistors and pull-up transistors.

Figure 4.3 Simulation waveforms of a write operation

## **4.2 SEU Correction Capability**

One of the most important features of the proposed bitcell is the error correction capability. When a ray of radiation strike a sensitive drain area and flip the voltage of a node, the other nodes can correct the corrupted nodes. To evaluate the soft error correction capability and robustness of the proposed design, all SEU scenarios are examined exhaustively. In SPICE simulation, an exponential current source is commonly used to simulate single event upset scenario by injecting current to flip the voltage of a certain node. The current is proportional to the charge being defined in the current source. The following analysis is done in Cadence Spectre Simulator.

### (1) Node A:

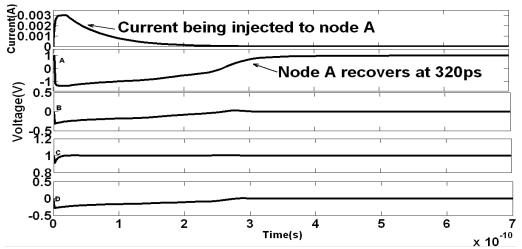

In "STATE1" (A, B, C, D = 1, 0, 1, 0), if the drain of N1 transistor is hit by a particle, node A is flipped from "1" to "0", which can be done by inducing a current going out of node A. In "STATE1", P1, P3, N2, N4 are turned on and N1, N3, P2, P4 are turned off initially. After node A is flipped from "1" to "0", node A turns off N2 and N4, therefore N2, P2 and N4, P4 transistors pairs are all off at this moment, but the logic of node B and D can maintain for a long time and therefore are considered unaffected. The collected negative charge at node A can be easily drained by voltage supply through P1 after the transient current is gone. Hence node A can recover to "1". How fast can node A recover depends on strength of P1 and how much charge is deposited in the drain area of N1. In Figure 4.4, it shows that when a double exponential current pulse with 300 fC charge is injected to node A, the value can be recovered in less than 350 ps.

Figure 4.4 Recovery simulation waveforms of internal node A, B, C, D when A is subjected to "1 -> 0" upset

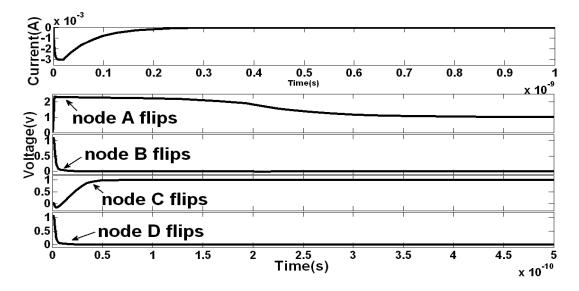

In "STATE0" (A, B, C, D = 0, 1, 0, 1), if the drain of PI is hit by a particle, Node A is flipped from "0" to "1". N2 and N4 transistors will be turned on. As a result, B and D are both pulled from "1" to "0" (pull-down NMOS transistors always win the battle). This is the worst situation and the cell is totally flipped. When three nodes are flipped in the cell, the value is not able to recover. Figure 4.5 shows the flipping of the cell content when node A is flipped from "0" to "1".

Figure 4.5 Simulation waveforms show that the whole cell flips when node "A" is subjected to "0 -> 1" SEU

## (2) Node B:

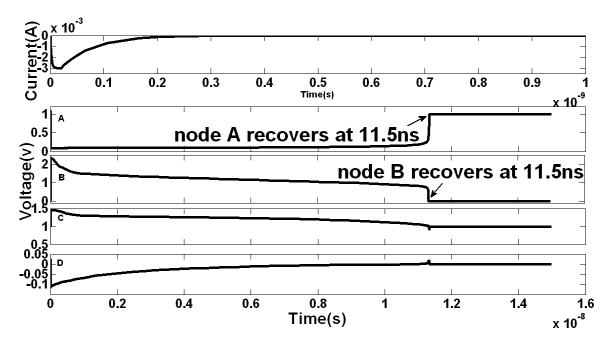

In "STATEI", if the drain of P2 is hit by a particle, node B is flipped from "0" to "1". In this situation, NI will be turned on, and NI and PI are on at the same time. Because NI has larger drivability than PI, it pulls node A from "1" to a very low voltage. Node A consequently turns off N2 transistor and makes it harder for node B to recover back to logic "0". This is an undesirable positive feedback in CVSL. Eventually node B can recover through the leakage current, and node A recovers back to "1" after node B recovers and turns off NI transistor. When  $(W_{PI}/L_{PI})/(W_{NI}/L_{NI})$  is increased, it will be beneficial for node A recovery because PI has more strength in fighting against NI. In Figure 4.6, simulation result shows that when  $(W_{PI}/L_{PI})/(W_{NI}/L_{NI}) = 0.6$ , it takes 11.5 ns to recover.

Figure 4.6 Simulation waveforms show that node B takes 11.5 ns to recover from "0 -> 1" SEU

In "STATEO", if the drain of N2 is hit by a particle, node B is flipped from "1" to "0". In this situation, P3 is turned on, but node C is only slightly affected and can maintain at "0" (N3's drivability larger than P3). Also node A is not affected. Hence, node B can recover to "0" as long as the transient current is gone.

#### (3)Node C:

In "STATE1", when node C is flipped from "1" to "0", P2 and P4 are both turned on. But node B and D are also only slightly affected, because N2 and N4 are on and they maintain the voltage of B and D at "0". Hence, node C can recover to "1" as long as the transient is gone. Simulation shows that node C can recover back to "1" in less than 400 ps when 300 fC charge are injected.

In "STATEO", when node C is flipped from "0" to "1", P2 and P4 are turned off. In this situation, because node B and D are not affected, node C can recover very fast after current transient is gone.

#### (3)Node D:

In "STATE1", when node D is flipped from "0" to "1", N3 is turned on and P1 is turned off. In this situation, node C is pulled down from "1" to "0". But node A and B are not affected and can maintain at "1" and "0" respectively. After the transient is gone, because N4 is driven by node A, node D can be pulled back to "0". Once node D recovers, node C can recover back to "1". The whole cell can recover in 300 ps when 300 fC charge are injected.

In "STATEO", when node D is flipped from "1" to "0", P1 is turned on and N3 is turned off. In this situation, since node A is only slightly affected and node C can maintain at "0" for a long time, node D can recover very fast.

In conclusion, for single node upset, all of the nodes are able to recover from "1->0" upset very quickly. But for "0->1" upset, node A and B are relatively vulnerable. Node A is the only node that is not able to recover from "0 -> 1" upset. Node B can recover, but takes longer time.

# 4.3 Read & Write Speed, Power Consumption and Area Overhead

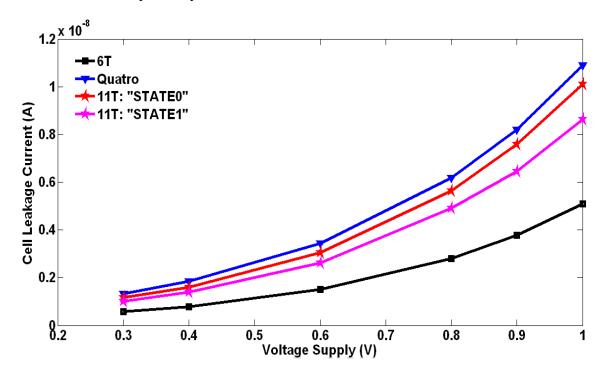

The leakage power is measured for proposed 11T, Quatro and 6T cell in TSMC 65 nm CMOS technology to compare static power consumption. As shown in Figure 4.7, the 6T cell has the lowest leakage current in all range of voltage supply. The proposed 11T cell's leakage current is approximately 10 % and 22 % lower than Quatro cell, in "STATEO" and "STATEI" respectively.

Figure 4.7 Leakage current of 11T, Quatro and 6T cell

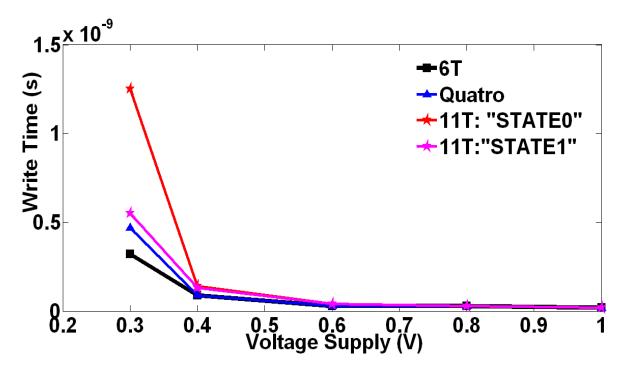

In this thesis, the write time is defined as the time interval from the active word line edge crossing 50 % voltage supply to the time when the data is written. Figure 4.8 shows the write time of 6T, Quatro and 11T cells at different power supply voltages. When voltage supply is larger than 0.6 V, 6T, Quatro and 11T cell (both states) all have the same write time. But as voltage scales down under 0.6 V, 11T has longer write time than Quatro and 6T in both states. And 11T cell has longer write time in "STATEO" than "STATEI" at low voltages (less than 0.4 V).

Figure 4.8 Write time of 11T, Quatro and 6T cell

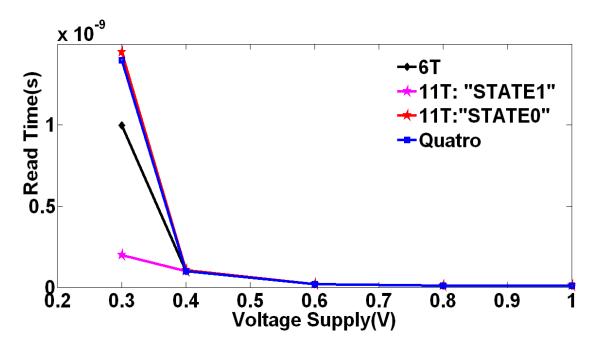

For the read time, it is gauged as the time interval from the active word line edge crossing 50 % voltage supply to bit line developing a 50 mV difference [52]. In Figure 4.9, it shows that, when voltage supply is larger than 0.4 V, 6T, Quatro and 11T cell (both states) all have the same read time. In "STATEO", 11T has almost the same read

time as Quatro in all range of voltage. In "STATE1", as voltage scales under 0.4 V, 11T has the shortest read time.

Figure 4.9 Read time of 11T, Quatro and 6T cell

The area comparisons of different structures (6T, Quatro, Regular 11T and LEAP-11T) which are designed in the test chip are shown in the following Table 4.1. The comparison is normalized with respect to 6T bitcell. The area of Quatro is 1.52 times as big as 6T, and regular 11T is 1.76 times as big as 6T. Regular 11T is 16 % larger than Quatro. It should be noted that here LEAP-11T is also 11T bitcell, but it is using a special layout technique to increase the soft error tolerance. It will be discussed in length in section 4.4. LEAP-11T is 2.03 times as big as 6T, and it is 15 % larger than regular 11T.

Table 4.1 Area Comparison

|                 | 6T     | Quatro-10T | Regular 11T | LEAP-11T   |

|-----------------|--------|------------|-------------|------------|

| Area            |        |            |             |            |

| Comparison (as  | 1 Time | 1.52 Times | 1.76 Times  | 2.03 Times |

| opposed to      |        |            |             |            |

| traditional 6T) |        |            |             |            |

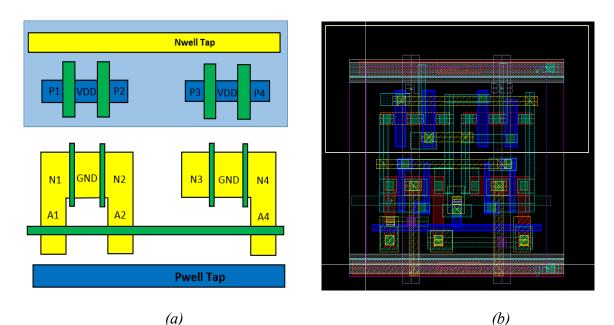

## 4.4 Layout Design and LEAP Implementation

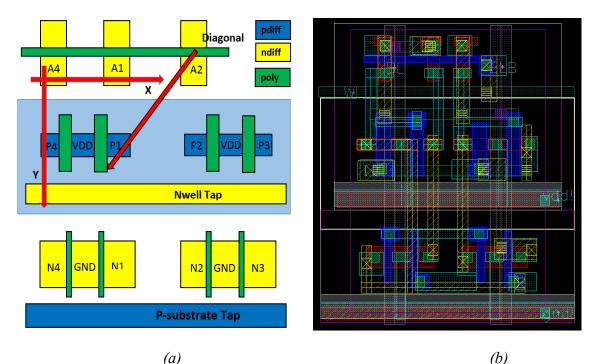

The layout design of 11T bitcell is done in the most compact manner in order to reduce the area penalty. Figure 4.10 (a) is the illustration of 11T layout. The yellow is N type diffusion; blue is P type diffusion and green is poly-silicon. Figure 4.10 (b) shows the layout of the 11T bitcell. P1 and P2 are sharing vdd, N1 and N2 are sharing gnd in order to reduce area penalty, as do P3 and P4, and N3 and N4. The layout is 2.07 µm by 2.11 µm. The layout is designed in TSMC 65 nm bulk technology. The size of the transistors is as follows:

Figure 4.10 (a) Illustration of 11T layout (b) 11T layout in TSMC 65 nm bulk technology

PMOS pull-up transistors: P1: 120 nm/120 nm (Ratio = 1)

P2: 120 nm/140 nm (Ratio = 0.86)

P3: 120 nm/120 nm (Ratio = 1)

P4:

$$120 \text{ nm}/140 \text{ nm}$$

(Ratio =  $0.86$ )

NMOS pull-down transistors: N1: 200 nm/60 nm (Ratio = 3.3)

N2: 200 nm/60 nm (Ratio = 3.3)

N3: 200 nm/60 nm (Ratio = 3.3)

N4: 200 nm/60 nm (Ratio = 3.3)

Access NMOS transistors: A1: 120 nm/60 nm (Ratio = 2)

A2: 120 nm/60 nm (Ratio = 2)

A4:120 nm/60 nm (Ratio = 2)

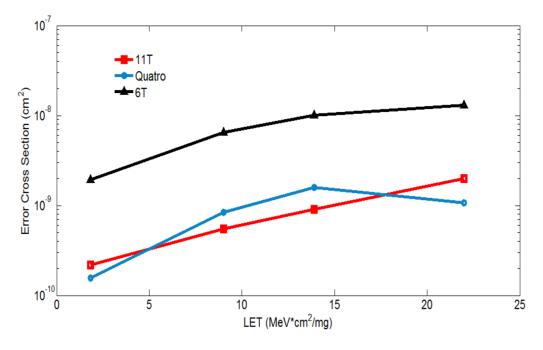

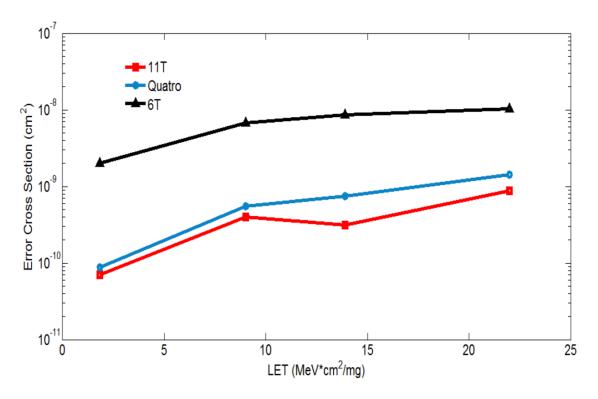

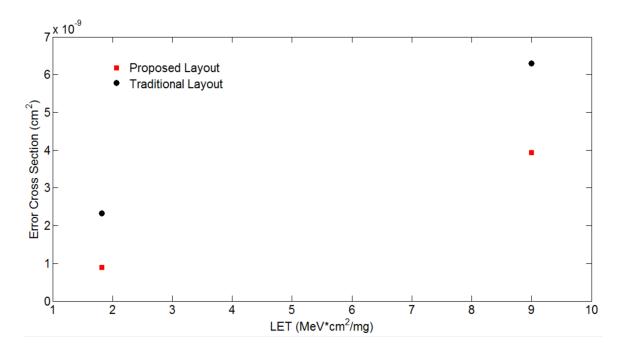

The ratio of pull-down NMOS, pull-up PMOS and access NMOS transistors are chosen in a way that the length of the *P2* and *P4* is increased to 140 nm, unlike *P2* and *P3* being 120 nm. The reason is that drivability of *P2* and *P4* should be scaled down in order to have a good write speed in state 1, as explained in Section 4.1.