# A RECONFIGURABLE INTEGRATED RECEIVER FRONT-END FOR HETEROGENEOUS UNDERWATER SENSOR NETWORKS

by

Ningcheng Gaoding

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

at

Dalhousie University Halifax, Nova Scotia June 2021

## **Table of Contents**

| List of   | f Tables                 | S                                                                                                      | iv                   |

|-----------|--------------------------|--------------------------------------------------------------------------------------------------------|----------------------|

| List of   | f Figure                 | es                                                                                                     | v                    |

| Abstr     | act                      |                                                                                                        | ix                   |

| List of   | f Abbre                  | eviations Used                                                                                         | X                    |

| Ackno     | wledge                   | ments                                                                                                  | xiii                 |

| Chapt     | er 1                     | Introduction                                                                                           | 1                    |

| 1.1       | Potent<br>1.1.1<br>1.1.2 | tial of CMOS Technology for Internet of Underwater Things Challenges in Low-power Receiver IC designs  | $1\\2\\4$            |

| 1.2       | Objec                    | tives and Contributions                                                                                | 7                    |

| 1.3       | Outlin                   | ne of this dissertation                                                                                | 10                   |

| Chapter 2 |                          | Design of a Controllable Low-Frequency Channel Selection Filter                                        | 13                   |

| 2.1       | Chann                    | nel Selection Filters: Background and Challenges                                                       | 13                   |

| 2.2       | Chann                    | nel Selection Filters: Current State of the Art                                                        | 15                   |

| 2.3       | A Low<br>2.3.1<br>2.3.2  | r-power 4 <sup>th</sup> -order Controllable Channel Selection Filter Proposed Filter Topology Analysis | 17<br>18<br>25       |

| Chapter 3 |                          | Design of an Inductor-less Voltage Controlled<br>Oscillator                                            | 29                   |

| 3.1       |                          | n Characteristics for the Proposed VCO                                                                 | 29<br>29<br>30<br>32 |

| 3.2       | Voltag<br>3.2.1<br>3.2.2 | ge Control Oscillator Topologies                                                                       | 32<br>32<br>34       |

| 3 3       | An Ind                   | ductor loss VCO Dosign in the VHF Rand                                                                 | 36                   |

|           | 3.3.1<br>3.3.2<br>3.3.3                     | Active Inductor Design and Analysis                                                                               | 38<br>42<br>46             |

|-----------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------|

| Chapter 4 |                                             | Design of a Continuous-Time $\Delta\Sigma$ ADC Based on Active-Passive Integrators with a Resistance Feedback DAC | 52                         |

| 4.1       | Overvi                                      | iew of Delta-Sigma ADCs                                                                                           | 52                         |

| 4.2       | Param                                       | eters and Performance Metrics                                                                                     | 53                         |

| 4.3       | Oversa<br>4.3.1<br>4.3.2                    | Ampling and quantization                                                                                          | 54<br>54<br>56             |

| 4.4       | Noise                                       | Shaping                                                                                                           | 58                         |

| 4.5       | Delta-<br>4.5.1<br>4.5.2<br>4.5.3<br>4.5.4  | Sigma ADC Architectures                                                                                           | 61<br>63<br>65<br>65       |

| 4.6       |                                             | Order 4-bit Continuous-Time $\Delta\Sigma$ ADC Based on Active-Passive ators with a Resistance Feedback DAC       | 71<br>71<br>73             |

| 4.7       | Circuit<br>4.7.1<br>4.7.2<br>4.7.3<br>4.7.4 | t design of the proposed $\Delta\Sigma$ DAC                                                                       | 80<br>80<br>86<br>89<br>96 |

| 4.8       | Experi                                      | imental Results                                                                                                   | 100                        |

| Chapte    | er 5                                        | Conclusion and future directions                                                                                  | 105                        |

| 5.1       | Conclu                                      | ısion                                                                                                             | 105                        |

| 5.2       | Future                                      | e directions                                                                                                      | 106                        |

| Riblios   | rranhy                                      |                                                                                                                   | 108                        |

# List of Tables

| 2.1 | Performance summary of the proposed filter                  | 26  |

|-----|-------------------------------------------------------------|-----|

| 2.2 | Comparison with previous BPF designs                        | 28  |

| 3.1 | Comparisons with previous VCO designs                       | 49  |

| 4.1 | Behavior model coefficients of the conventional CT DSM      | 74  |

| 4.2 | Behavior model coefficients of the proposed CT DSM          | 77  |

| 4.3 | The summary of the two op amps performances                 | 83  |

| 4.4 | Comparison of the performance with previous CT DSM designs. | 104 |

# List of Figures

| 1.1  | A simplified IoT wireless receiver architecture                                                                                   | 5  |

|------|-----------------------------------------------------------------------------------------------------------------------------------|----|

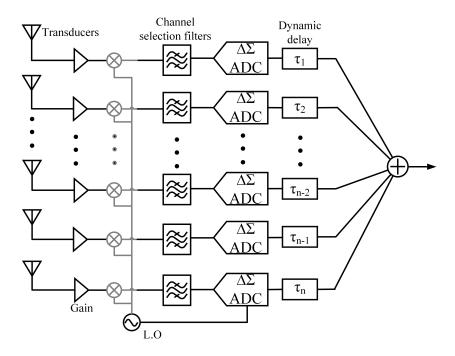

| 2.1  | A beamformer for an ultrasonic sensor array                                                                                       | 15 |

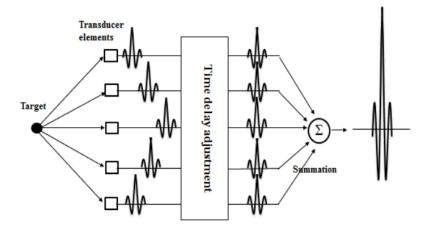

| 2.2  | Sensor architecture utilizing a $gm$ - $C$ BPF                                                                                    | 16 |

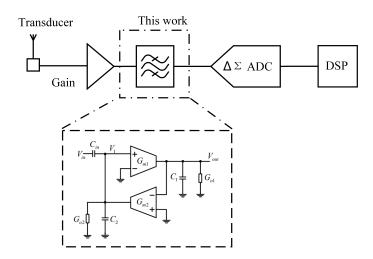

| 2.3  | A proposed BPF with a constant quality factor                                                                                     | 19 |

| 2.8  | Analysis of the 1-dB compression point and of the IIP3 for the proposed filter                                                    | 24 |

| 2.9  | The post-layout simulation against the temperature                                                                                | 24 |

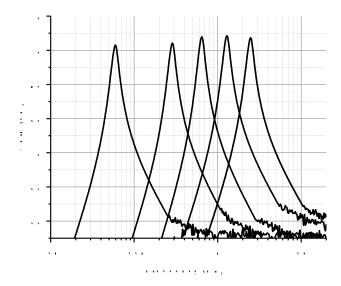

| 2.10 | Simulated frequency response of the two-stage cascaded BPF for different control voltages between $0.35~\rm{V}$ and $0.75~\rm{V}$ | 25 |

| 2.11 | Layout of proposed filter                                                                                                         | 26 |

| 2.12 | Measured IIP3 point of the proposed filter                                                                                        | 26 |

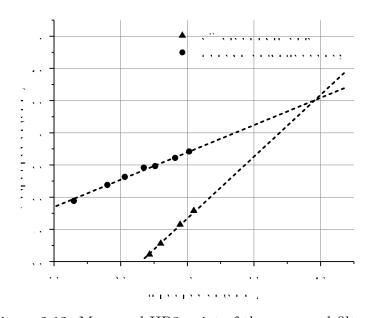

| 2.13 | Measured frequency responses of the $4^{\mathrm{th}}$ -order BPF                                                                  | 27 |

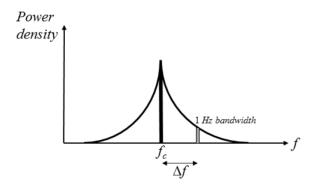

| 3.1  | Diagram of phase noise in a real oscillator                                                                                       | 31 |

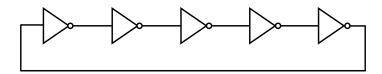

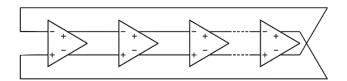

| 3.2  | Single-ended ring oscillator                                                                                                      | 33 |

| 3.3  | Differential ring oscillator                                                                                                      | 33 |

| 3.4  | Ideal LC VCO                                                                                                                      | 34 |

| 3.5  | Parallel LC circuit with losses and active negative resistance                                                                    | 35 |

| 3.6  | LC oscillator with cross-coupled differential pair                                                                                | 35 |

| 3.7  | LC VCO using varactors                                                                                                            | 36 |

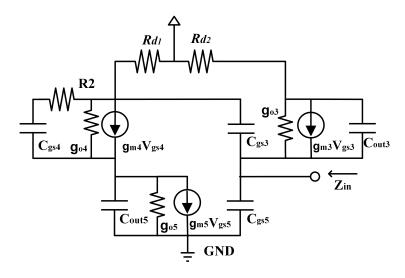

| 3.8  | The active inductor design. (a) The conventional design. (b) The proposed design                                                  | 39 |

| 3.9  | The small signal model and its equivalent RLC                                                                                     | 39 |

| 3.10 | Simulation of the proposed AI under different values of resistor R2                                                               | 40 |

| 3.11 | Simulation of the real impedance of the proposed AI under dif-                                                                    | 12 |

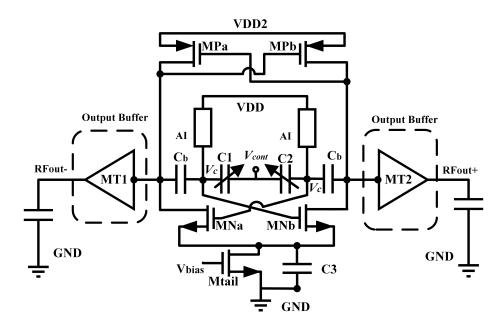

| 3.12 | The proposed VCO topology                                                                                                                                                                                                       | 43 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

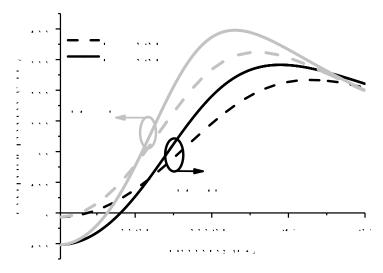

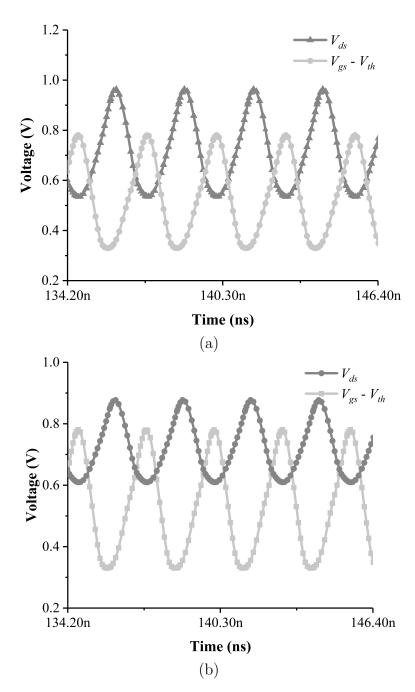

| 3.13 | The transient voltage comparison of the VCO core tank. a, The transient voltage without $C_{\rm b}$ . b, The transient voltage with $C_{\rm b}$                                                                                 | 44 |

| 3.14 | Phase noise performance comparison                                                                                                                                                                                              | 45 |

| 3.15 | Temperature variation simulations of the proposed VCO                                                                                                                                                                           | 45 |

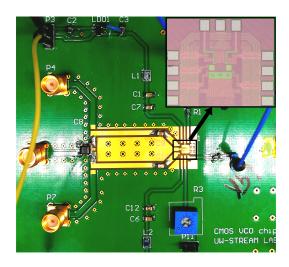

| 3.16 | The layout of the proposed VCO on a printed circuit board                                                                                                                                                                       | 47 |

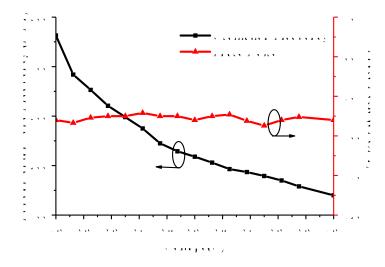

| 3.17 | Characterization of the fundamental tone                                                                                                                                                                                        | 48 |

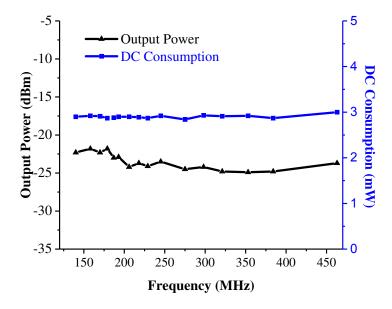

| 3.18 | Output power and DC power consumption                                                                                                                                                                                           | 48 |

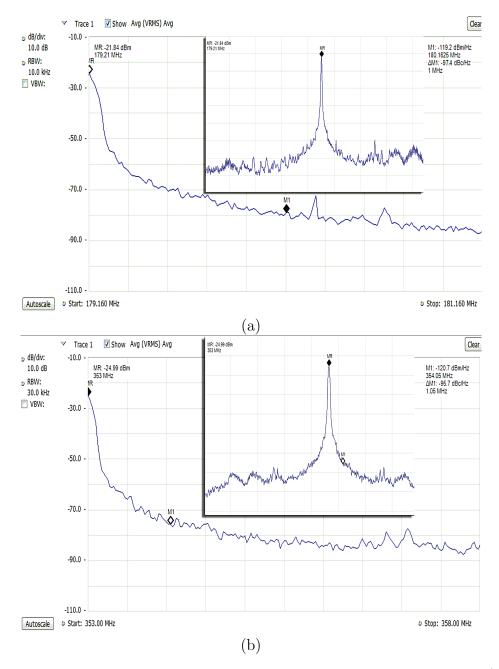

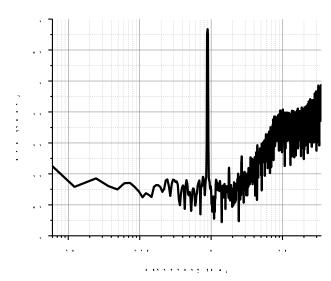

| 3.19 | The measured spectrum and phase noise of the proposed VCO. (a) The measured spectrum and phase noise at 179 MHz. (b) The measured spectrum and phase noise at 353 MHz                                                           | 50 |

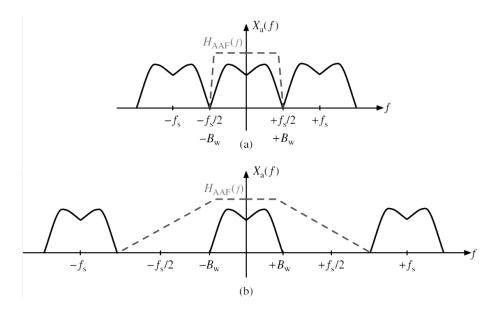

| 4.1  | Sampling spectrum (a) Nyqusit ADC (b) Oversampling ADC.                                                                                                                                                                         | 56 |

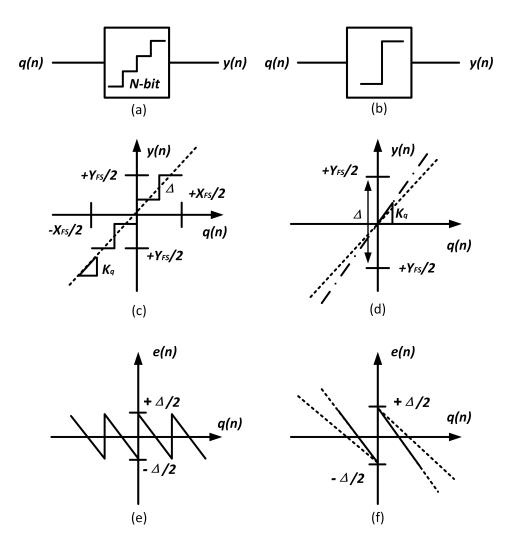

| 4.2  | Quantization diagrams (a) Multi-bit quantizer (b) One-bit quantizer (c) Multi-bit quantizer output curve (d) One-bit quantizer output curve (e) Multi-bit quantizer quantization error (f) One-bit quantizer Quantization error | 57 |

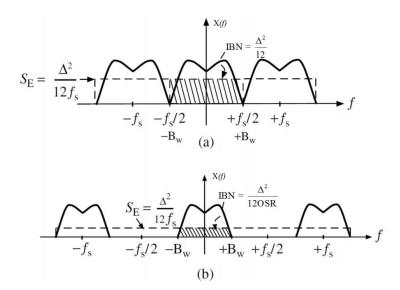

| 4.3  | The relationship between quantization noise power and over-sampling rate (a) Nyquist sampling (b) oversampling                                                                                                                  | 59 |

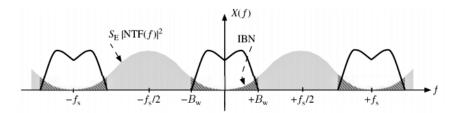

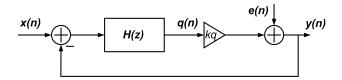

| 4.4  | Diagram of noise shaping                                                                                                                                                                                                        | 60 |

| 4.5  | Single loop Delta-Sigma modulator                                                                                                                                                                                               | 62 |

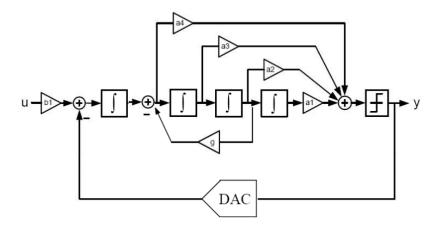

| 4.6  | General CIFF topology                                                                                                                                                                                                           | 63 |

| 4.7  | General CIFB topology                                                                                                                                                                                                           | 64 |

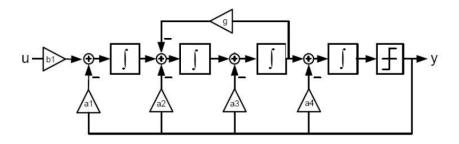

| 4.8  | Comparison of modulator structures (a) The discrete-time model (b) The continuous-time model                                                                                                                                    | 66 |

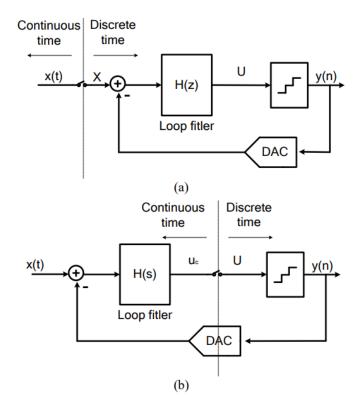

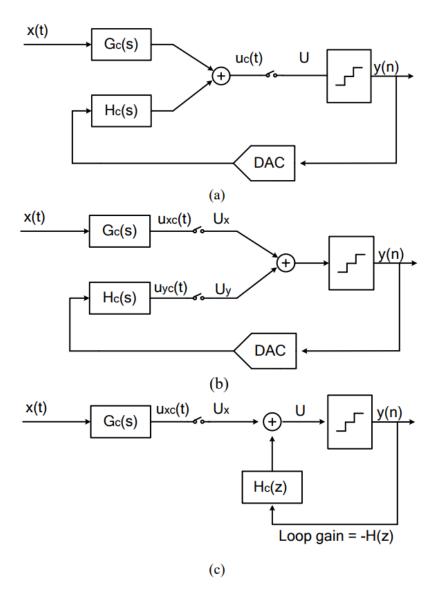

| 4.9  | Three equivalent diagrams to demonstrate the inherent antialiases filter in the continuous time Sigma-Delta Modulator                                                                                                           | 68 |

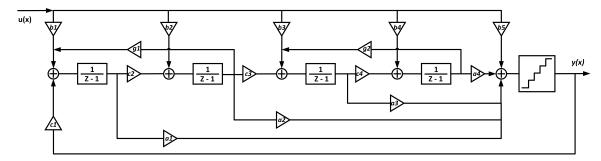

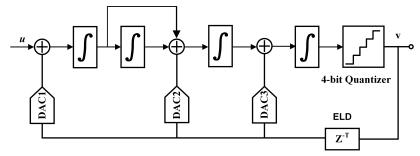

| 4.10 | Behavioral model of 4th-order CIFF topology                                                                                                                                                                                     | 74 |

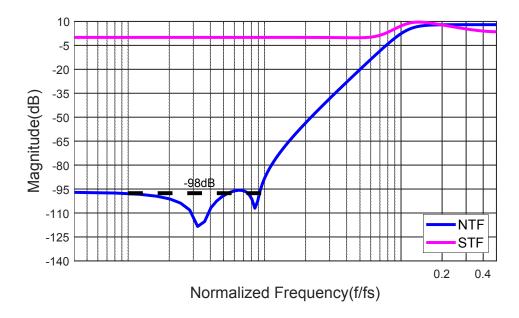

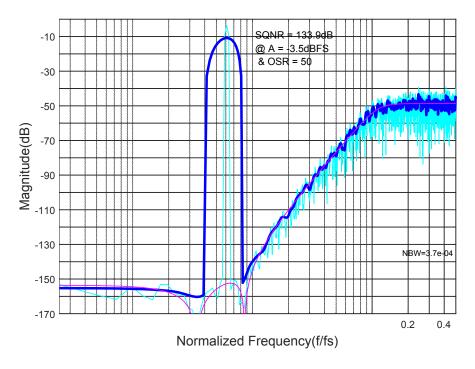

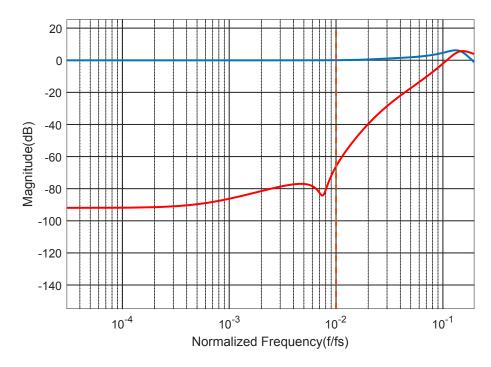

| 4.11 | Simulation of the NTF and STF transfer functions using the behavioural model                                                                                                                                                    | 75 |

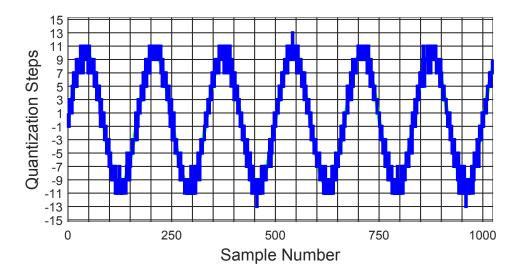

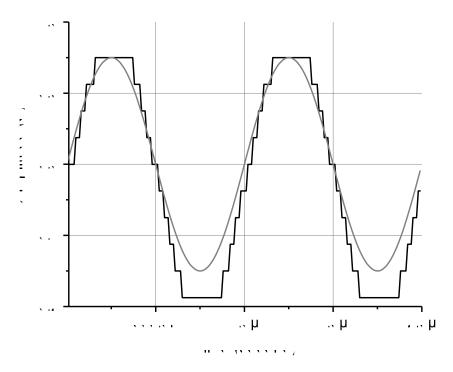

| 4.12 | Transient simulation using the behavioural model                                                                                                                                                                                | 75 |

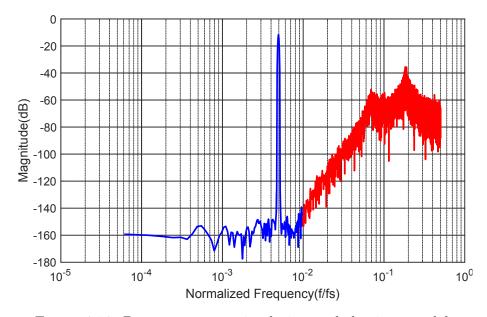

| 4.13 | Power spectrum simulation of the behavioural model                                                                                                                                                                              | 76 |

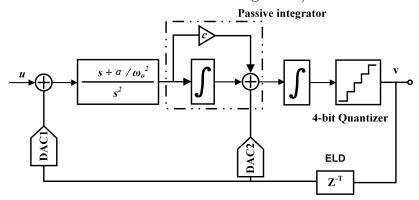

| 4.14 | Modified behaviour model using in this design                           | 77 |

|------|-------------------------------------------------------------------------|----|

| 4.15 | NTF and STF simulation on behaviour model                               | 78 |

| 4.16 | Power spectrum simulation on behaviour model                            | 78 |

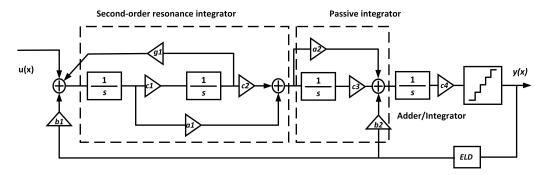

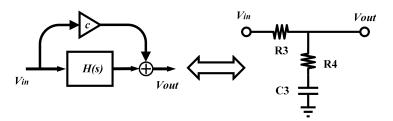

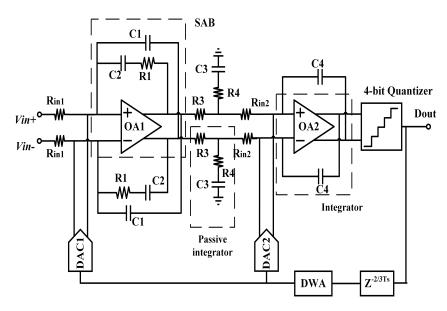

| 4.17 | The system blocks of 4th order $\Delta\Sigma$ Modulator                 | 79 |

| 4.18 | Block diagram of the passive integrator                                 | 80 |

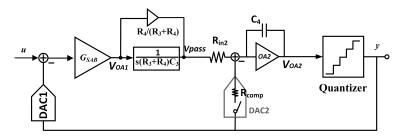

| 4.19 | Block diagram of the proposed CT DSM                                    | 81 |

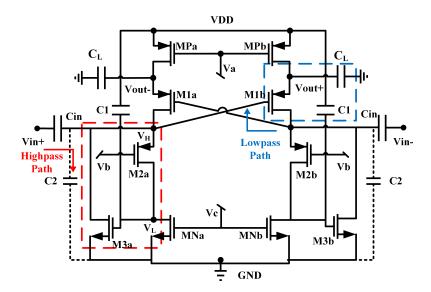

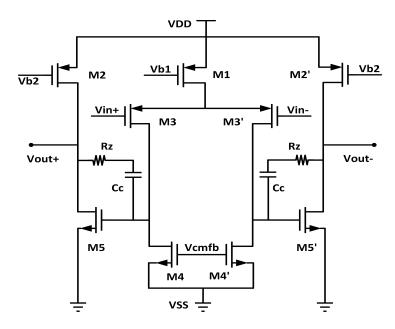

| 4.20 | Schematic of the opamp used in this loop filter                         | 82 |

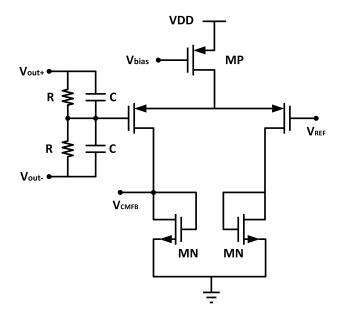

| 4.21 | Schematic of the common mode feedback circuit used in the opamp         | 82 |

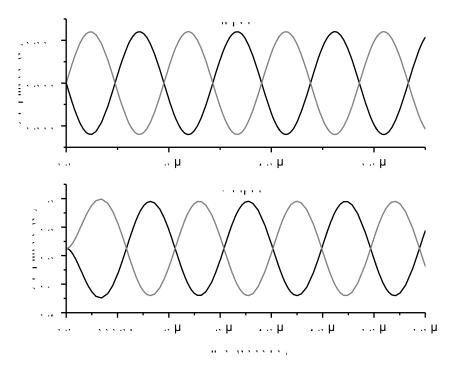

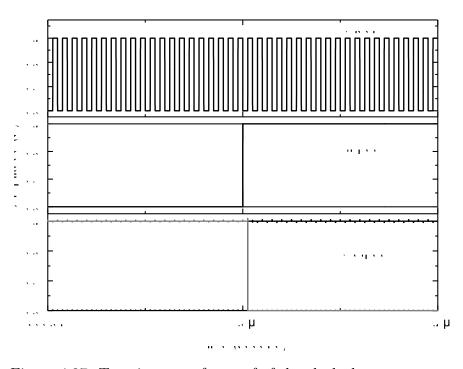

| 4.22 | Transient waveforms of the opamp used in this loop filter               | 83 |

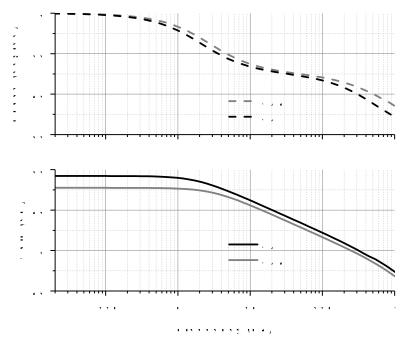

| 4.23 | Bode plots of the opamps used in this loop filter                       | 84 |

| 4.24 | SNR versus opamp unity gain bandwidth and normalized RC product         | 86 |

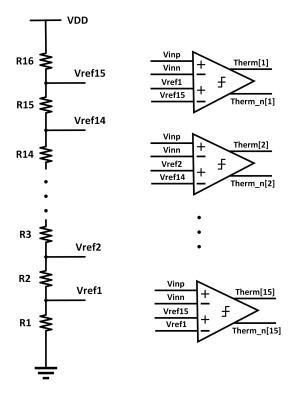

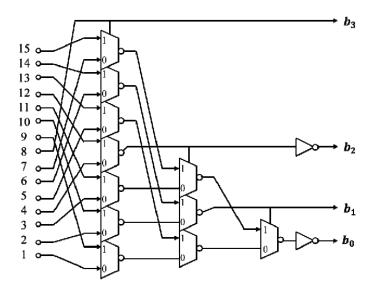

| 4.25 | Structure of the 4-bit flash ADC                                        | 87 |

| 4.26 | Schematic of the clocked comparator                                     | 88 |

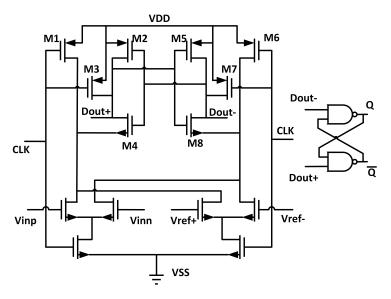

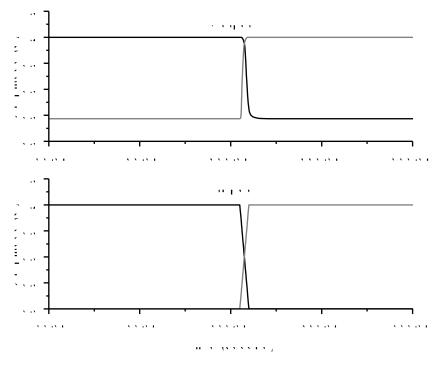

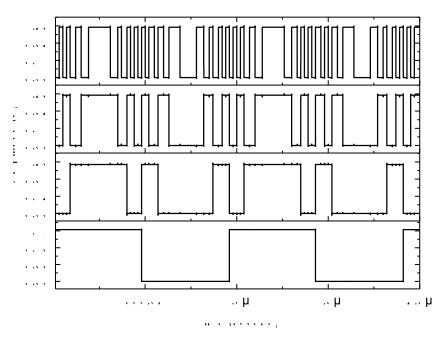

| 4.27 | Transient waveforms of of the clocked comparator                        | 88 |

| 4.28 | Transient waveforms of the 4-bit flash ADC                              | 89 |

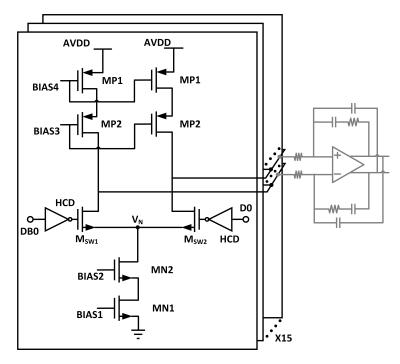

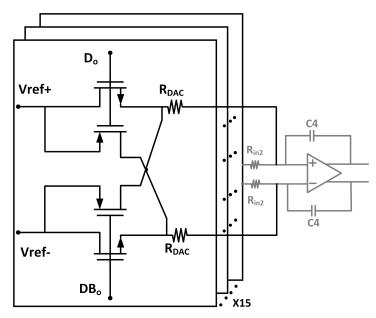

| 4.29 | Schematic of the current-steering DAC                                   | 90 |

| 4.30 | Schematic of the high-cross driver (HCD)                                | 91 |

| 4.31 | Simulated transient waveform of the HCD                                 | 91 |

| 4.32 | Schematic of the low-pass resistance DAC                                | 92 |

| 4.33 | Simplified system diagram with the low-pass filter in the feedback path | 93 |

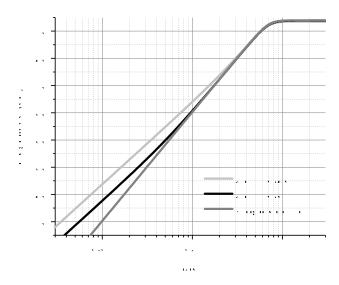

| 4.34 | The NTF comparison for different ARs                                    | 94 |

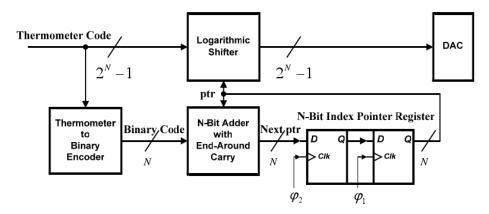

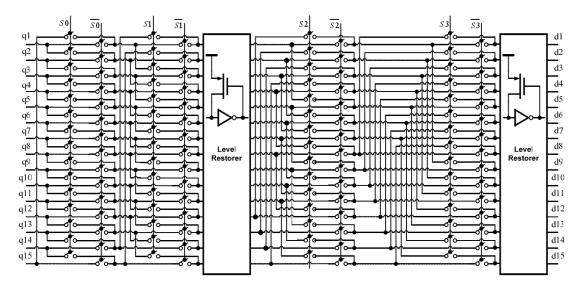

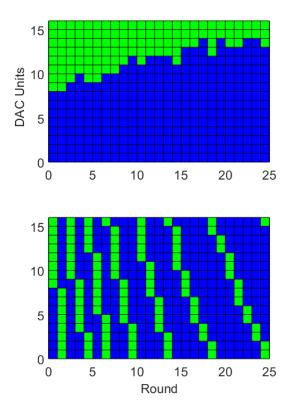

| 4.35 | Implementation of DWA algorithm                                         | 96 |

| 4.36 | Schematic of the encoder                                                | 97 |

| 4.37 | Transient waveforms of the encoder                                      | 97 |

| 4.38 | Schematic of the logarithm shifter                                      | 98 |

| 4.39 | Transient waveforms of the DWA circuit                       | 98  |

|------|--------------------------------------------------------------|-----|

| 4.40 | The selection scheme of the DWA circuit                      | 99  |

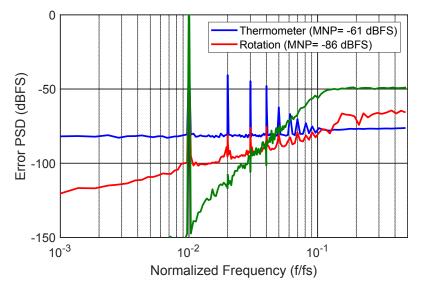

| 4.41 | The mismatch noise shaping effect of DWA circuit             | 99  |

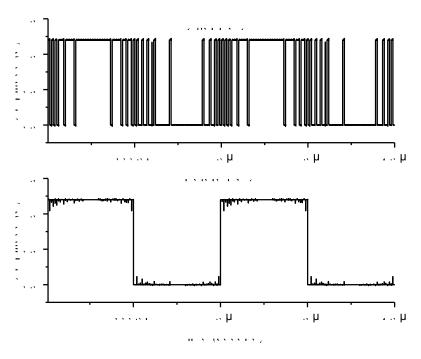

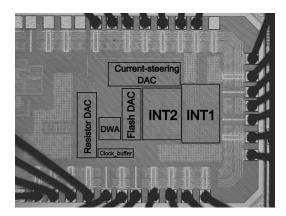

| 4.42 | Chip photograph of the proposed design                       | 100 |

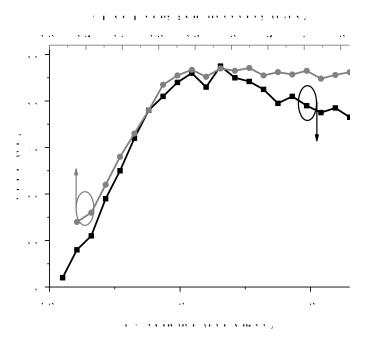

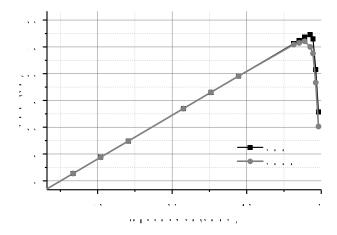

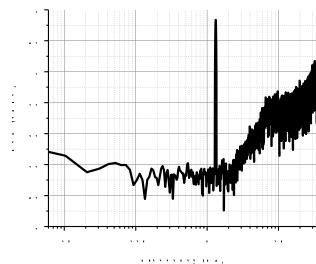

| 4.43 | The measured SNDR and SNR comparison                         | 101 |

| 4.44 | The measured PSD of proposed design at different frequencies | 102 |

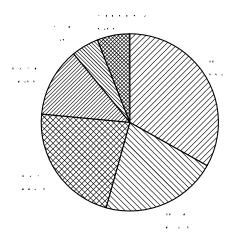

| 4.45 | Power breakdown                                              | 103 |

#### Abstract

With the increased interest in the Internet of Things (IoT), more and more sensors are implemented to satisfy the demand of various applications. In this project, a low power, controllable, high resolution sensor node relying on a  $\Delta\Sigma$  analog to digital converter (ADC) is introduced for IoT applications, and more specifically to enable underwater communication networks that rely on low frequency of operation.

Typically, remote sensors are not required to process the data and they act like relays. As such, those sensors normally require small footprints, low power consumption, narrow bandwidth and are architecturally simple. In this research, a receiver design is proposed, and operates in the acoustic and ultrasonic band. It is intended to be a relay for underwater monitoring, and the device can also be applied for example as a sensor in security system, or in other acoustic and ultrasonic remote control systems. In this design, three key components are described: 1) an inductor-less voltage controlled oscillator, 2) a channel acquisition filter and 3) a continuous-time (CT) Delta Sigma modulator (DSM) ADC. The three designs are implemented in TSMC's 65-nm CMOS technology.

The proposed active inductor (AI) based VCO has already been designed and fabricated. The proposed AI-VCO is compact, has a wide linear tuning range, consumes low-power and exhibits good phase noise performance. It achieves an excellent figure of merit (FOM) around -163 dBc/Hz in comparison to previous designs. The proposed gm-C based channel selection filter is currently finished the design and measurement. The filter can achieve a wide passband range from 60 kHz to 2.5 MHz with an almost constant Q-factor equal to 7.2. The power consumption of this filter is only a few  $\mu$ Watts excluding the digital control cell. Finally, a 4th-order CT DSM provides high resolution, less active components and a hybrid structure compared with existing solutions. A single amplifier biquad (SAB) integrator, a passive integrator, and a first-order integrator are used for the low-pass CT DSM. The proposed design can realize a 2 MHz bandwidth with an OSR equal to 50. The peak SNR and Effective number of bits (ENOB) of the proposed design is 82.3 dB and 12.8 bits respectively.

### List of Abbreviations Used

**IoT** Internet of Things

ADC Analog to digital converter

**DSM** Delta Sigma modulator

CT Continuous-time

**AI** Active inductor

VCO Voltage control oscillator

**PN** Phase noise

**FOM** Figure of merit

SAB Single amplifier biquad

**SNR** Signal-to-noise-ratio

**ENOB** Effective number of bits

CMOS Complementary metal-oxide-semiconductor

**OSR** Oversampling ratio

IC Integrated circuits

**DAC** Digital-to-analog conversion

PVT Process, voltage, temperature

MI Magneto-inductive

PLL Phase-locked loop

**SDR** Software-defined radio

**DSP** Digital signal processing

LNA Low noise amplifier

**DCR** Direct conversion receiver

**IF** Intermediate frequency

**BPF** Bandpass filter

**THD** Total harmonics distortion

IIP3 Third-order interception point

P1dB 1-dB compression point

**DR** Dynamic range

CDR Circuit of data recovery

LDO Low dropout regulator

MEMS Micro-electromechanical system

**LPWAN** Low-power wide-area network

MASH Multi-stage noise shaping

**SFDR** Spurs free dynamic range

**AAF** Anti-aliases filter

**BW** Bandwidth

**IBN** In-band noise

STF Signal transfer function

NTF Noise transfer function

CIFF Cascade-of-integrators with forward

CIFB Cascade-of-integrators with feedback

**DCL** Digital cancellation logic

GBW Gain bandwidth product

**DEM** Dynamic element matching

**RZ** Return-to-zero

NRZ Non-return-to-zero

ITF Ideal transfer function

HRZ Half return-to-zero

**DWA** Data averaging algorithm

**PsDWA** Pseudo DWA

**PDWA** Partitioned DWA

**NS-DWA** Noise Shaping DWA

**ELD** Excess loop delay

**HCD** High-crossing driver

**ISI** Inter-symbol interference

**PSD** Power density spectral

**FFT** Fast-Fourier transfer

**SNDR** Signal-to-noise-distortion ratio

### Acknowledgements

I am here to express my sincere gratitude to my supervisor, Dr. Jean-François Bousquet, who have provided immense guidance, assistance, and constructive support throughout the years of my doctoral studies. He has been giving me high dedications in his role as my supervisor, allowing me to gain valuable experiences and lessons.

My thanks goes to my amazing group members, because of them, I have learnt and gained much more than what I am familiar with in my field. The experience that I feel in our UW-STREAM research group is constructive, leaving me with an impression of a productive environment with strong team work. My thanks goes to all my current group members and alumni: Xiao, Hussein, Afolarin, Surinder, Adib, Cole, Jeff, Adam and Andrew.

I would like to thank all the staff members at the department of Electrical and Computer Engineering, Dalhousie University for their support and cooperation that makes the experience of being a postgraduate student at Dalhousie University much smoother. Special thanks goes to Dr. El-Sankary and Mark LeBlanc for all the technical supports that they have provided.

I acknowledge the supports from the Faculty of Graduate Studies for providing scholarships and the CMC Microsystems for guiding the chip fabrication during this doctoral studies. I would also like to acknowledge the great support from my family members for the supports that allows me to pursue this doctoral studies.

### Chapter 1

#### Introduction

### 1.1 Potential of CMOS Technology for Internet of Underwater Things

Since the invention of the transistor at Bell Labs in the middle of the 20th century, the advancement in very large scale integration (VLSI) technology on semiconductor has revolutionized our society, making it possible to increasingly digitize information and thus generating new capabilities and potential. During the last fifty years, the scaling process that was predicted by Moore at Intel has been closely maintained, and we have observed the doubling of the number of transistors per unit area on an integrated circuit (IC) every two years. Using innovative semiconductor fabrication processes, and particularly with complementary metal-oxide semiconductor (CMOS) the scaling process has been continuing, leading to smaller devices, higher integration, and lower power consumption.

The trend driven by the scaling of CMOS technology has a more significant effect on digital circuits, therefore providing us with continuously faster and better digital computing products. To maintain the scaling trend, better manufacturing have been devised with new processing techniques to fabricate ICs from larger silicon wafers, with smaller die sizes [1]. Many discussions on the fundamental limits and future directions of this CMOS scaling process have been discussed in [2, 3, 4], where new materials and processes are seen to be the only key to maintain the future scaling trend [5, 6]. New CMOS techniques are must take into consideration low voltage supply and very short channel length. The scaling of these two parameters provides benefits for digital logic circuits area, which is the dominating motivation of CMOS scaling as indicated in [7].

For analog designs, the benefits from the channel scaling may not be too apparent. In fact, many problems have resulted with the smaller scaling process, including limited voltage headroom for transistors, lower transconductance gain, lower output power and lower signal-to-noise ratio [8]. Moreover, non-idealities in state-of-the-art

CMOS process lead to lower yield rate that are still difficult to predict and compensate. Nonetheless, implementation of analog circuits on CMOS technology is still essential since our environment is a pure analog world. As such, analog circuits plays a key role in linking the real world with the digitized world. Additionally, integration with digital counterparts on the same IC is preferable for many reasons, including the footprint of the entire circuit, the cost savings using fully-integrated solutions, and the ability to produce accurate and reliable data converters, specifically analog-to-digital converters (ADCs) and digital-to-analog converters (DACs), that require a mixed-signal design process.

The design of analog circuits using short channels make the process, voltage, temperature (PVT) variations more prominent, possibly leading to mismatch issues between transistors. As such, non-idealities of the transistor are exacerbated when devices are made smaller. In fact, according to [9], the variance of the voltage threshold and effectively of the transistor current is inversely proportional to the width and length of transistors. With technology scaling, the proportionality constant is no longer the same, and it decreases with more recent fabrication processes. Additionally, the low voltage supply in new CMOS techniques makes the analog designs more sensitive and unstable. Specifically, the low voltage supply leads to lower gain, smaller headroom for transistors and smaller output voltage swings, which may weaken the performances of analog circuit designs. As such, to design robust analog circuits that achieve high yield, accurate characterization of mismatch parameters for each technology process is still considered important and necessary [10].

To enable ocean monitoring, a motivation for this work is to develop a flexible analog front-end on CMOS technology that can be applied for heterogeneous sensing in underwater networks. While the design of the transmitter generally requires interfacing between different circuits implemented on different semiconductors, fully integrated receivers can be realizable.

#### 1.1.1 Challenges in Low-power Receiver IC designs

Towards the implementation of a fully integrated receiver, a variety of standard techniques and tools are applied to design on-chip analog components; the key components

include low-noise amplifiers, active filters, oscillators, mixers and delta-sigma modulators (DSMs). In particular, active filters and DSMs are approaches that mitigate the on-going scaling of the CMOS process. For example, the DSM can achieve high resolution conversion by trading off analog components accuracy with larger over sampling ratio (OSR) and more digital-intensive circuitry.

The scaling of the transistor introduces challenges on the linearity of the front-end circuit design at the receiver. The poor linearity is due to several factors, including the low output impedance of the current mirrors, the low transistor intrinsic gain, and mismatch between devices [11, 12, 13]. It jeopardizes the dynamic range at the receiver, it degrades the maximum signal input power, increases the spectral regrowth and increases the power consumption. Effectively, this deteriorate the sensitivity level of the whole system and places burden at the digital processor to operate under low signal-to-noise power ratio. Since CMOS technology is applicable to low-power, highly integrated circuits, a motivation of this work is to implement a receiver front-end that can have a large dynamic range.

Significant investments are being made in the deployment of underwater sensor network, which has prompted the definition of integrated sensing and communication technologies to enable the Internet of Underwater Things (IoUT). Specifically, magnetic-induction can serve to power devices, and enable communication across the air-water interface. Furthermore, to enable long-range communication acoustic propagation has been the preferred approach, and commercially available modems currently operate at a center frequency of 27 kHz and above. Finally, the ambient noise in the ocean provides a means to monitor its activity. Specifically, underwater instruments can be equipped with acoustic sensor arrays to monitor the presence of ships, track various species of marine mammals, and can also detect and characterize man made activities and seismic activity. As such, underwater instrumented platforms are equipped with heterogeneous sensors, that combine ultra-sonic arrays, magnetic sensors, and complementary sensors that provide physical environmental characteristics of the ecosystem.

To enable fusion of data in the IoUT, an adaptive integrated sensor is proposed, and the front-end can be tuned for underwater sensing, acoustic communications, as well as magnetic-inductive coupling. Furthermore, with the development of Internet of Things (IoT) sensors, the scaling of CMOS technology further supports the development of multi-purpose multi-band front-ends that are fully-integrated with remote processors and communication nodes. As such, this thesis covers the design of key analog components to implement low-power receivers at the input of a software defined modem. Firstly, a channel selection filter with a wide tuneable range and a constant high quality factor will be described. The constant quality-factor and the fourth-order bandpass frequency response provide an excellent performance in frequency selectivity and out-of-band signal suppression. Secondly, in this thesis, an active-indutor based VCO is designed with a very compact footprint in comparison with LC-VCOs designed in the VHF band. Thirdly, a CT DSM with a similar bandwidth is introduced to convert signals from the channel selection filters to a digital signal. A potential application, using a combination of these key integrated circuit components, is an IoT receiver array, as shown in Fig 1.1, for ultrasonic applications, for example, to enable a receive beamformer system.

#### 1.1.2 Thesis Goals and Research motivations

There is currently a dramatic rise in demand for remote sensors due to the IoT. For most IoT sensor nodes, the bandwidth is not a primary concern in comparison to that of communication equipment. Instead, the power consumption is very important. As such, it is preferable to extend the battery life of remote sensors for several reasons: to reduce the maintenance, to lower the cost, as well as for environmental sustainability.

With the above considerations, it is necessary to design low-power low-frequency sensor nodes below a few MHz, which allows processing different signal spectra, such as ultrasonic waves or low-frequency electromagnetic signals. Sensor fusion has received increased interest in recent years, to integrate heterogeneous sensing nodes in a single system. Additionally, in IoT applications, the sensor nodes are multi-functional and can be deployed for various applications. Specifically, the sensor simply detects the analog signal which is converted into a digital signal, such that it can be processed locally or forwarded to an edge node. As such, the target application may operate over several bands. Furthermore, an analog-to-digital converter must be able to cover a wide bandwidth and provide a high dynamic range.

Figure 1.1: A simplified IoT wireless receiver architecture

In this thesis, a smart multi-band receiver operating ultrasound frequency bands is investigated. With multiple receiving frequencies and high resolution continuous-time Delta-Sigma ADC, the objective is to design a front-end with a low footprint and low power consumption. To extend the lifetime of the remote sensor node, such that it can be deployed for several month, the power consumption must be below 10 mWatts for the analog front-end. The resolution must be greater than 12 bits to provide a good dynamic range for the different sensors. At the core of the receiver, a continuous-time Delta-Sigma ADC described in [14][15] will be utilized to satisfy these requirements. The front-end design should also be easily integrated with a digital processor, such as a Field Programmable Gate Array (FPGA). Using this architecture, a variety of identical front-end channels can be integrated to enable sensors arrays.

To implement the mixed signal circuit design, a flexible front-end is required. First, a controllable bandpass filter is necessary to select the target operation frequency. The tuneable filter is a low-cost solution that avoids the requirement to design a variety of different front-ends with different requirements. To enable a wide-band filter, a low noise amplifier which is typically at the front-end of the sensor receiver is integrated with the bandpass filter to increase the integration level of the

front-end. As such, to improve the overall noise figure of the receiver, the active bandpass filter should provide a gain, between 10 to 20 dB.

For the analog to digital conversion, the continuous-time DSM has a power efficiency advantage in comparison to others ADC architectures. In fact, DSM ADCs can provide a high resolution and large dynamic range which is suitable for IoT sensors. Also, a clock is required for the ADC and other components that need timing control, and a compact, low power voltage controlled oscillator is required for this purpose. Thus, remote sensor nodes must include three key devices: 1) the channel selection filter, 2) the VCO, and 3) the CT DSM. Due to the large size of on-chip capacitors and inductors, a small footprint is a challenge for applications in this frequency band. Moreover, the use of high-gain op-amps required for typical CT-DSMs leads to a high power consumption. All those features are not suitable for remote IoT nodes.

As explained above, three key components are designed for the proposed multichannel receiver system. To make the specifications of those design more easily to understand, a brief explanation is provided here. In this system, a 90 dB dynamic range for the system is required. As such, a VGA/LNA is required before the channel selection filter to compensate the linearity performance of the channel selection filter shown in Fig 1.1. With this arrangement, the gain of the channel selection filter is relaxed and a low power design can be accepted and achieved. The other benefit from a first gain stage with a gain of 40 dB, the dynamic range for this filter only requires around 50 dB. The detail of this design will be given in Chapter 2.3. Also, to drive the ADC, an integrated VCO is necessary. In this design, the target tuneable frequency range of this VCO should be between 100 MHz to 500 MHz to satisfy the requirement of the oversampling ratio for the ADC with a fixed oversampling ratio to save power at low input frequency signal. Also, a low phase noise around -110 dBc/Hz at 1 MHz should be targeted to maintain the sensitivity of the system at a good level, for example, -100 dBm for this system design. As such, in Chapter 3, an inductor-less cross-coupled VCO is designed for this system. Finally, for most low frequency communication system particularly in the acoustic and ultrasonic band, a high digital resolution can be beneficial for remote data processing. To realize a high resolution ADC with low power consumption, the Delta-Sigma ADC is designed and optimized in Chapter 4. As such, an oversampling ratio of 50 with an Effective number of bits (ENOB) of 12 bits is selected. Also, in Chapter 4.7.3, low power techniques and noise transfer function (NTF) optimization approach are provided.

To summarize, for the three key components presented in this thesis, the channel selection filter should achieve multi-channel passbands with a dynamic range of 50 dB; an inductor-less VCO is required with a phase noise around -110 dBc/Hz at 1 MHz offset with a low power consumption; lastly, an ADC is employed with a Delta-Sigma ADC topology and it should have an ENOB of 12 bits under a sampling frequency which is 50 times higher than the Nyquist frequency.

Therefore, as a first objective, in this thesis, I will investigate the practical use of a gm-C based active bandpass filter with quality factor enhancement. As a second objective, a fourth-order continuous-time Delta-Sigma modulator with only two active opamps and a low-pass feedback resistive DAC will be proposed. The primary motivation in the choice of the circuit components at the core of the proposed receiver front-end is to reduce power consumption, constrained on the signal quality, and can be summarized as follows:

- the channel selection filter gm-C topology is derived from a gyrator-C topology and can be cascaded:

- the clock VCO is optimized in power consumption and constrained on phase noise;

- a DSM ADC fourth-order loop filter is optimized for power efficiency, while maintaining the signal transfer function and noise shaping capability.

#### 1.2 Objectives and Contributions

The aim of the work is to integrate a remote transceiver that can be deployed underwater to sense ultra-sonic and magnetic signals, and key components are designed such that they can be integrated on a single platform. Although the designs and implementations of the standalone voltage-control oscillator (VCO) is included within this thesis, a phase-locked loop (PLL) and frequency synthesizer is required to create a stable clock. To allow magneto-inductive communication using software define modem, the circuit is to be integrated with a magnetic coil. However, in this thesis,

the design of the magneto-inductive antenna and its implementation strategy are not discussed. Nonetheless, we will still refer to this design when we introduce the system, since it is being developed concurrently. Although the antenna design has not been integrated within the whole system, the channel selection filter, the VCO and the continuous time delta-sigma modulator are the most crucial parts in the receiver node, and is intended to enable a high throughput communication network underwater.

As such, the specific objectives of this thesis are:

- 1. To realize a higher integration level for the analog front-end and multi-purpose sensors, a novel controllable gm-C based active biquad bandpass filter, referred in this thesis as a channel selection filter, is implemented using TSMC's CMOS 65-nm process and overcomes the low quality factor and narrow tunable range of conventional gm-C bandpass filter.

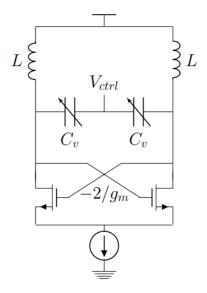

- 2. An inductor-less VCO is designed using an active inductor to minimize the footprint of the LC cross-coupled topology VCO in the VHF band, and also to improve the phase noise performance.

- 3. The use of a hybrid active-assive integrator in a loop filter is investigated, aiming at continuous time delta-sigma modulator application. This type of loop filter is chosen for its power efficiency, and its finite bandwidth gain. A circuit architecture will be investigated to attenuate out-of-band high frequency signals by employing a low-pass feedback path within a continuous-time sigma delta modulator.

In this dissertation, our contribution is the design and implementation in 65-nm CMOS technology of key components for low-frequency signal acquisition, including the channel selection filter, the VCO and the CT-DSM. In our work on the channel selection filter, the passband tuneability, the quality factor optimization and the noise performance will be analyzed and supported by experiment results. Furthermore, the inductor-less VCO based on gyrator-C topology is analyzed with a wide tuneable range and an optimized phase noise performance, and the analysis is supported by the measurement results. Also, the focus and emphasis of this thesis regarding the CT-DSM deals with the high level simulation, analysis and design, chip implementation,

and measurements that are embedded within a fourth-order 4-bit CT-DSM with DWA.

Specifically, the main research contributions of this thesis can be listed as follows

- 1. I designed, developed and tested a new active biquad bandpass filter as a channel selection filter. The basic theory shows that the circuit is equivalent to a second-order RC filter. The topology is based on gm C circuits with a pair of differential PMOS transistors at the output to improve the quality factor limitation that normally appear in those RC type filter. A tunable channel selection filter in CMOS 65-nm was fabricated and tested such that it can be integrated in a magnetic sensor analog front-end.

- 2. I designed, developed and measured a new active inductor topology that was applied in a differential cross-coupled VCO. The topology is based on a gyrator-C circuit with a pair of cross-coupled differential PMOS transistors that present a negative resistance to improve the quality factor of the active-inductor. This circuit was designed and implemented in a wideband tuneable VCO in CMOS 65-nm and the performance was measured in the lab.

- 3. Towards the design of a high order multi-bit CT-DSM, I provided an analysis and design considerations towards the development of a hybrid active-passive integrator architecture to minimize the power consumption for sigma-delta ADCs. Through analysis, the noise shaping improvement of the circuit was demonstrated, and tuning strategies were provided which also highlights their limitations.

- 4. I designed, simulated and measured a fourth-order 4-bit continuous-time sigmadelta modulator with a low-pass feedback path in CMOS 65-nm. The CT-DSM design, in which an optimization approach is adopted, combines the hybrid active-passive integrator, a resistor-based DAC to optimize the power efficiency. The use of a low-pass feedback path is investigated using a switch resistor DAC to understand the performance of noise shaping for multi-bit system. This work is supported with hardware experimental results. The work is submitted for publication in *IEEE Transactions on Very Large Scale Integration (VLSI)*

Systems. Prior to these publications, to our knowledge few reported work has used this architecture for multi-bit CT-DSM applications.

#### 1.3 Outline of this dissertation

The organisation of this dissertation is arranged as follows:

Chapter 2 discusses a channel selection filter for heterogeneous sensing applications. Here, the applicability of the active biquad bandpass filter based on the gm-Ctopology is proposed, for use in a receiver front-end node. This chapter contains material from the following publications:

- Ningcheng Gaoding and Jean-François Bousquet, "A 4th-Order Programmable Channel Selection Filter for Acoustic and Ultrasonic Applications," in 2020 IEEE 63th International Midwest Symposium on Circuits and Systems (MWS-CAS), 2020, pp. 154–157.

- 2. Ningcheng Gaoding and Jean-François Bousquet, "A Fully Integrated Controllable Bandpass Filter with a Constant Q-Factor for Ultrasonic Applications" submitted to IEEE Transactions on Circuits and Systems II: Express Briefs (under review).

The first publication presents a design that establishes the potential of a DAC as a controller for the channel selection filter, and the second paper presents discussions on its potential use in low-voltage environment for ultrasonic and magneto-inductive applications, and supported with experimental results.

Chapter 3 covers the design of a CMOS 65-nm inductor-less VCO for ISM applications in the VHF band. The proposed design employs the differential LC-VCO topology while the inductor is replaced with the proposed novel active inductor topology based on the gyrator-C circuits. This chapter contains material from the following publications:

Ningcheng Gaoding and Jean-François Bousquet, "A Fully Integrated Sub-GHz Inductor-less VCO with a Frequency Doubler," in 25th IEEE International Conference on Electronics, Circuits and Systems (ICECS), 2020, pp. 469-472.  Ningcheng Gaoding and Jean-François Bousquet, "Design of a CMOS 65-nm inductor-less VCO for ISM applications in the VHF band," in International Journal of Circuit Theory and Applications, 2020, Vol. 48, no. 8, pp. 309-320.

The first publication presents a design with a dual-band VCO implementation by employing active inductors, and the second paper presents discussions on its potential use in VHF band applications for an optimized phase noise design, supported with experimental results.

Chapter 4 provides our study on the design of an ADC. The main discussion is on the sigma-delta ADC with a chip implementation in various different technique trends. Also, to support the discussion, the measurement results are compared to the features of similar designs available in the literature.

Chapter 5 proposes a new tuning and optimization technique to achieve a 13-bit ENOB using a hybrid loop filter and low-pass feedback path. The design is also compared with existing CT-DSM circuits. A tuning mechanism is a necessity for the low-pass feedback path that we use, and therefore this chapter provides a practical scheme to explain this issue and verify it with experimental results, in order to enable the operation of the proposed CT-DSM circuit. The work in this chapter has been submitted for publication in *IEEE Transactions on Very Large Scale Integration* (VLSI) Systems, and the hybrid loop filter topology that was used as case study in this chapter has been presented in IEEE NEWCAS 2020. Details of these publications are listed as follows:

- 1. Ningcheng Gaoding and Jean-François Bousquet, "A Hybrid 4th-Order 4-Bit Continuous-Time  $\Delta\Sigma$  Modulator in 65-nm CMOS Technology," in 2020 18th IEEE International New Circuits and Systems Conference (NEWCAS), 2020, pp. 134-137.

- 2. Ningcheng Gaoding and Jean-François Bousquet, "A 4th-Order 4-Bit Continuous-Time ΔΣ ADC Based on Active-passive Integrators with a Resistance DAC," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems (Under Review).

The first publication presents a design that establishes a hybrid structure loop filter to help the CT-DSM achieve a better performance, and the second paper presents discussions on a multi-bit CT-DSM based on active-passive integrator with a built-in low-pass filter in the feedback path. The design is also supported with experimental results.

Chapter 6 summarizes conclusions and key contributions of this dissertation. Possible future research directions from this work are also included.

### Chapter 2

# Design of a Controllable Low-Frequency Channel Selection Filter

In this chapter, first, in Section 2.1, system requirements are presented, with potential solutions to adaptive filter designs; then, in Section 2.2, fundamental concepts for the gm-C topology are reviewed; finally, in Section 2.3, a novel gm-C adaptive filter with tuneable center frequency is designed and measured.

#### 2.1 Channel Selection Filters: Background and Challenges

In a wireless communication receiver, the architecture can follow a heterodyne, or direct conversion topology. Direct conversion receivers have gained significant interest in high-speed wireless communication; since they do not require analog filters to mitigate image frequencies, they dissipate less power [16]. The direct conversion receiver is particularly beneficial to enable fully-integrated receivers on semiconductor, and typically its architecture consists of a band-pass filter, a low noise amplifier (LNA), a mixer, a channel selection filter and an ADC. While the filters are common circuits, they have presented their challenges in integrated circuit design, because of the area required for the passive devices.

Filters are used for various purposes, and their application can vary depending on the choice of receiver architecture. Fundamentally, it is an analog device that performs signal processing functions specifically to remove unwanted frequency components from signals and effectively enhance the signal quality. Each wireless application has a different frequency band and channel assignment. Retrieving this information is an important concern at the receiver. In general, the channel selection filter is a bandpass filter that isolates a unique channel in a communication standard. As wireless communications are subject to noise and interference, a key function of the channel selection filter at the input of the wireless receiver is to select the desired fundamental signal and to remove out-of-band unwanted signals.

With the recent emerging trends in wireless communication systems, and the proliferation of remote sensor nodes, there is a pressing need for a low power approach for compact VLSI circuits that integrate the complete remote node processor. The need for low in-band noise and suppression of out-band signal is always an issue for a wireless design. Tuning to those frequencies is always a tedious task. This can be achieved using a channel selection filter which blocks the out-band signal completely and is an integral part of the direct conversion receiver. As wireless communication deals with various noise sources and interference that can limit the dynamic range of the receiver, it is crucial to minimize the noise at the input of the receiver front-end. The simplest method is to have a channel selection filter whose cut-off frequency is fixed to the value of the wireless standard with the widest channel bandwidth among the supported standards. Using this filter, even for other wireless standards, information is not lost in the channel selection filter. However, the requirements of data converters performance have become very stringent [17]. Therefore, the cutoff frequency of the channel selection filter should be adjusted according to the channel bandwidth of each wireless standard.

Tuneable on-chip active filters have been investigated to enable adaptive bandpass filters. Various circuit topologies have been proposed such as op-amp based filters, gm-C filters and MOSFET-C based filters. Op-amp based filters, commonly referred as active-RC filters, utilize a combination of active components and passive components. Configuring active-RC filters in biquad, and cascading multiple stages can serve to generate higher order filter transfer function. However, significant power consumption and bulkiness renders the active-RC filter unsuitable for low-power wireless communication [18]. The gm-C utilizes a voltage to current converter followed by a highly linear current multiplier. This increases the linearity of the circuit at moderate frequencies, but fails at higher frequencies which prevents it from being applied for high frequency applications. The unity-gain bandwidth of amplifier can be set near the filter cut off frequency; this in turn reduces the power consumption. For the MOSFET-C filter, since an op-amp is required, it also has the same power consumption limitation as the active RC filter. As this thesis focuses on acoustic and ultrasonic applications with frequencies up to a few Megahertz, a circuit topology relying on the gm-C circuit at its core will be proposed.

Figure 2.1: A beamformer for an ultrasonic sensor array

It can be noted that the use of the analog front-end design for wireless communications can also be applied to a variety of other societal problems. In fact, in acoustic or ultrasound front-ends, as in many other sophisticated electronic systems, the analog signal processing components are key in determining the overall system performance. This is a general problem in any receive signal processing front-end. As an example, it is interesting to note that an acoustic or ultrasound beamformer system is very similar to a radar or sonar system - while radar works in the GHz range, sonar in the kHz range, and ultrasound in the MHz range - but the essential system principles are essentially the same. Actually, an advanced ultrasonic communication receiver is practically identical to a Synthetic Array Radar (SAR). An example is shown in Fig. 2.1. Originally the 'phased array' idea of steerable beams has been conceived by radar designers. However, ultrasound designers expanded on the principle and today those systems are some of the most sophisticated signal processing equipment.

#### 2.2 Channel Selection Filters: Current State of the Art

Recently, acoustic and ultrasonic frequency bands have been employed in near field sensing applications, for example, for hearing assistants, medical imaging and even applications relying on magnetic induction [19][20]. To select different channels for sensors applied to multi-bands applications at low-frequency, a channel selection filter is a highly desirable circuit component. In conventional transceivers, different fundamental signals can be separated from other signals through a parallel band-pass

filter selection network [21] that can be enabled using switches. However, to enable a compact and low power filter, a single channel selection filter with a controllable center frequency, a low-power consumption, good out-of-band rejection capability and a compact size is desired. Also, instead of employing a passive controllable BPF, an active one is more attractive because it has a large slew rate and provides gain for the receiver front-end in comparison with passive ones.

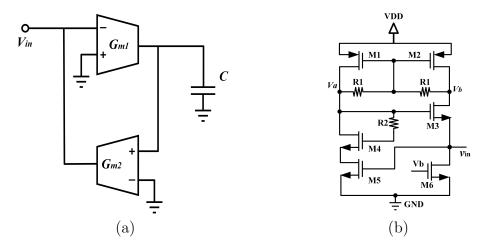

Figure 2.2: Sensor architecture utilizing a gm-C BPF.

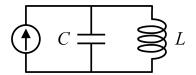

In general, an on-chip BPF can be realized by employing different design techniques, using 1) passive elements, 2) an active-RC design, 3) a switch-capacitor design and 4) the gm-C topology [22, 23, 24, 25, 26]. However, it is not advisable to employ passive LC elements to create on-chip BPF in the acoustic and ultrasonic frequency bands, because the large inductor value leads to a high cost due to the large on-chip area. Also, filters based on active-RC and switch-capacitor techniques normally require an op-amp with a large gain. This leads to a high power consumption or a complex design. Instead, in this work, the gm-C filter topology can implement an active inductor.

As shown in Fig. 2.2, the gm-C filter consists of a common-source transistor with transconductance  $g_{m1}$  loaded with a capacitor  $C_1$ , and a second transistor with transconductance  $G_{m2}$  connected in feedback. The equivalent input inductance of the gyrator-C is

$$L_{eq} = C_1/G_{m1}G_{qm2}. (2.1)$$

The inductance  $L_{eq}$  in series with the capacitor  $C_{in}$  forms a resonant circuit at the core of the second order BPF [25]. The merit of using this BPF configuration is that it operates in continuous-time mode and it does not require a high gain op-amp to provide a filter with a high quality factor in comparison to the switch-capacitor filter. However, its disadvantage is that it offers a small linear dynamic range and it may be very sensitive to parasitic capacitance because of the low gain. Moreover, a single transistor is employed to realize the transconductance  $g_m$  instead of a complex op-amp network; this significantly reduces the power consumption. Another benefit of the gm-C topology is that it can provide some gain in comparison to passive LC BPF; this provides an improvement to the front-end sensitivity.

In this thesis, a tuneable second-order active biquad bandpass filter based on the gm-C topology is designed in TSMC's 65-nm technology. The proposed filter shown in Fig. 2.3 spans a wide frequency range in the ultra-sonic frequency band. To select a channel with a given center frequency and bandwidth, the proposed filter is also designed to be controllable and can be cascaded. By adjusting a control voltage, the proposed design can select different passband channels with an almost constant quality (Q) factor. It can be used, for example, as an input signal acquisition filter at the front-end of a downconverter mixer in a wireless receiver or at the input of continuous-time analog-to-digital converters (ADCs) in a sensor. Moreover, the proposed BPF is designed to be cascaded such that a higher Q-factor and better out-of-band rejection can be achieved easily. This increases the channel selectivity capability of the receiver. The proposed design is simulated and also verified with measurements. To compare the proposed design with existing state-of-the-art, a figure of merit (FOM) introduced in [20] is employed to quantify the performance.

# 2.3 A Low-power 4<sup>th</sup>-order Controllable Channel Selection Filter

In this section, first, in Section 2.3.1, a proposed filter design relying on a gm-C core topology with an improve quality factor is analyzed; then in Section 2.3.2, measurement results are presented. As will be demonstrated, the filter shows an improved in maintain a constant Q-factor with low power consumption.

#### 2.3.1 Proposed Filter Topology Analysis

In this section, a methodology combining a PMOS source follower and a gm-C based highpass filter is introduced and analyzed. The benefits are an enhanced and an approximately constant quality factor for the whole tuneable frequency range. Also, the design requires a low power consumption and can be cascaded to realize higher order filters.

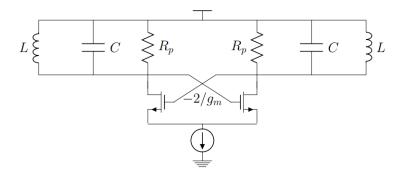

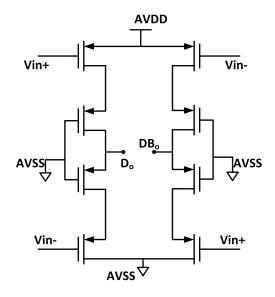

A novel tuneable active BPF based on the qm-C topology is shown in Fig. 2.3. It should be noted that a conventional second-order RC BPF has a low Q-factor limitation, which also applies to a BPF design based on a conventional gm-C topology [27]. As such, a cross-coupled PMOS pair, formed using M1<sub>a-b</sub> is chosen to improve the Q-factor of the proposed design. Also, the proposed filter employs a differential topology to compress the even order harmonics and thereby maximize the dynamic range of the filter and its linearity. In Fig. 2.3, M2<sub>a-b</sub> and M3<sub>a-b</sub> represent a conventional gyrator-C topology formed by a PMOS and an NMOS single transistor respectively. Additionally, the transistor pair  $MN_{a-b}$  acts as a current source for the gyrator-C topology. As proposed in [24], the input capacitor C<sub>in</sub> and the load capacitor C1 are added to the gyrator-C topology formed by  $M2_{a-b}$  and  $M3_{a-b}$ . This produces a bandpass frequency response between the input  $V_{in}$  and output  $V_L$  of the gm-Cstage as shown in Fig. 2.3 [22]. Moreover, a PMOS source follower, which consists of the cross-coupled pair  $M1_{a-b}$ , the capacitor  $C_L$  and the current source  $MP_{a-b}$ , is a natural first-order lowpass filter. As such, a bandpass frequency response is produced between the voltage node  $V_{in}$  and the output of the PMOS source follower.

An approximation of the transfer function between the input  $V_{in}$  and the output  $V_{out}$  can be determined using the small-signal model of the circuit. From the voltage node  $V_H$  to the voltage node  $V_{out}$ , the lowpass transfer function generated by the PMOS source follower is

$$H_{LP}(s) = \frac{V_{out}^{+}}{V_H} = \frac{1}{1 + \left(\frac{sC_L}{g_{m1}}\right)}.$$

(2.2)

Note that all the transfer functions are based on an equivalent single-ended topology of the proposed design. It should also be noted that the differential cross-coupled structure can present an equivalent negative resistance at node  $V_H$  to help optimize

Figure 2.3: A proposed BPF with a constant quality factor.

the overall frequency response. The gm - C topology produces a lowpass transfer function between the voltage node  $V_H$  to the voltage node  $V_L$ . It can be expressed as  $H'_{LP}(s) = V_L/V_H = (g_{m2} + g_{o2})/(sC_1 + g_{o2})$ . Moreover, due to the large input impedance presented by the source follower, the highpass transfer function generated by the gm - C topology from the voltage node  $V_{in}$  to the voltage node  $V_H$  can be expressed as

$$H_{HP}(s) = \frac{V_H}{V_{in}^+} \approx \frac{s(s + \frac{g_{o2}}{C_1})}{s^2 + s\left(\frac{g_{o2}}{C_{in}} + \frac{g_{o3}}{C_1 + C_{in}}\right) + \left(\frac{g_{m2}g_{m3}}{C_{in}C_1}\right)},\tag{2.3}$$

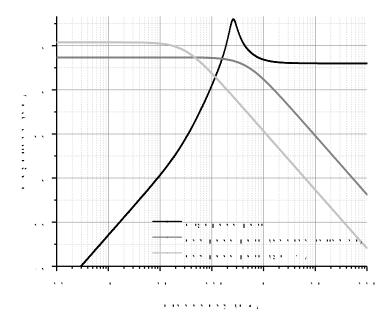

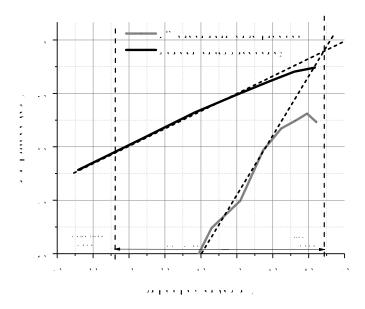

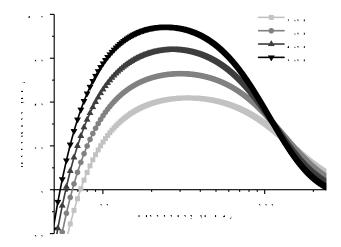

where  $g_{o2}$  and  $g_{o3}$ , and  $g_{m2}$  and  $g_{m3}$  are the output conductance and transconductance realized by  $M2_{a-b}$  and  $M3_{a-b}$  respectively. Specifically, Fig. 2.4 shows the curves of three signal responses,  $H_{LP}(s)$ ,  $H'_{LP}(s)$  and  $H_{HP}(s)$ . It can be observed that the highpass frequency response, which is formed by  $M2_{a-b}$ ,  $C_{in}$ ,  $C_1$  and  $M3_{a-b}$ , helps define the Q factor of the overall circuit. Note that, the drain-to-source conductance of  $M2_{a-b}$ ,  $g_{o2}$ , introduces a zero at low frequency with  $C_1$ , which changes the slope of the highpass filter as shown in Fig. 2.4. Also, the source follower frequency response is designed to have a cutoff frequency near the resonating frequency of the highpass filter.

In this design, the proposed bandpass frequency response is shaped using the

Figure 2.4: Magnitude response for the three signal paths.

Figure 2.5: Magnitude response at different frequencies.

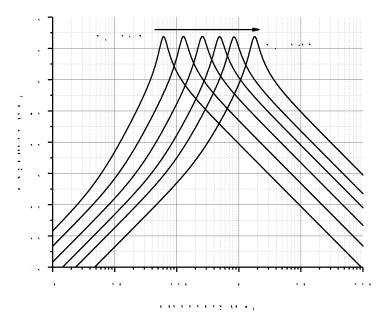

highpass path generated by the qm-C topology combined with the lowpass path provided by the PMOS source follower, instead of using the bandpass frequency response shaped by the conventional qm-C topology. Ideally, a 3rd order filter is produced, but the finite zero at  $\omega_z = g_{02}/C_1$  changes the slope of the filter at low frequency, and the overall response of the filter is similar to that of a second order BPF. The crosscoupled negative conductance formed by transistors  $M1_{a-b}$  helps reduce the output conductance  $g_{o3}$  from M3<sub>a-b</sub>. Also,  $g_{m2}$  can be used to tune the Q-factor. Effectively, this helps produce a high-pass frequency response with a higher Q-factor at the input of the gm-C topology. Also, at the output of the BPF, the equivalent output conductance is reduced because of the cross-coupled differential connection used instead of the cascode transistor in a conventional gm-C topology [24]. Compared to that of a conventional gm-C BPF with a output at  $V_L$ , in this design, the Q-factor is improved from 3.7 to 5.1 under the same biasing conditions. The simulated frequency responses are at different passband frequencies shown in Fig. 2.5. Since the proposed filter is based on combining the gm-C topology with a PMOS source follower, using the transfer functions derived in (2.2) and (2.3), the passband frequency  $\omega_o$  can be approximated as a geometric mean and can be expressed as

$$\omega_o \approx \sqrt{\sqrt{\frac{g_{m2}g_{m3}}{C_{in}C_1}} \cdot \frac{g_{m1}}{C_L}}.$$

(2.4)

As the lowpass path is a source follower, its gain is approximately one at low-frequency. As such, the total passband gain  $H_o$  can be expressed as the gain of the high pass path, which is the gain of the highpass filter

$$H_o \approx \frac{g_{m3}C_{in}}{\sqrt{g_{m2}C_1 \cdot (4g_{m3}C_{in} - g_{m2}C_1)}}$$

(2.5)

Also, the Q-factor is

$$Q \approx \sqrt{\frac{g_{m3}C_{in}}{g_{o2}C_1}}. (2.6)$$

where  $g_{m1}$ ,  $g_{m2}$  and  $g_{m3}$  are the transconductance of  $M1_{a-b}$ ,  $M2_{a-b}$ , and  $M3_{a-b}$  respectively.

Next, a tuning procedure is proposed; automated tuning can be considered by integrating the filter with a digital signal processor core to control this. As shown in

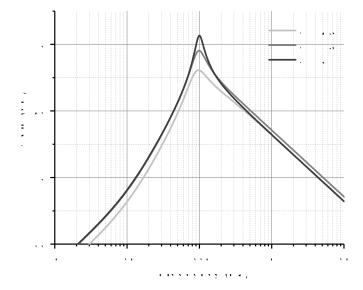

Figure 2.6: Tuning of the Q factors for the proposed BPF at 100 kHz.

Fig. 2.3, the voltage at node  $V_a$  controls the current flowing into the transistors  $M1_{a-b}$  and  $M3_{a-b}$ . Also, the cutoff frequency of the highpass band is primarily defined by the transistor pairs  $M2_{a-b}$  and  $M3_{a-b}$  while the lowpass band is defined by the PMOS source follower as explained previously. To be noted here, when  $V_a$  is changing, the bias voltage at  $V_b$  and  $V_c$  are always fixed so that the change of the bias current in  $M2_{a-b}$  is relatively minimal. Therefore, the current in  $M3_{a-b}$  mainly follows the current change in  $M1_{a-b}$  because of the relatively constant current flowing through  $M2_{a-b}$ . Hence, a tuneable center frequency is achieved by changing the voltage at node  $V_a$ . In addition, the current flow through the  $M2_{a-b}$  is used to control the Q-factor in the filter. By tuning the voltage  $V_b$ , the drain current flowing from  $M2_{a-b}$  can be changed, and thus the Q-factor is also changed. Therefore, with a constant  $V_b$  and  $V_c$ , a relatively constant quality factor can be achieved when  $V_a$  is tuned. The Q-factor tuning in simulation is shown in Fig. 2.6.

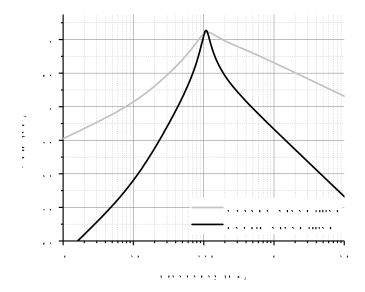

Similar to designs in [26, 28, 24], the proposed single stage BPF can also be used to produce a higher-order BPF by simply cascading two identical second order circuits. Furthermore, the DC operating points of each second order filter can be optimized independently; thus the design of a higher-order filter is greatly simplified. The comparison of the single second order and the cascaded fourth order frequency response is shown in Fig. 2.7. It can be observed that the Q-factor and the out-of-band attenuation are improved by increasing the order of the BPFs. It should be

Figure 2.7: Magnitude responses of the proposed BPFs at 100 kHz.

noted that the input coupling capacitor C2 of the second stage in the fourth order BPF, shown in Fig. 2.3, must be carefully chosen to optimize the frequency response.

The linearity is one of the important considerations in active filter design. In our system, following after a gain stage, the role of this BPF is to select the desired pass-band frequency to realize a multi-channel system. As such, the linearity requirement of this work mainly focuses on the dynamic range. In the post-layout simulations, the noise floor, which is related to the input-refered noise, is -73 dBm and the third-order interception point (IIP3) is -16 dBm. Thus, a dynamic range of 57 dB is achieved. Although this can be improved through higher power supply, this will increase the power consumption of the filter.

It is also important to assess the noise degradation by this filter. The noise currents from MP<sub>a-b</sub> and M1<sub>a-b</sub> are combined and flow through the source follower network comprised of  $C_L$  and  $g_{m1}^{-1}$ . Also, the output of this design is chosen to be the output of the PMOS source follower instead of the output,  $V_L$ , of the conventional gm-C topology. As such, an average differential output noise power can be derived as  $\overline{V_{on}^2} \approx \frac{32kT}{3C_L}$ , where k is Boltzmann's constant and T is the absolute temperature. It can be observed that increasing  $C_L$  is the most effective way of reducing the output noise at the cost of a larger drain current, effectively increasing the power consumption.

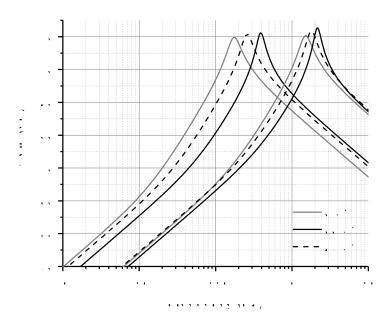

The temperature variation for different frequency bands centered at 257 kHz and 1.78 MHz for the proposed BPF is also provided as shown in Fig. 2.9. As given in (2.6),

Figure 2.8: Analysis of the 1-dB compression point and of the IIP3 for the proposed filter.

Figure 2.9: The post-layout simulation against the temperature.

the Q-factor is mainly decided by the ratios of capacitors and transconductances. The less frequency variation at high passband frequency is due to the larger current in the circuit. As such, the Q-factor of the proposed BPF shows a good robust capability against the temperature and the similar results are also found in the process variation simulation. However, the passband frequencies vary more than that in the temperature variation simulation. This is mainly because the low power supply design is more sensitive to this in comparison with those high power consumption. This can be mitigated at a cost of more power consumption. Alternatively, other techniques can be introduced which makes the circuit independent against PVT variations. Hence, there is a compromise between robustness and low power consumption. Although the passband frequencies vary from the fundamental frequencies, the proposed design still can cover the frequency range between 100 kHz to 2 MHz by tuning the  $V_a$ . The simulated two-stage cascaded filter is shown in Fig. 2.10

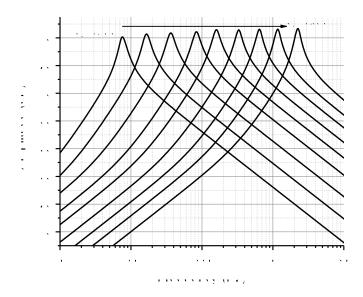

Figure 2.10: Simulated frequency response of the two-stage cascaded BPF for different control voltages between 0.35 V and 0.75 V.

#### 2.3.2 Measurement Results and Performance Comparison

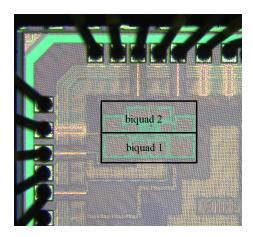

The proposed active fourth-order channel selection filter is designed in TSMC's 65-nm CMOS technology and its frequency response is measured for different control settings. A micro-photograph of the proposed filter fabricated on semiconductor is shown in Fig. 2.11. The total footprint area without pads is  $0.33 \times 0.21 \text{ mm}^2$ .

Table 2.1: Performance summary of the proposed filter

| Metrics             | $650~\mathrm{kHz}$ | 1.2 MHz | 2.4 MHz |  |  |

|---------------------|--------------------|---------|---------|--|--|

| Q-factor            | 7.2                |         |         |  |  |

| IIP3(dBm)           | -21                |         |         |  |  |

| Dynamic Range       |                    | 51.6 dB |         |  |  |

| Power( $\mu$ watts) | 25.6               | 42.3    | 68      |  |  |

Figure 2.11: Layout of proposed filter.

Figure 2.12: Measured IIP3 point of the proposed filter.

Figure 2.13: Measured frequency responses of the 4<sup>th</sup>-order BPF.

The measured passband frequency response is shown in Fig. 2.10, for different tuning bias voltages  $V_a$  varying between 0.42 V to 0.68 V. As can be observed, the total bandwidth covers a wide range between 60 kHz to 2.5 MHz. Also the Q-factor is equal to 7.2 and is almost constant for each of the frequency bands. The passband gain can be improved by adding a buffer after the second stage proposed BPF. The highest power consumption is for the 2.5-MHz band, and is equal to 68  $\mu$ W. The summary of the performance is provided in Table 2.1. The FOM is introduced in [20] and is defined as

$$FOM = \frac{V_{DD} \times P_{DC}}{DR \times f_c \times N},$$

(2.7)

where  $P_{DC}$  is the DC power dissipation in microwatts, the  $V_{DD}$  is the supply voltage, DR is the dynamic range of active filters, the N stands for the order of filters and  $f_c$  is the cutoff frequency.

The linearity performance of this design against the input power is investigated. The measured dynamic range is 51.6 dB with an IIP3 at -21 dBm, as shown in Fig. 2.12, and with a dynamic range at 51.6 dB. The measured passband frequency response is shown in Fig. 2.10, for different tuning bias voltages  $V_a$  varying between 0.42 V to 0.68 V. As can be observed, the total bandwidth covers a wide range between 60 kHz to 2.5 MHz. Also the Q-factor is equal to 7.2 and is almost constant for each

Table 2.2: Comparison with previous BPF designs

| Ref.                    | [20]              | [25]                    | [29]               | [30]      | [31]   | This work       |

|-------------------------|-------------------|-------------------------|--------------------|-----------|--------|-----------------|

| Process (nm)            | 350               | 350                     | 130                | 130       | 180    | 65              |

| Technique               | Gm - C            | $OTA - C^4$             | Switched-capacitor | Active-RC | Gm - C | Gm - C          |

| Q-factor                | 1.86              | 3                       | $0.9 \sim 6.9$     | 1.8       | 1      | 7.2             |

| Order                   | 6                 | 2                       | 2                  | 4         | 3      | 4               |

| Tuneable range (Hz)     | $100 \sim 25.6 k$ | $20 \sim 20 \mathrm{k}$ | $3.9k \sim 7.1k$   | 1.65M     | 2M     | $60k \sim 2.5M$ |

| Supply (V)              | 1                 | 3.3                     | 0.9                | 0.7       | 1.6    | 1               |

| DC Power (µWatt)        | 0.068 @ 670 Hz    | 2.85 @ 2 kHz            | 256.4              | 350       | 1328   | 25.6 @ 650kHz   |

| DR (dB)                 | 49                | 63.5                    | -                  | 40        | 63     | 51.6            |

| FOM $(\times 10^{-13})$ | 3.4               | 13                      | -                  | 4.9       | -      | 2               |

| Area (mm <sup>2</sup> ) | 0.234             | 0.13                    | 0.09               | 0.24      | 0.16   | 0.07            |

of the frequency bands. The passband gain can be improved by adding a buffer after the second stage proposed BPF. The highest power consumption is for the 2.5-MHz band, and is equal to 68  $\mu$ W. Moreover, the comparison is shown in Table 2.2. In comparison with previous work, the proposed filter shows a good dynamic range, an efficient power consumption performance and a wide tuneable range.

As a summary, a controllable constant Q-factor BPF in 65-nm CMOS technology has been presented and a cascaded two-stage BPF composed of two such biquads has been fabricated and measured. The proposed cascaded BPF has a Q-factor around 7.2 for each passband from 60 kHz to 2.5 MHz. Furthermore, the proposed BPF achieves a dynamic range over 50 dB with only 68  $\mu$ W power consumption at 1 V supply. These characteristics illustrate that the proposed design has a capability to be employed as a channel selection filter at the front-end to sense ultra-sonic signals.

# Chapter 3

# Design of an Inductor-less Voltage Controlled Oscillator

A voltage-controlled oscillator (VCO) is a circuit in which the output is a single-ended or differential periodic oscillating output voltage of which frequency depends on the input control voltage. The VCO is a critical circuit block used in phase-locked loops (PLLs). Common applications of PLLs are in frequency synthesis and clock and data recovery circuits (CDR) where they are used as a local VCO. The two main categories of VCOs include the ring oscillator and the LC oscillator (LC-VCO). The LC-VCO is generally capable of higher maximum oscillation frequencies as well as better phase noise performance compared to ring oscillators. Ring oscillators are advantageous in tuning range and manufacture.

In this chapter, a small form factor low-power VCO will be designed to produce a clock that will drive the sensor analog and digital circuit. First, in Section 3.1, the VCO requirements for our application will be reviewed. Then, in Section 3.2, the characteristics of the ring and LC-VCO will be reviewed to justify the choice of topology adopted here. Finally, in Section 3.3, a VCO design relying on active inductors is detailed, its performance is measured, and compared to that of current state-of-the-art.

## 3.1 System Characteristics for the Proposed VCO

There are several important performance characteristics of VCOs that must be considered to guide our choice of architecture. In this section, first, the operating frequency will be reviewed in Section 3.1.1; then, VCO phase noise will be reviewed in Section 3.1.2; finally, the VCO power consumption will be reviewed in Section 3.1.3.

#### 3.1.1 Tuneability of Operation Frequency

A tuning range is necessary for chips or systems that need to operate over a range of frequencies. Tuning range is also important since the frequency of a VCO can vary

due to process variations. If the frequency of the fabricated VCO is slightly different than the intended frequency, as long as the tuning range encompasses the desired frequency of operation, the VCO is still useful.