## GPU-BASED ACCELERATION ON ACENET FOR FDTD METHOD OF ELECTROMAGNETIC FIELD ANALYSIS

by

Dachuan Sun

Submitted in partial fulfilment of the requirements for the degree of Master of Applied Science

at

Dalhousie University Halifax, Nova Scotia November 2013

© Copyright by Dachuan Sun, 2013

| Dedication                                                                                          |  |  |  |  |

|-----------------------------------------------------------------------------------------------------|--|--|--|--|

| This work is dedicated to my parents who gave me support and encouragement at each step of my life. |  |  |  |  |

|                                                                                                     |  |  |  |  |

|                                                                                                     |  |  |  |  |

|                                                                                                     |  |  |  |  |

|                                                                                                     |  |  |  |  |

|                                                                                                     |  |  |  |  |

### **TABLE OF CONTENTS**

| LIST O | F TABLE                                         | S                                                    | V   |  |

|--------|-------------------------------------------------|------------------------------------------------------|-----|--|

| LIST O | F FIGUR                                         | ES                                                   | vi  |  |

| ABSTR  | ACT                                             |                                                      | ix  |  |

| LIST O | F ABBRE                                         | EVIATIONS USED                                       | X   |  |

| ACKNO  | OWLEDG                                          | SEMENTS                                              | xii |  |

| CHAPT  | ER 1 INT                                        | TRODUCTION                                           | 1   |  |

| 1.1    | RESEA                                           | RCH BACKGROUND                                       | 1   |  |

| 1.2    | Motiv                                           | ATION                                                | 2   |  |

| 1.3    | THESIS                                          | OUTLINE                                              | 3   |  |

|        |                                                 | ERVIEW OF THE FINITE DIFFERENCE TIME DOMAIN D        |     |  |

| 2.1    | COMPUTATIONAL EM METHODS AND THEIR APPLICATIONS |                                                      | 4   |  |

|        | 2.1.1                                           | Finite Element Method                                | 4   |  |

|        | 2.1.2                                           | Moment Method                                        | 6   |  |

|        | 2.1.3                                           | Finite-Difference Time-Domain Method                 | 7   |  |

| 2.2    | YEE'S                                           | FDTD Grids and Discretization of Maxwell's Equations | 9   |  |

| 2.3    | FDTD                                            | Enabling Hardware Platform                           | 13  |  |

|        | 2.3.1                                           | CPU-Based FDTD                                       | 13  |  |

|        | 2.3.2                                           | FPGA-Based FDTD                                      | 14  |  |

|        | 2.3.3                                           | GPU-Based FDTD                                       | 16  |  |

| CHAPT  | ER 3 PAI                                        | RALLEL COMPUTING AND GPU ARCHITECTURE                | 19  |  |

| 3.1    | PARAL                                           | PARALLEL COMPUTING TECHNOLOGY                        |     |  |

|        | 3.1.1                                           | Hardware                                             | 19  |  |

|        | 3.1.2                                           | Programming Model                                    | 21  |  |

|        | 3.1.3                                           | Algorithms                                           | 26  |  |

| 3.2    | COMPUTATION: FROM CPU TO GPU                    |                                                      | 27  |  |

|        | 3.2.1                                           | GPU Computation Capability                           | 27  |  |

|        | 3.2.2                                           | Accurate Floating-Point Representation               | 27  |  |

| 3.3    | GPU M                                           | GPU MEMORY STRUCTURE                                 |     |  |

| 3.4    | SUMMA                                           | ARY                                                  | 30  |  |

| CHAPTI | ER 4 IM                               | PLEMENTATIONS OF CUDA-ENABLED FDTD              | 31 |

|--------|---------------------------------------|-------------------------------------------------|----|

| 4.1    | Сомри                                 | UTE UNIFIED DEVICE ARCHITECTURE                 | 31 |

|        | 4.1.1                                 | Hardware                                        | 31 |

|        | 4.1.2                                 | Programming Model                               | 33 |

|        | 4.1.3                                 | Software Architecture                           | 39 |

| 4.2    | FDTD                                  | PARALLEL COMPUTING METHOD BASED ON CUDA         | 43 |

| 4.3    | 4.3 Two-Dimensional CUDA-Enabled FDTD |                                                 | 45 |

|        | 4.3.1                                 | Threads Arrangement                             | 45 |

|        | 4.3.2                                 | Implementation Algorithms and Approaches        | 47 |

| 4.4    | THREE                                 | E-DIMENSIONAL CUDA-ENABLED FDTD                 | 52 |

|        | 4.4.1                                 | Threads Arrangement                             | 52 |

|        | 4.4.2                                 | Implemented Algorithms and Approaches           | 53 |

| CHAPTI | ER 5 CO                               | MPUTATION ACCELERATION                          | 55 |

| 5.1    | PERFORMANCE OPTIMIZATION STRATEGIES   |                                                 | 55 |

| 5.2    | Мемо                                  | RY ACCESSES                                     | 62 |

|        | 5.2.1                                 | Global Memory                                   | 62 |

|        | 5.2.2                                 | Local Memory                                    | 63 |

|        | 5.2.3                                 | Shared Memory                                   | 64 |

| 5.3    | ACEN                                  | ET                                              | 65 |

| 5.4    | LOCAL                                 | PLATFORM SPEED-UP PERFORMANCE                   | 68 |

| 5.5    | MATI                                  | AB GPU Performance and ACEnet Comparison        | 78 |

|        | 5.5.1                                 | Implementation on ACEnet and Initial Run        | 78 |

|        | 5.5.2                                 | MATLAB GPU Performance                          | 81 |

| CHAPTI | ER 6 CO                               | NCLUSIONS                                       | 87 |

| 6.1    | Conci                                 | LUSIONS                                         | 87 |

| 6.2    | Futur                                 | E WORK                                          | 88 |

| BIBLIO | GRAPH                                 | Y                                               | 89 |

| APPENI | DIX A S                               | Specifications of GeForce GT 520 Graphics Card  | 95 |

| APPENI | DIX B S                               | specifications of GeForce GTX 650 Graphics Card | 96 |

#### **LIST OF TABLES**

| Table 4.1.1.1: GeForce GT 520 and GTX 650 graphics cards brief information                                      | 33 |

|-----------------------------------------------------------------------------------------------------------------|----|

| Table 4.3.2.1: Specifications of the PC testing platform                                                        | 47 |

| Table 5.4.1.1: Specifications summary of the testing GPU: GeForce GT 520                                        | 69 |

| Table 5.4.1.2: Detailed information of CPU in the testing computer                                              | 69 |

| Table 5.4.1.3: Comparison between the results obtained from our method and the theoretical resonant frequencies | 69 |

| Table 5.4.1.4: Specifications summary of the testing GPU: GeForce GTX 650                                       | 77 |

| Table 5.5.2.1: Efficiency comparison between local CPU and ACEnet                                               | 82 |

| Table 5.5.2.2: Performance comparison between CPU and GPU with the new algorithm                                | 84 |

#### **LIST OF FIGURES**

| Figure 2.1.3.1: Position of the electric and magnetic fields in Yee's scheme           | 8  |

|----------------------------------------------------------------------------------------|----|

| Figure 2.2.1: Yee's cell in FDTD                                                       | 10 |

| Figure 2.3.2.1: FDTD computing design using FPGA                                       | 16 |

| Figure 2.3.3.1: Traditional GPGPU parallel FDTD computing procedure                    | 18 |

| Figure 3.1.1.1: Parallel computing system: distributed memory architecture             | 20 |

| Figure 3.1.1.2: Parallel computing system: shared memory architecture                  | 21 |

| Figure 3.1.1.3: Parallel computing system: distributed shared memory architecture      | 21 |

| Figure 3.1.2.1: Partitioned multi-threaded program                                     | 23 |

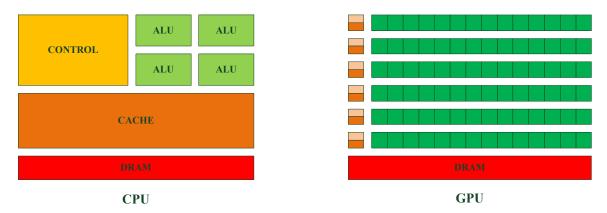

| Figure 3.1.2.2: CPU and GPU microprocessor architectures                               | 24 |

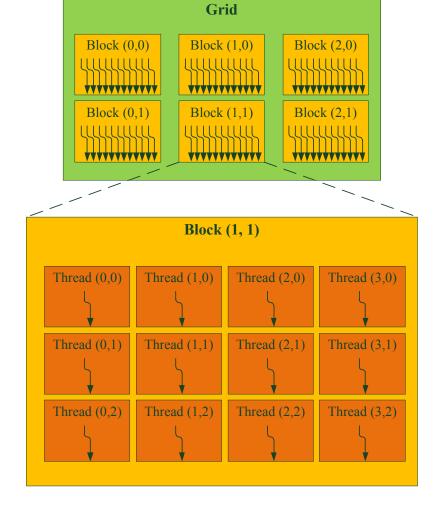

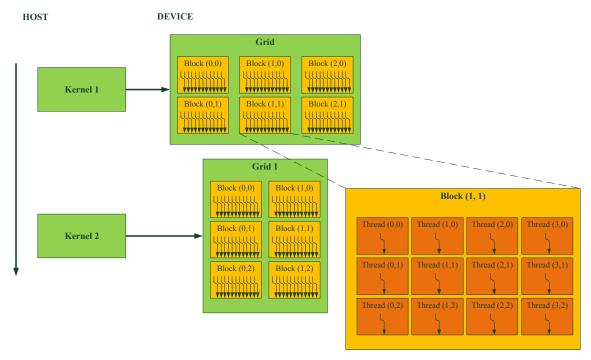

| Figure 3.1.2.3: Hierarchy of threads, blocks and grid in CUDA                          | 25 |

| Figure 3.3.1: Hierarchy of various types of memory in CUDA                             | 29 |

| Figure 4.1.2.1: CUDA programming hierarchy                                             | 36 |

| Figure 4.1.2.2: CUDA grid of thread blocks                                             | 38 |

| Figure 4.1.3.1: CUDA software stack                                                    | 40 |

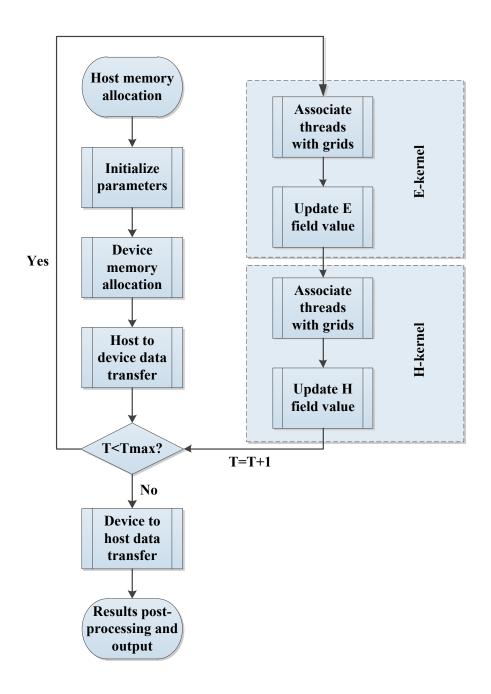

| Figure 4.2.1: CUDA parallel algorithm flowchart of FDTD                                | 44 |

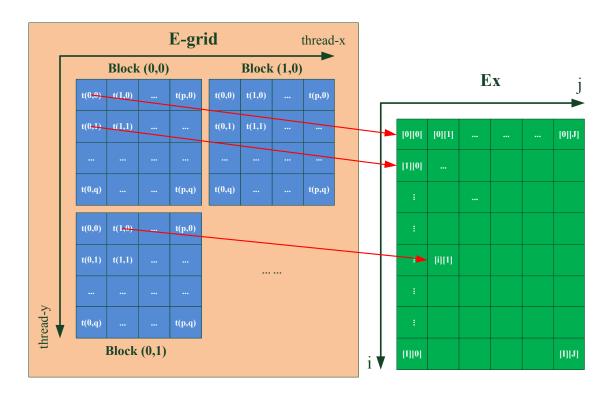

| Figure 4.3.1.1: 2D FDTD parallel algorithm thread arrangement                          | 46 |

| Figure 4.3.2.1: GPU initial run result: simulation size of 64×64 with 100 time steps   | 51 |

| Figure 4.3.2.2: GPU initial run result: simulation size of 128×128 with 100 time steps | 51 |

| Figure 4.3.2.3: GPU initial run result: simulation size of 256×256 with 100 time steps | 51 |

| stepssteps                                                                               | 51 |

|------------------------------------------------------------------------------------------|----|

| Figure 4.3.2.5: GPU initial run result: simulation size of 1024×1024 with 100 time steps | 52 |

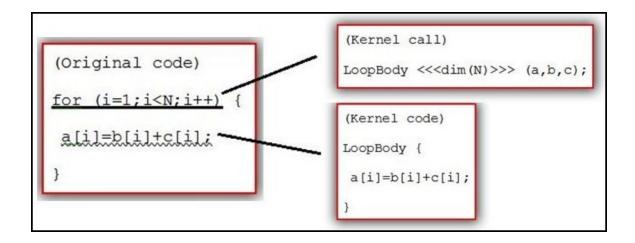

| Figure 5.1.1: CUDA kernel pseudo call and code                                           | 56 |

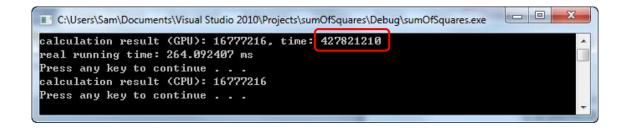

| Figure 5.1.2: sumOfSquares: initial run result.                                          | 59 |

| Figure 5.1.3: sumOfSquares test result with 256 threads defined                          | 60 |

| Figure 5.1.4: sumOfSquares test result: fixed way for data access                        | 61 |

| Figure 5.1.5: sumOfSquares test result: with BLOCK_NUM of 32 defined                     | 61 |

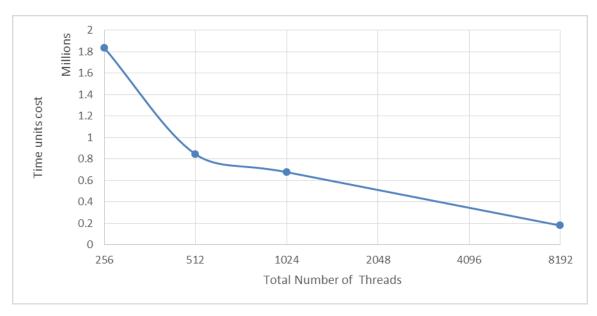

| Figure 5.1.6: Four representative cases for general speed-up comparison                  | 62 |

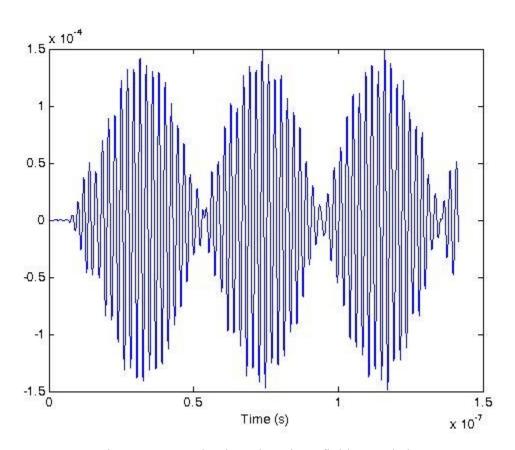

| Figure 5.4.1a: The time-domain E-field recorded                                          | 70 |

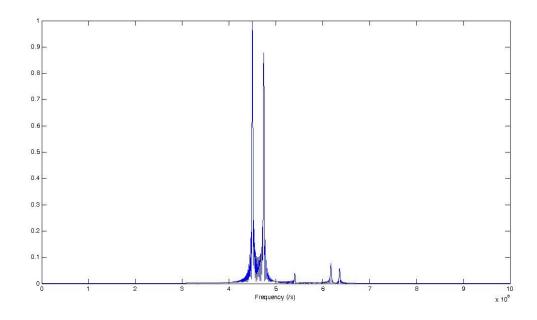

| Figure 5.4.1b: The E-field in the frequency domain.                                      | 71 |

| Figure 5.4.1.1: FDTD simulation size of 100×100 with 1000 time steps (CPU)               | 71 |

| Figure 5.4.1.2: FDTD simulation size of 500×500 with 1000 time steps (CPU)               | 72 |

| Figure 5.4.1.3: FDTD simulation size of 1000×1000 with 1000 time steps (CPU)             | 72 |

| Figure 5.4.1.4: FDTD simulation size of 2000×2000 with 1000 time steps (CPU)             | 72 |

| Figure 5.4.1.5: FDTD simulation size of 5000×5000 with 1000 time steps (CPU)             | 72 |

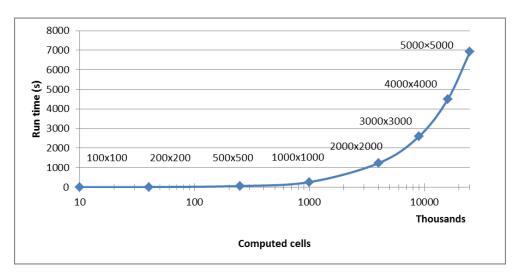

| Figure 5.4.1.6: Simulation results on CPU                                                | 72 |

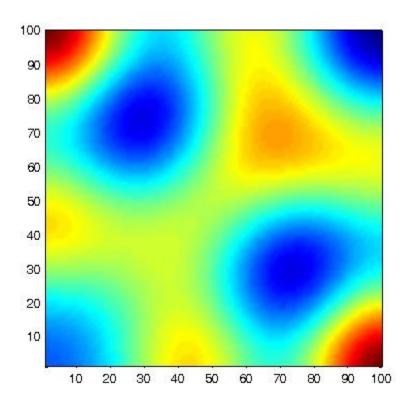

| Figure 5.4.1.7: FDTD simulation result of Hz field distribution (1000 time steps)        | 73 |

| Figure 5.4.1.8: Running time: FDTD simulation with size of 100×100 (GPU)                 | 74 |

| Figure 5.4.1.9: Running time: FDTD simulation with size of 500×500 (GPU)                 | 74 |

| Figure 5.4.1.10: Running time: FDTD simulation with size of 1000×1000 (GPU)              | 74 |

| Figure 5.4.1.11: Running time: FDTD simulation with size of 2000×2000 (GPU)              | 74 |

| Figure 5.4.1.12: Running time: FDTD simulation with size of 5000×5000 (GPU)              | 74 |

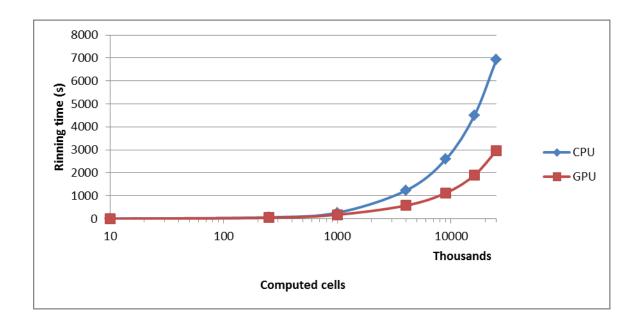

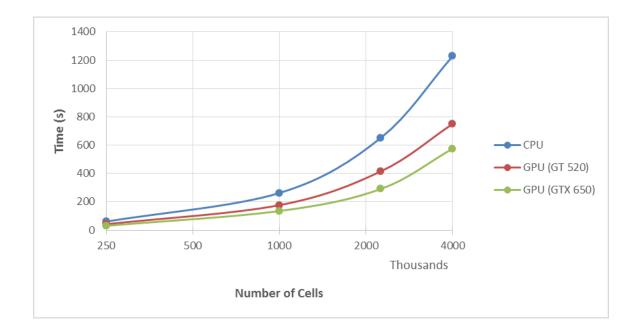

| Figure 5.4.1.13: Comparison between CPU and CUDA GPU simulation speeds                | 75 |

|---------------------------------------------------------------------------------------|----|

| Figure 5.4.1.14: Plot of simulation results to compare accuracy between CPU and GPU   | 76 |

| Figure 5.4.1.15 General local speed-up comparison.                                    | 76 |

| Figure 5.5.1.1: ACEnet test operation: check job status – waiting                     | 79 |

| Figure 5.5.1.2: ACEnet test operation: check job status – running                     | 79 |

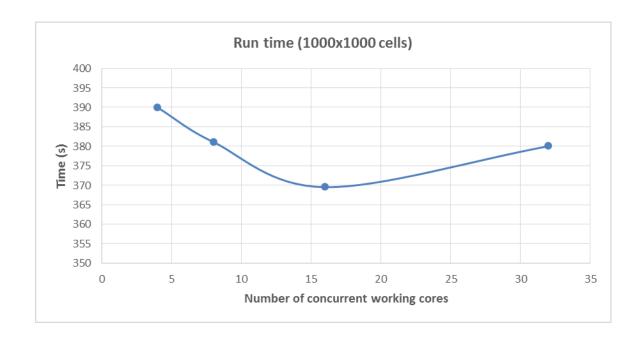

| Figure 5.5.1.3: ACEnet running times with different number of cores (1000×1000 cells) | 79 |

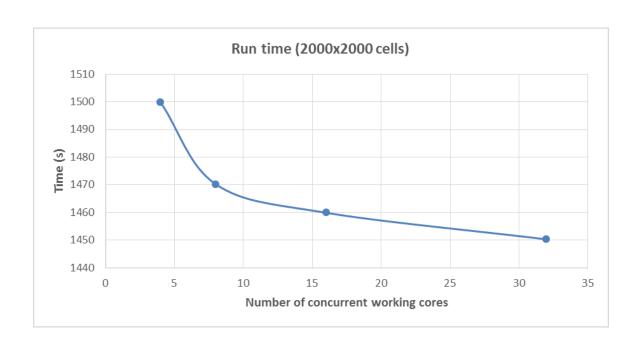

| Figure 5.5.1.4: ACEnet running times with different number of cores (2000×2000 cells) | 80 |

| Figure 5.5.2.1: Matlab profiler to check the bottleneck                               | 83 |

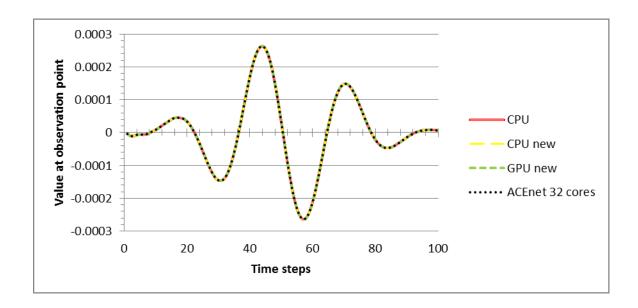

| Figure 5.5.2.2: Plot of simulation accuracy comparison                                | 84 |

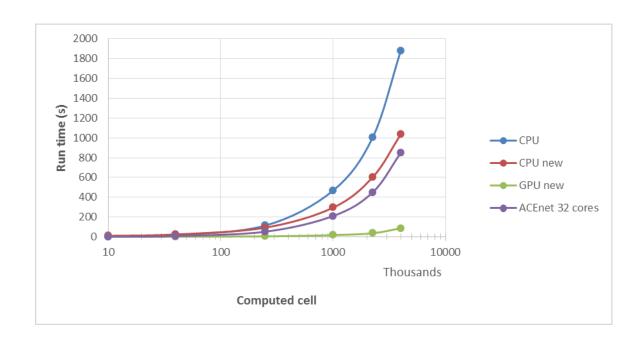

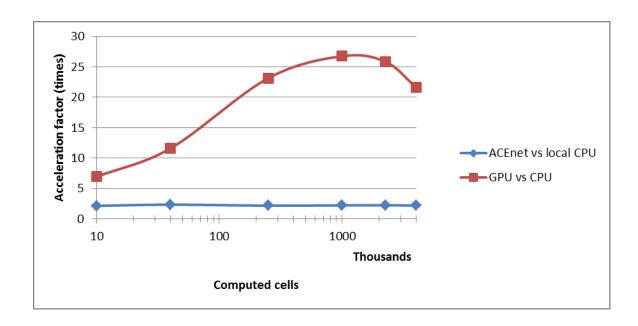

| Figure 5.5.2.3: General speed-up comparison                                           | 85 |

| Figure 5.5.2.4: Speed-up tendency with increasing computing scales                    | 86 |

#### **ABSTRACT**

Graphics Processing Unit (GPU) programming techniques have been applied to a range of scientific and engineering computations. In computational electromagnetics, uses of the GPU technique have dramatically increased since the release of NVIDIA's Compute Unified Device Architecture (CUDA), a powerful and simple-to-use programmer environment that renders GPU computing easy accessibility to developers not specialized in computer graphics.

The focus of recent research has been on problems concerning the Finite-Difference Time-Domain (FDTD) simulation of electromagnetic (EM) fields. Traditional FDTD methods sometimes run slowly due to large memory and CPU requirements for modeling electrically large structures. Acceleration methods such as parallel programming are then needed. FDTD algorithm is suitable for multi-thread parallel computation with GPU. For complex structures and procedures, high performance GPU calculation algorithms will be crucial.

In this work, we present the implementation of GPU programming for acceleration of computations for EM engineering problems. The speed-up is demonstrated through a few simulations with inexpensive GPUs and ACEnet, and the attainable efficiency is illustrated with numerical results. Using C, CUDA C, Matlab GPU, and ACEnet, we make comparisons between serial and parallel algorithms and among computations with and without GPU and CUDA, different types of GPUs, and personal computers and ACEnet. A maximum of 26.77 times of speed-up is achieved, which could be further boosted with development of new hardware in the future. The acceleration in runtime will make many investigations possible and will pave the way for studies of large-scale computational electromagnetic problems that were previously impractical. This is a field that definitely invites more in-depth studies.

#### LIST OF ABBREVIATIONS USED

ACEnet Atlantic Computational Excellence Network

BEM Boundary Element Method

CCM custom computing machines

CPU Central Processing Unit

CUBLAS CU Basic Linear Algebra Subroutines

CUDA Compute Unified Device Architecture

CUFFT CU Fast Fourier Transform

DDA Discrete Dipole Approximation

DRAM dynamic random access memory

DSM Distributed Shared Memory

EM Electromagnetics

FDM Finite Difference Method

FDTD Finite-Difference Time-Domain

FEM Finite Element Method

FMM Fast Multi-pole Method

FPGA field-programmable gate arrays

GPGPU General-Purpose Graphics Processing Unit

GPU Graphics Processing Unit

HPC High-Performance Computing

MIMD multiple-instruction-multiple-data

MISD multiple-instruction-single-data

MLFMM multi-level fast multi-pole methods

MoM Method of Moments

NVCC NVIDIA CUDA Compiler

PDE partial differential equations

PTX Parallel Thread eXecution

SFP special function processor

SIMD single-instruction-multiple-data

SISD single-instruction-single-data

SM Shared Memory

SMP Symmetrical Multi-Processing

TFL Thread For Line

TFP Thread For Point

TLM Transmission Line Matrix

TPC Texture Processor Cluster

#### **ACKNOWLEDGEMENTS**

I extend heartfelt appreciation to my supervisor, Dr. Zhizhang Chen, who introduced me to this special and challenging research topic and motivated me throughout the entire course of this thesis. He has the attitude and the substance of a researcher – continually and convincingly conveying a spirit of adventure through exploration. I received generous support and encouragement from him and also learned a lot from him.

As well, I would like to express my gratitude to my co-supervisor, Dr. Poman So, for his insightful comments, meticulous suggestions, and careful modifications. They are very important to my work and are certainly a huge help to me.

My thanks also go to my committee members, Dr. Sergey Ponomarenko and Dr. William Phillips, for their willing participation in the defense process and their kind advice.

I am particularly grateful to all my colleagues at the RF/Microwave Wireless Research Laboratory for their long-term support and kindness, especially Shunchuan Yang. Without their help, this thesis would not have materialized.

I owe a deep thank you to my best friends, Han Zhang and Luyu Wang, for their faithful companionship and warm encouragement over the past two memorable years.

Last but not least, I would like to thank my wonderful parents. Without their love, support, patience, and persistent encouragement throughout my degree, I would not have made it. This thesis is dedicated to them.

#### **CHAPTER 1 INTRODUCTION**

This chapter introduces the research background and motivation. The thesis outline is given at the end.

#### 1.1 RESEARCH BACKGROUND

In recent years, GPU (Graphics Processing Unit) programming techniques are increasingly being used in a range of scientific and engineering computer simulations [1]. In the area of field simulation, reports on this technique have begun to increase as well, particularly since the release of NVIDIA's CUDA (Compute Unified Device Architecture) [2], a powerful and simple-to-use programmer environment available for NVIDIA cards. CUDA makes GPU computing accessible to developers who are not necessarily experts in computer graphics.

Initially, GPUs were not designed for general purpose programming, and high level programming languages were not readily available. Programmers were thus required to learn the intricacies of specialized, low-level hardware languages. For instance, the FDTD implementations in [3], [4] and [5] are based on OpenGL. Meanwhile, CUDA is a general purpose parallel computing architecture. To program CUDA's architecture, developers can use C, which can then be run at high performance on a CUDA-enabled processor. The CUDA architecture and its associated software provide a small set of extensions to standard programming languages, like C, that enable straightforward implementation of parallel algorithms [6].

Therefore, we can focus on the task of parallelization of algorithms instead of spending all of our time on their implementation. The CPUs and GPUs are treated as separate devices that have their own memory spaces. Simultaneous computation on both CPUs and GPUs are also allowed by this configuration without contention for memory resources [7].

#### 1.2 MOTIVATION

The computational power of graphics cards have been utilized within numerical electromagnetic problems. Among these, some work (e.g., [8] - [12]) is concerned with the problems of FDTD simulation of EM fields. The problems treated thus far, however, are rather limited in their structures and calculation procedures. If we are able to treat most of calculations and procedures only by basic FDTD equations like wave propagation calculation, it would be comparatively easy to extract the GPU's inherent acceleration capability because basic FDTD algorithm is essentially suited to the multithread parallel computing function of GPU. For complex problems, the type of algorithm employed and the computer circumstances being used are deeply relevant to the computation speed. In other words, for complex problems, discussions of GPU implementation algorithm are quite valuable and significant. Developments in the design of GPUs have occurred at a much faster pace than with CPUs, and powerful processing units have been designed solely for the processing of computer graphics. For instance, the current generation of GPU-based NVIDIA Tesla C1060 Computing Processors is running at approximately 1.3 GHz, with a 512 bit data and memory bandwidth of 102 GB/sec [13]. While GPU clock speed seems slow compared to modern 3.8 GHz Pentium CPUs or 3.0 GHz Core Duos, the parallelism provided by the graphics cards enables better efficiency in computations [9]. Due to this potential in faster computations, GPU programming and CUDA have caught the attention of the scientific and engineering computing community.

In this thesis, we explain how to implement GPU versions of some simulation algorithms to achieve improved acceleration performance, especially on ACEnet. The attainable efficiency is demonstrated by discussing studies of some interaction problems and implementing the algorithms on off-the-shelf inexpensive GPUs. The wrap-up shows the consistency of the results between serial and parallel algorithms. Furthermore, observable speed-up is obtained compared with traditional computation.

#### 1.3 THESIS OUTLINE

This thesis is organized as follows:

Chapter 2 introduces the computational EM methods and their applications, including the Finite Element Method, the Moment Method, the Finite-Difference Time-Domain Method, Yee cell, and differentials of Maxwell's equations.

Chapter 3 focuses on GPU programming and CUDA architecture. A short summary of the various types of memory available on a GPU are given here, and differences between a CUDA GPU and a CPU are discussed. CUDA's potential in reducing computation time for the FDTD method is also explored.

Chapter 4 discusses implementations of CUDA-enabled FDTD on GPUs. Memory allocation and coalescing requirements are also discussed. In this chapter, the complexity involved in programming using GPU framework is introduced, and difficulties involved in implementing two- and three-dimensional grids and blocks of threads on CUDA are explained.

Chapter 5 investigates detailed acceleration methods. Performance optimization revolves around some basic strategies, including maximizing parallel execution to achieve maximum utilization and optimizing memory usage to achieve maximum speed-up. Tests were run and accelerated using various approaches on different platforms. Thorough comparisons are provided.

Chapter 6 summarizes the thesis and suggests potential future research directions for parallel methods. As a wrap-up, this chapter presents an overall conclusion of the thesis as well as some improvements that can be made to in-depth acceleration.

# CHAPTER 2 OVERVIEW OF THE FINITE DIFFERENCE TIME DOMAIN (FDTD) METHOD

#### 2.1 COMPUTATIONAL EM METHODS AND THEIR APPLICATIONS

Since the establishment of basic Maxwell's equations of electromagnetic fields, EM and wave theory have been used in various research areas such as geology, life science, medicine, material science, and information technology. EM and wave theory are also used in other fields like radio propagation, antennas, radars, optical communications, mobile communications, geological exploration, and bio-electromagnetics [14]. In practical problems, electromagnetic analysis is often quite complex and there are usually no easy analytical solutions to the boundary value problems of Maxwell's equations. Moreover, electronic analysis is difficult, expensive, and time-consuming. Therefore, it is much more practical to explore a solution for an electromagnetic theoretical equation to obtain the numerical results of field characteristics for a specific environment.

Earlier studies of EM numerical methods focused on the electrostatic field and time-harmonic steady state of Maxwell's equations Finite Difference Method (FDM). The Finite Element Method extended from structural mechanics calculations, high-frequency asymptotic, Method of Moments, and some other integral methods. In 1966, Yee presented the Finite-Difference Time-Domain method, which could directly solve the time-domain equations [15]. In the 1970s, several computational electromagnetic methods were proposed as improvements, such as Transmission Line Matrix (TLM) [16], Discrete Dipole Approximation (DDA) [17], Fast Multi-pole Method (FMM) [18], and Boundary Element Method (BEM) [19].

Next, we will introduce several widely applied computational electromagnetic methods.

#### 2.1.1 Finite Element Method

The Finite Element Method is based on the variational principle and is widely used in various types of physical field numerical calculation. In the 1940s, Hrennikoff [20], McHenry [21] and Courant [22] originally proposed the idea of a mesh discrete element, but their approaches differed significantly. Hrennikoff's work discretized the domain by using a lattice analogy, while Courant's approach divided the domain into finite triangular subregions to solve second-order elliptic partial differential equations (PDEs) that arise from the problem of torsion of a cylinder. Courant's contribution was evolutionary, drawing on a large body of earlier results for PDEs developed by Rayleigh, Ritz, and Galerkin [23]. The finite element method obtained its real impetus in the 1960s and 1970s with the developments of J.H. Argyris and co-workers at the University of Stuttgart, R.W. Clough and co-workers at UC Berkeley, O.C. Zienkiewicz and coworkers at the University of Swansea, and Richard Gallagher [24] and co-workers at Cornell University. A rigorous mathematical basis to the finite element method was provided in 1973 with a publication by Strang and Fix [25]. The method has since been generalized for the numerical modeling of physical systems in a wide variety of engineering disciplines, e.g., electromagnetism, heat transfer, and fluid dynamics [26].

FEM utilizes mesh interpolation to divide the continuous structure into a finite number of non-overlapping cells and to select the nodes as the interpolation points of functions to solve. Many physical phenomena in engineering and science can be described in terms of partial differential equations (PDE). In general, solving these equations by classical analytical methods for arbitrary shapes is almost impossible. The finite element method is a numerical approach by which these PDE can be solved approximately. It is widely used in diverse fields to solve static and dynamic problems of solid or fluid mechanics, electromagnetics, biomechanics, etc.

There are two key words in FEM: discretization and interpolation. First, we need to discretize the equations. The subdivision of a whole domain into simpler parts has several advantages, such as accurate representation of complex geometry, inclusion of dissimilar material properties, easy representation of the total solution, and capture of local effects [27]. We then can manage to solve the discrete system of equations, eventually followed

by interpretation of the obtained results and errors analysis. Generally, the advantage of finite element analysis is that it can move us toward a solution when we have a very complicated shape undergoing very complicated loads (e.g., temperature, vibration, earthquakes, yielding, spread of plasticity), or when we wish to examine a part in greater detail (more common in mechanical engineering).

#### 2.1.2 Moment Method

The method of moments (MoM) or boundary element method (BEM) is a numerical computational method of solving linear partial differential equations that have been formulated as integral equations (i.e., in boundary integral form). It can be applied in many areas of engineering and science, including fluid mechanics, acoustics, electromagnetics, fracture mechanics, and plasticity [28]. In 1962, Dr. Mei proposed MoM to solve integral equations [29], and Harrington made a comprehensive in-depth analysis in terms of using the moment method to solve electromagnetic problems [30] [31].

MoM has become more popular since the 1980s. It is especially efficient in terms of computational resources for problems with a small surface/volume ratio, since it requires calculating only boundary values rather than values throughout space. Conceptually, it works by constructing a "mesh" over the modeled surface. For many problems, however, MoM would be substantially less efficient than volume-discretization methods (i.e., finite element method, finite difference method, finite volume method). Boundary element formulations typically give rise to fully populated matrices, which means that the storage requirements and computational time tend to increase based on the square of the problem size. Finite element matrices, by contrast, are typically banded and the storage requirements for the system matrices grow linearly with the problem size. We can use compression techniques multi-pole expansions (e.g., adaptive cross approximation/hierarchical matrices) to ameliorate these problems, though at the cost of added complexity and with a success-rate that depends heavily on the nature and geometry of the problem [28].

Moment method is relatively simple in terms of the analytical part, but the resulting matrix is often large sparse matrix, or full matrix, which brings in heavy computing workloads. The three-dimensional problem solving is especially hard in this case with very high memory storage requirements. Therefore, in recent years the development of MoM concentrated on an effective sparse solution of the three-dimensional structures, ensuring the accuracy of the premise. Examples of this are fast multi-pole methods (FMM) [32] and multilevel fast multi-pole methods (MLFMM) [33]. MoM is applicable to problems for which Green's functions can be calculated, which usually involve fields in linear homogeneous media. This places considerable restrictions on the range and generality of problems suitable for boundary elements [34]. The formulation can contain nonlinearities, although they generally introduce volume integrals that require the volume to be discretized before solution, removing an oft-cited advantage of MoM.

#### 2.1.3 Finite-Difference Time-Domain Method

The FDTD method is a numerical method introduced by Yee in the 1960s [15] to solve the differential form of Maxwell's equations in time-domain. Although the method has existed for over four decades, enhancements to improve FDTD are continuously being published [35]. It is easy to understand and has an exceptionally simple implementation for a full wave solver. It is at least an order of magnitude less work to implement a basic FDTD solver than either an FEM or MoM solver. FDTD is the only technique where one person can realistically implement oneself in a reasonable time frame, but even this will be for a quite specific problem [36].

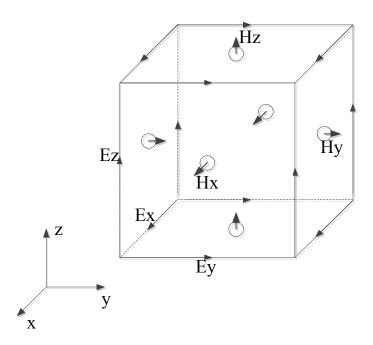

Maxwell's curl equations are discretized by the FDTD method into time and spatial domains. The electric fields are generally located at the edge of the Yee Cell, while the magnetic fields are located at the center of the Yee Cell, as shown in Figure 2.1.3.1. In three dimensions, the number of cells in one time step can easily be in orders of millions. A dimension of  $100 \times 100 \times 100$  cells already yields a total of one million cells. For

example, in [37], a high resolution head model of an adult male has a total of 4,642,730 Yee cells, with each cell having a dimension of  $1\times1\times1$  mm<sup>3</sup>.

Figure 2.1.3.1: Position of the electric and magnetic fields in Yee's scheme.

FDTD is a versatile modeling technique used to solve Maxwell's equations. It is intuitive, so users can easily understand how to handle it and know what to expect. It is also a time-domain technique. When a broadband pulse (such as a Gaussian pulse) is used as the source, the response of the system over a wide range of frequencies can be obtained with a single simulation. This is useful in applications where resonant frequencies are not exactly known or anytime that a broadband result is desired. Since FDTD calculates the E and H fields everywhere in the computational domain as they evolve in time, it lends itself to providing animated displays of the electromagnetic field movement through the model. This type of display is useful in understanding what is going on in the model, and to help ensure that the model is working correctly. FDTD uses the E and H fields directly. Since most EMI/EMC modeling applications are interested in the E and H fields, it is convenient that no conversions must be made after the simulation has run to get these values [38].

#### 2.2 YEE'S FDTD GRIDS AND DISCRETIZATION OF MAXWELL'S EQUATIONS

Electromagnetic processes in the media space meet the requirements of Maxwell's curl equations:

$$\nabla \times \mathbf{H} = \frac{\partial \mathbf{D}}{\partial t} + \mathbf{J} \tag{2-2-1a}$$

$$\nabla \times \mathbf{E} = -\frac{\partial \mathbf{B}}{\partial t} \tag{2-2-1b}$$

Combined with structural equations of isotropic media:

$$\mathbf{D} = \varepsilon \mathbf{E} \tag{2-2-2a}$$

$$\mathbf{B} = \mu \mathbf{H} \tag{2-2-2b}$$

$$\mathbf{J} = \sigma \mathbf{E} \tag{2-2-2c}$$

In a Cartesian coordinate system, we can expand them to get scalar Maxwell's equations, as follows:

$$\frac{\partial H_x}{\partial t} = \frac{1}{\mu} \left( \frac{\partial E_y}{\partial z} - \frac{\partial E_z}{\partial y} \right) \tag{2-2-3a}$$

$$\frac{\partial H_y}{\partial t} = \frac{1}{\mu} \left( \frac{\partial E_z}{\partial x} - \frac{\partial E_x}{\partial z} \right) \tag{2-2-3b}$$

$$\frac{\partial H_z}{\partial t} = \frac{1}{\mu} \left( \frac{\partial E_x}{\partial y} - \frac{\partial E_y}{\partial x} \right) \tag{2-2-3c}$$

$$\frac{\partial E_x}{\partial t} = \frac{1}{\varepsilon} \left( \frac{\partial H_z}{\partial y} - \frac{\partial H_y}{\partial z} - \sigma E_x \right)$$

(2-2-3d)

$$\frac{\partial E_{y}}{\partial t} = \frac{1}{\varepsilon} \left( \frac{\partial H_{x}}{\partial z} - \frac{\partial H_{z}}{\partial x} - \sigma E_{y} \right) \tag{2-2-3e}$$

$$\frac{\partial E_z}{\partial t} = \frac{1}{\varepsilon} \left( \frac{\partial H_y}{\partial x} - \frac{\partial H_x}{\partial y} - \sigma E_z \right) \tag{2-2-3f}$$

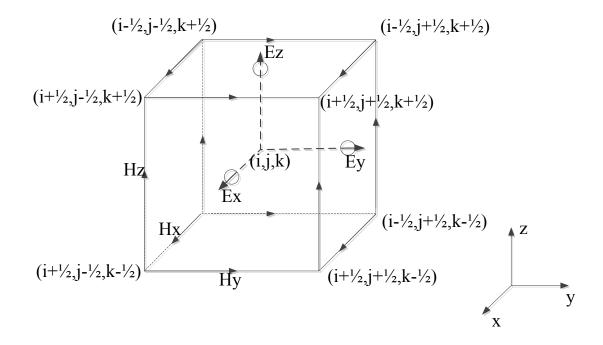

Yee did the alternate sampling for the electromagnetic components in space, so that each electric field component is surrounded by four magnetic field components and each magnetic field component is surrounded by four electric field components. As shown in Figure 2.2.1, this is called a Yee Cell. The sampling basis is simple, intuitive, and satisfies the Gauss theorem [39]. Applying it to the scalar Maxwell's curl equations (2-2-3), we obtain numerical solutions to the electromagnetic problems.

Figure 2.2.1: Yee's cell in FDTD.

If we use second-order central difference to replace the differential in (2-2-3) and do the sampling in time domain for the E and H every half-step length, we can obtain the time-domain electromagnetic field recurrence formula:

$$\begin{split} H_{x}^{n+\frac{1}{2}} \Big( i, j + \frac{1}{2}, k + \frac{1}{2} \Big) \\ &= H_{x}^{n-\frac{1}{2}} \Big( i, j + \frac{1}{2}, k + \frac{1}{2} \Big) + \frac{\Delta t}{\mu} \Big[ \frac{E_{y}^{n} \Big( i, j + \frac{1}{2}, k + 1 \Big) - E_{y}^{n} \Big( i, j + \frac{1}{2}, k \Big)}{\Delta z} \\ &- \frac{E_{z}^{n} \Big( i, j + 1, k + \frac{1}{2} \Big) - E_{z}^{n} \Big( i, j, k + \frac{1}{2} \Big)}{\Delta y} \Big] \end{split}$$

$$(2-2-4a)$$

$$\begin{split} H_{y}^{n+\frac{1}{2}} \Big( i + \frac{1}{2}, j, k + \frac{1}{2} \Big) \\ &= H_{y}^{n-\frac{1}{2}} \Big( i + \frac{1}{2}, j, k + \frac{1}{2} \Big) + \frac{\Delta t}{\mu} \Big[ \frac{E_{z}^{n} \Big( i + 1, j, k + \frac{1}{2} \Big) - E_{z}^{n} \Big( i, j, k + \frac{1}{2} \Big)}{\Delta x} \\ &- \frac{E_{x}^{n} \Big( i + \frac{1}{2}, j, k + 1 \Big) - E_{x}^{n} \Big( i + \frac{1}{2}, j, k \Big)}{\Delta z} \Big] \end{split}$$

$$(2-2-4b)$$

$$\begin{split} H_{z}^{n+\frac{1}{2}} \Big( i + \frac{1}{2}, j + \frac{1}{2}, k \Big) \\ &= H_{z}^{n-\frac{1}{2}} \Big( i + \frac{1}{2}, j + \frac{1}{2}, k \Big) + \frac{\Delta t}{\mu} \Big[ \frac{E_{x}^{n} \Big( i + \frac{1}{2}, j + 1, k \Big) - E_{x}^{n} \Big( i + \frac{1}{2}, j, k \Big)}{\Delta y} \\ &- \frac{E_{y}^{n} \Big( i + 1, j + \frac{1}{2}, k \Big) - E_{y}^{n} \Big( i, j + \frac{1}{2}, k \Big)}{\Delta x} \Big] \end{split}$$

(2-2-4c)

$$\begin{split} E_{x}^{n+1}\left(i+\frac{1}{2},j,k\right) \\ &= \frac{2\varepsilon - \Delta t\sigma}{2\varepsilon + \Delta t\sigma}E_{x}^{n}\left(i+\frac{1}{2},j,k\right) + \frac{2\Delta t}{2\varepsilon + \Delta t\sigma} \\ &\quad \times [\frac{H_{z}^{n+\frac{1}{2}}\left(i+\frac{1}{2},j+\frac{1}{2},k\right) - H_{z}^{n+\frac{1}{2}}\left(i+\frac{1}{2},j-\frac{1}{2},k\right)}{\Delta y} \\ &\quad - \frac{H_{y}^{n+\frac{1}{2}}\left(i+\frac{1}{2},j,k+\frac{1}{2}\right) - H_{y}^{n+\frac{1}{2}}\left(i+\frac{1}{2},j,k-\frac{1}{2}\right)}{\Delta z}] \end{split}$$

$$E_{y}^{n+1}\left(i,j+\frac{1}{2},k\right) = \frac{2\varepsilon - \Delta t\sigma}{2\varepsilon + \Delta t\sigma} E_{y}^{n}\left(i,j+\frac{1}{2},k\right) + \frac{2\Delta t}{2\varepsilon + \Delta t\sigma} \\ \times \left[\frac{H_{x}^{n+\frac{1}{2}}\left(i,j+\frac{1}{2},k+\frac{1}{2}\right) - H_{x}^{n+\frac{1}{2}}\left(i,j+\frac{1}{2},k-\frac{1}{2}\right)}{\Delta y} - \frac{H_{z}^{n+\frac{1}{2}}\left(i+\frac{1}{2},j+\frac{1}{2},k\right) - H_{z}^{n+\frac{1}{2}}\left(i-\frac{1}{2},j+\frac{1}{2},k\right)}{\Delta x}\right]$$

(2-2-4e)

$$\begin{split} E_{z}^{n+1}\left(i,j,k+\frac{1}{2}\right) &= \frac{2\varepsilon - \Delta t\sigma}{2\varepsilon + \Delta t\sigma} E_{z}^{n}\left(i,j,k+\frac{1}{2}\right) + \frac{2\Delta t}{2\varepsilon + \Delta t\sigma} \\ &\times \left[\frac{H_{y}^{n+\frac{1}{2}}\left(i,j+\frac{1}{2},k+\frac{1}{2}\right) - H_{y}^{n+\frac{1}{2}}\left(i,j-\frac{1}{2},k+\frac{1}{2}\right)}{\Delta x} - \frac{H_{x}^{n+\frac{1}{2}}\left(i,j+\frac{1}{2},k+\frac{1}{2}\right) - H_{x}^{n+\frac{1}{2}}\left(i,j-\frac{1}{2},k+\frac{1}{2}\right)}{\Delta y} \right] \end{split}$$

(2-2-4f)

In the equations above,  $\Delta x$ ,  $\Delta y$ ,  $\Delta z$  are space steps at three directions in the Cartesian coordinates, respectively, while  $\Delta t$  is the time step.  $(i + \frac{1}{2}, j, k)$  and its similar forms are coordinates of Yee grid point field components, as illustrated in Figure 3.1.  $\sigma$  and  $\varepsilon$  are conductivity and permittivity at the current calculation point. Superscripts like n + 1 and  $n + \frac{1}{2}$  are index values of the time steps. It can be seen that each component of E and E at that time has the same difference of half a step, and thus takes the alternate recursion in the time domain, updating the EM field distribution over time.

From Figure 3.1 and Equation (3.1.4), we know that in FDTD recursion of time domain, the computation of one field value at all positions in space is conducted in accordance with a unified recursive formula. Additionally, the field value of a grid point is only

related to its previous field value and its four surrounding grid points, without regard to the overall distribution of the electromagnetic field.

#### 2.3 FDTD ENABLING HARDWARE PLATFORM

We know that Maxwell's curl equations in free space for one-dimension are

$$\frac{\delta E_x}{\delta t} = -\frac{1}{\varepsilon_0} \frac{\delta H_y}{\delta z} \tag{2-3-1a}$$

$$\frac{\delta H_y}{\delta t} = -\frac{1}{\mu_0} \frac{\delta E_x}{\delta z} \tag{2-3-1b}$$

Using the finite difference method of central approximation and rearranging [40], the electric fields and magnetic fields are calculated alternately over the entire spatial domain at time step n. This process continues over all time steps until convergence is achieved. Depending on the size of the computation domain, millions of iterations could be required to solve the differential equations. However, the benefit of using the FDTD method is that it only requires exchange of data with neighbouring cells, without regard to the overall distribution of the electromagnetic field. This provides an easy way of decomposition into multiple sub-process calculations and thus can be a natural parallelizable algorithm. Because of this, FDTD has drawn intense interest from researchers.

#### 2.3.1 CPU-Based FDTD

In the 1980s, reports emerged regarding implementing FDTD parallel computing on large vector machines [41] [42]. Before PC networking technology was widely applied, the use of the FDTD method on mainframe computers dominated this field. However, these computers or systems were too expensive for general researchers and so the method not been extensively applied. Then, with the development of PC and network equipment,

parallel computing systems using low-cost computers began to emerge. Initially from the parallel 386 CPU [43] to multicore Xeon CPUs [44], researchers have continuously been promoting the parallel models and algorithms.

Parallel computing hardware devices based on traditional CPU have shared or distributed memory parallel systems. With the popularity of multi-core processors, there are increasing numbers of distributed memory parallel systems. Parallel implementations are mostly in view of FDTD domain decomposition, which divides the whole computing area into a plurality of sub-areas according to the number of sub-computing units. Each sub-unit is responsible for processing iterations in a sub-area of the electromagnetic field. In the course of forwarding time steps, there will be synchronizations between the cells. Moreover, if the computation is implemented on a distributed memory parallel system, there have to be data transferring between the cells.

Along with the further improvement of parallel computing systems, mature parallel computing software and models on FDTD are also promoted. These include MPI [45] and PVM [46] based on message passing, OpenMP based on single computer multithreaded programming and the distributed memory parallel systems combining the two models. W. Yu (2007) conducted a detailed study on the FDTD parallel algorithm, border data exchange, computational efficiency and other issues using parallel computer systems at the University of Pennsylvania and IBM Blue Gene supercomputer, which took MPI as the basic model. In a good network environment, the parallel efficiency was able to reach up to 90% with over 200 processors [47]. In 2004, a combination of MPI and OpenMP was proposed and achieved the implementation of FDTD parallel computing on SGI Origin 2000 [48]. In 2008, one more parallel solution was realized on hyper-threading clusters composed of Pentium four CPUs [49]. However, due to limitations in network equipment, the efficiency was lower than mainframe computers and declined further with each additional computing unit.

#### 2.3.2 FPGA-Based FDTD

The software execution of the FDTD method has the problem of limited computational speed. An effective approach to construct parallelism is the implementation with field-programmable gate arrays (FPGAs). The FDTD algorithm is computationally intensive but has a simple computation kernel, making it suitable for implementation on FPGA co-processor boards of high performance parallel computers. FPGA is one of the programmable-logic devices where end-users can configure their own logic circuits over and over on the semiconductor chip [50]. So far, fundamental floating-point operations and their applications on FPGAs have been studied.

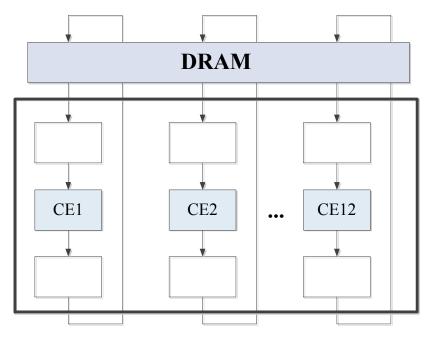

In 2005, FPGA-based floating-point co-processors were proposed for the matrix-vector multiplication and the matrix multiplication in [51] and [52]. Although such fundamental operations can be utilized for the FDTD method, these co-processors have an essential problem in that data transfer to FPGAs becomes bottlenecked. Since the I/O bandwidth of an FPGA chip is limited, building custom computing machines (CCMs) as a co-processor is essentially not scalable due to the I/O bottleneck in streaming data to FPGAs from external components. Durbano et al. designed 12 dedicated computing engines to do the parallel calculation, as shown in Figure 2.3.2.1 [53], while Kawaguchi et al. designed different hardware for different computing portions so that they could process in parallel for different field values. They also utilized specific PML for hardware circuits and optimized for memory modules [54].

Figure 2.3.2.1: FDTD computing design using FPGA.

Apart from the relatively high cost of hardware, the technique also had several problems in terms of issues like memory access and multi-parallel. Additionally, it is difficult to implement complex FDTD using hardware programming language. Due to all of these issues, FPGA-based FDTD parallel computing systems are not widely applied.

#### 2.3.3 GPU-Based FDTD

As one of the main components of PC, GPU has a higher floating point computing capability compared to CPU. As well, its integrated process development is even faster than CPU, which offers a cost-effective solution for scientific computing parallelization. Meanwhile, FDTD has a strong parallelizability, so FDTD parallel computing on GPU has always attracted considerable attention.

The adoption of GPU computing for EM numerical methods is a relatively new issue, even though it is featuring a positive trend. This is also because of the recent publication of the Compute Unified Device Architecture (CUDA), a powerful and simple-to-use programmer environment available for NVIDIA cards that makes GPU computing

accessible to developers who are not experts at computer graphics. Several EM numerical methods are amenable to benefit from appealing GPU characteristics [55] [56] [57]. Among them, the FDTD algorithm is perhaps the best suited to be implemented in a GPU-enabled fashion. It is the simplest to describe, as it is an inherently data-parallel algorithm. It was therefore chosen in this thesis as a case study for demonstrating GPU capabilities, and for illustrating the software design and implementation efforts required for developing efficient parallel codes on a GPU.

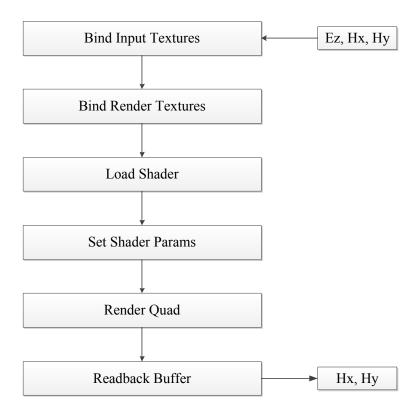

Traditional General-Purpose Graphics Processing Unit (GPGPU) implementation of FDTD is relatively complex as it needs to map the entire calculation process to the graphics pipeline. Two-dimensional TM wave FDTD recursion of Hx and Hy proceeds as follows:

- Bind input parameters to texture units;

- Bind them to an object that needs to be rendered, which means to virtualize the whole area into a quadrilateral, and each component represents one single part;

- Load shader program and set its parameters. Write in accordance with recursive formula as the form of fragment program and load it into a storage area. One small section in Figure 2.3.3.1 is the compiled form of recursive formula. We can see the operations such as texture reading and multiply-add from it;

- Render a quadrilateral. Execute the fragment program process, conduct electromagnetic field recursion, and update Hx and Hy from the input field values;

- Read data from the texture buffer. Output the updated Hx and Hy value.

Figure 2.3.3.1: Traditional GPGPU parallel FDTD computing procedure.

This computing process involves numerous graphics concepts and the operation is complicated. In early GPU architecture, there were limitations using vertex and pixel processors to program, which did not take full advantage of the GPU floating point calculation superiority.

Since the release of NVIDIA CUDA, researchers have started to program in the novel GPU architecture without the help of graphics rendering. They only need to use pointers, memory replication, function calls, and some other familiar operations. In 2008, Sypek et al. realized fundamental FDTD parallel computation and achieved a great speed of 20 times faster for 3-D FDTD (unspecified type of GPU chip) [58]; Balevic et al. utilized 2-Dimensional block and realized FDTD based on wave equations upon GeForce 8800GTX (112sp); Valcarce et al. utilized 5 different kernels, calculated FDTD main area and PML area, realized 2-D FDTD computing under CPML absorbing boundary conditions, and worked out WiMAX signal distribution in the city.

#### CHAPTER 3 PARALLEL COMPUTING AND GPU ARCHITECTURE

#### 3.1 PARALLEL COMPUTING TECHNOLOGY

In the process of applying FDTD algorithm for electromagnetic simulation, the computed grids and time steps must be small enough so that the calculation requirements will be met with the increasing of the structure complexity. To reduce the simulation time, research has focused on parallel algorithms. FDTD has a natural characteristic of data parallelizability, which provides an excellent condition for its parallel computing implementation. To do this, we must first select the appropriate parallel system, then design the algorithm based on the parallel programming model, and finally implement it in the computing environment.

#### 3.1.1 Hardware

Michael J. Flynn created one of the earliest classification systems for parallel (and sequential) computers and programs, now known as Flynn's taxonomy [59]. Flynn classified programs and computers by whether they were operating using a single set or multiple sets of instructions, and whether or not those instructions were using a single set or multiple sets of data. There are four major types of classification. The single-instruction-single-data (SISD) classification is equivalent to an entirely sequential program. The single-instruction-multiple-data (SIMD) classification is analogous to doing the same operation repeatedly over a large data set. This is commonly done in signal processing applications. Multiple-instruction-single-data (MISD) is a rarely used classification. While computer architectures to deal with this were devised (such as systolic arrays), few applications that fit this class materialized. Multiple-instruction-multiple-data (MIMD) programs are by far the most common type of parallel programs [60]. According to memory and computing unit distribution, computer systems can also be divided into Shared Memory (SM), Symmetrical Multi-Processing (SMP) and Distributed Shared Memory (DSM) architectures.

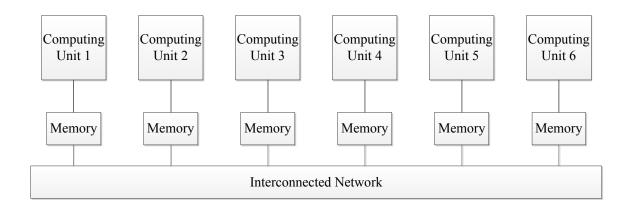

Conventional single-core CPU clusters and distributed computing architectures are typical DM parallel systems. As can be seen in Figure 3.1.1.1, this structure is quite suitable for parallel algorithms without computing unit communication. If the algorithm requires data communication between each computing unit, transit through other devices will be needed for messaging. Its performance can thus be greatly influenced by interconnected network devices. Meanwhile, DM architecture has an easy access to expand the scale and thus is extensively applied.

Figure 3.1.1.1: Parallel computing system: distributed memory architecture.

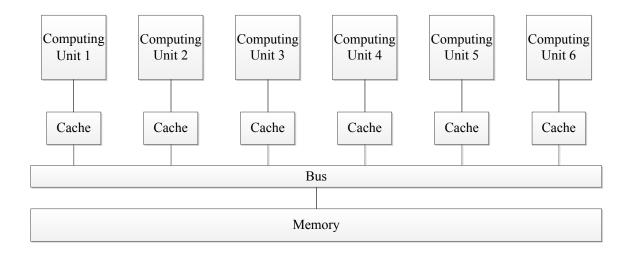

Multi-core CPUs and GPUs belong to shared memory parallel computing system architecture. As shown in Figure 3.1.1.2, all of its calculation units are able to access the memory in the same area via the bus of the device. There are cache devices in each calculation unit to accelerate the speed of data access. The data transferring process is not required for any algorithm, and the only thing that should be taken into account is synchronization of the calculation units.

Figure 3.1.1.2: Parallel computing system: shared memory architecture.

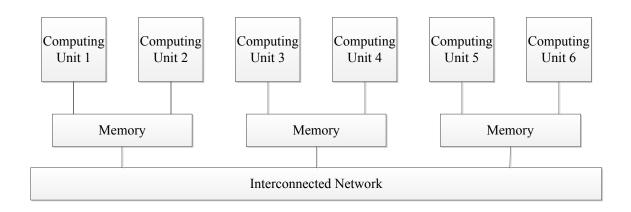

Multi-core CPUs connected in parallel through a network and multi-GPU platform belonging to DSM architecture. As can be seen in Figure 3.1.1.3, within an SMP, each computing unit can access the same memory area. Every unit can have private or public cache, and a number of SMPs build up the DM architecture through interconnected equipment components. Between GPUs, data can be transferred via the host memory or network equipment.

Figure 3.1.1.3: Parallel computing system: distributed shared memory architecture.

#### 3.1.2 Programming Model

Using a parallel computing system as a hardware basis, we then select the appropriate software development model and design parallel algorithms to achieve the desired programming results. For different parallel computing systems, we can choose different development models and design different parallel algorithms. The implementation used in this thesis – Compute Unified Device Architecture (CUDA) – can also be regarded as a parallel model.

CUDA is hardware and software architecture introduced by NVIDIA in 2006 [61]. The aim in developing CUDA was to provide developers with access to the parallel computational elements of NVIDIA GPUs. CUDA architecture enables NVIDIA GPUs to execute programs written in various high-level languages such as C, FORTRAN, OpenCL and Direct Compute. The newest architecture of GPUs by NVIDIA (codenamed "Fermi") also fully supports programming through the C++ language [62].

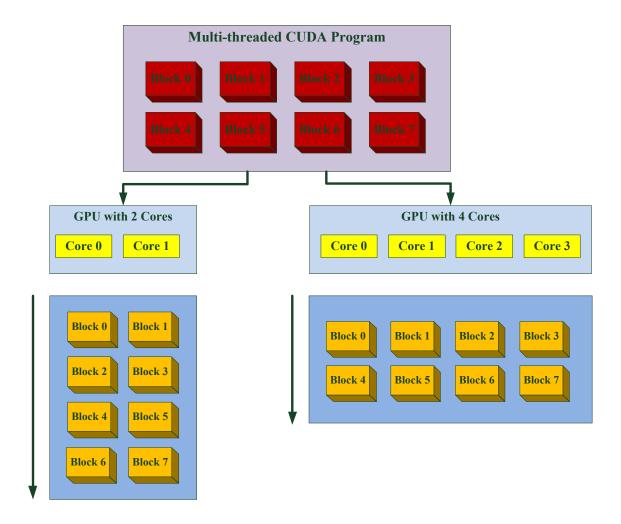

Because of advancements in technology, the processing power and parallelism of GPUs are continuously increasing. CUDA's scalable programming model makes it easy to provide this abstraction to software developers, allowing the program to automatically scale according to the capabilities of the GPU without any change in code, unlike traditional graphics programming languages such as OpenGL [63]. This is illustrated in Figure 3.1.2.1. A multithreaded program is partitioned into blocks of threads that execute independently from each other, so that a GPU with more cores will automatically execute the program in less time than a GPU with fewer cores.

Figure 3.1.2.1: Partitioned multi-threaded program.

(Source: NVIDIA CUDA C programming guide version 4.2, 2012.)

Because the GPU and CPU both serve different purposes in a computer, their microprocessor architectures, as shown in Figure 3.1.2.2, are very different. GPU devotes more transistors to data processing. While CPUs currently have up to six processor cores (Intel Core i7-970), a GPU has hundreds. For example, the NVIDIA Tesla 20-series has 448 CUDA cores [62].

Figure 3.1.2.2: CPU and GPU microprocessor architectures.

(Source: NVIDIA CUDA C programming guide version 4.2, 2012.)

Compared to the CPU, the GPU devotes more transistors to data processing than to data caching and flow control. This allows GPUs to specialize in math-intensive, highly parallel operations compared to CPUs, which serve as multi-purpose microprocessors. Therefore, calculations of the FDTD algorithm are potentially much faster when executed on a GPU instead of a CPU. This is becoming increasingly true as graphics card vendors such as NVIDIA and AMD are now developing more graphics card for high performance computing (HPC) such as the NVIDIA Tesla [64].

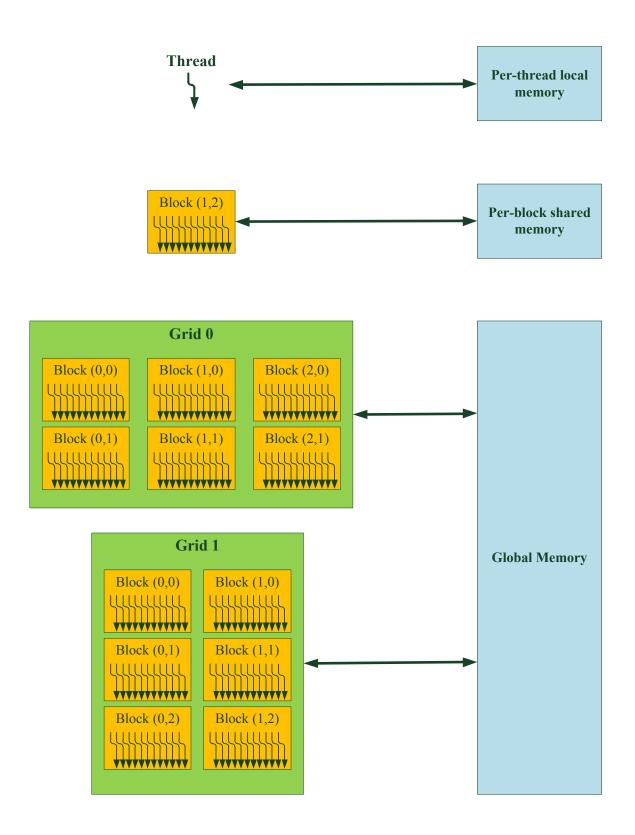

CUDA has a single-instruction multiple-thread (SIMT) execution model where multiple independent threads execute concurrently using a single instruction [62]. CUDA GPUs have a hierarchy of grids, threads and blocks, as shown in Figure 3.1.2.3. Each thread has its own private memory. Shared memory is available per-block and global memory is accessible by all threads. This multi-threaded architecture model puts the focus on data calculations rather than on data caching. Thus, it can sometimes be faster to recalculate than to cache on a GPU.

Figure 3.1.2.3: Hierarchy of threads, blocks and grid in CUDA. (Source: NVIDIA CUDA C programming guide version 4.2, 2012.)

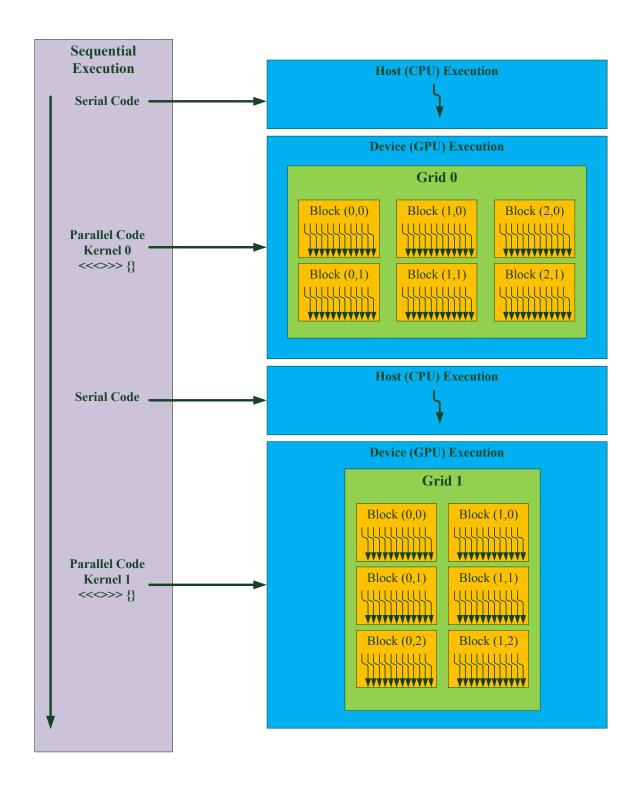

A CUDA program is called a kernel and is invoked by a CPU program. The CUDA programming model assumes that CUDA threads execute on a physically separate device (GPU), which is a co-processor to the host (CPU) that runs the program. CUDA also assumes that the host and device both have separate memory spaces: host memory and device memory, respectively. Because host and device both have their own separate memory spaces, there is potentially a lot of memory allocation, de-allocation and data transfer between host and device. Thus, memory management is a key issue in GPGPU computing. Inefficient use of memory can significantly increase the computation time and mask the speed-ups obtained by the data calculations.

## 3.1.3 Algorithms

There are many classifications of parallel algorithms. According to basic calculation objects, the algorithms can be divided into numerical and non-numerical [65]. FDTD is the study of numerical parallel algorithms, whereas comparing relationships between symbolic processing issues is a non-numerical parallel algorithm, like database operations [66].

The dependencies of parallel processes can be divided into synchronous algorithm, asynchronous algorithm, and independent algorithm. In a synchronous parallel algorithm, the performance of some computation unit tasks requires others' results. Thus, it needs a global clock to control the pace of each part so that each computing unit in various parts of the tasks can simultaneously move forward. In contrast, an asynchronous parallel algorithm does not need every computing unit to wait for the others. They either decide to wait, continue on, or terminate, based on different stages of the calculating process. In an independent parallel algorithm, all computing units are totally irrelevant and do not even start computing tasks simultaneously. For distributed computing, people often use the independent parallel algorithm.

If we focus on the computing tasks, the algorithms can be divided into coarse-grained parallel ones and fine-grained parallel ones [67]. The former is an overall task decomposition into each computing unit, and each unit has a substantial workload of computing tasks and a complex calculation procedure, e.g., the parallel algorithm based on PC clusters. In terms of design, by comparison, a fine-grained parallel algorithm does not care about the relationship between computing tasks and computing units; it is only responsible for assigning the data calculation process to the abstract threads. Single-GPU-based FDTD is a fine-grained parallel algorithm, while multi-GPU-platform FDTD contains a coarse-grained parallel algorithm.

## 3.2 COMPUTATION: FROM CPU TO GPU

Benchmarks that focus on floating point arithmetic (which is most often used in these engineering computations) show that GPUs can perform such computations much faster than the traditional CPUs used in today's workstations – sometimes as much as several times and could even be several orders times faster at the best performance, depending on the specific computation.

## 3.2.1 GPU Computation Capability

The number of floating points operations per second (flops) of a computer is one of the measures of the device's computational abilities. This is an important measure, especially in scientific calculations, as it is an indication of a computer's arithmetic capabilities.

While a high-performance CPU can have a double-precision computation capability of 140 Gflops (Intel Nehalem architecture) [63], an NVIDIA Tesla 20-series (NVIDIA Fermi architecture) GPU has a peak single-precision performance of 1.03 Tflops and a peak double-precision performance of 515 Gflops [64]. Furthermore, the computation capability of a GPU is growing at a much faster pace compared to the CPU.

Although the compute capability of a GPU is impressive when compared to a CPU, it has one significant disadvantage in scientific applications. Not all GPUs fully conform to the IEEE standard for floating point operations [68]. Although the floating point arithmetic of NVIDIA graphics cards is similar to the IEEE 754-2008 standard used by many CPU vendors, it is not quite the same, especially for double precision [61].

# 3.2.2 Accurate Floating-Point Representation

In computers, the natural form of representation of numbers is in binary (1's and 0's). Thus, computers cannot accurately represent real numbers. There are standards to

represent floating-point numbers in computers, the most widely used of which is the IEEE 754 standard. Accuracy in representation of floating point numbers in computers is important in scientific applications.

There have been many cases where errors in floating-point representation have caused catastrophes. One example is the failure of the American Patriot Missile defence system to intercept an incoming Iraqi Scud missile at Dhahran, Saudi Arabia in 1991. This resulted in the death of 28 Americans [69]. The cause of this was determined to be the loss of accuracy from the conversion of an integer to a real number in the Patriot's computer. Other examples of catastrophes resulting from floating-point representation errors can be found at [70].

Therefore, accurate floating-point representation is important in scientific computations. Most CPU manufacturers now use the IEEE 754 floating-point standard. As developments in GPGPUs continue, GPU vendors will inevitably conform to the IEEE 754 standard for floating-point representation as well. This is evident with the newest Fermi architecture from NVIDIA, which implements the IEEE 754-2008 floating point for both single- and double-precision arithmetic [62].

## 3.3 GPU MEMORY STRUCTURE

The CUDA memory hierarchy is shown in Figure 3.3.1. These varied types of memory differ in size, access times, and restrictions. Detailed descriptions of the various memory types are available in the CUDA Programming Guide [61] and the CUDA Best Practices Guide [71].

Figure 3.3.1: Hierarchy of various types of memory in CUDA. (Source: NVIDIA CUDA C programming guide version 4.2, 2012.)

In short, global memory is the largest in size. It is located off the GPU chip and can be accessed by any thread. Because it is off-chip, its access time is the slowest amongst all types of memory. Shared memory is located on-chip, which makes memory access very fast compared to global memory. However, it is limited in size and shared memory access is only on block-level. This means that a thread cannot access shared memory that is allocated outside its block. Local memory is located off-chip and thus has a long latency. It is used to store variables when there are insufficient registers available.

Other types of memory not shown in Figure 3.3.1 are registers and constant memory. Registers are located on-chip, are scarce, and are not shared between threads. Constant memory is located off-chip but is cached. Caching makes memory accesses to constant memory fast, although it is located off-chip.

While global memory is located off-chip and has the longest latency, there are techniques available that can reduce the amount of GPU clock cycles required to access large amounts of memory at one time. This can be done through memory coalescing, which refers to the alignment of threads and memory. For example, if memory access is coalesced, it takes only one memory request to read 64-bytes of data. On the other hand, if it is not coalesced, it could take up to 16 memory requests, depending on the GPU's compute capability. This is further explained in the CUDA Best Practices Guide [71].

#### 3.4 SUMMARY

GPUs have a parallel architecture with the capability of executing thousands of threads simultaneously. This gives the GPU an advantage over the CPU when it comes to intensive computations on large amounts of data. With the CUDA framework, developers have access to CUDA-enabled NVIDIA GPUs. This allows developers to leverage this computation capability for applications other than graphics-rendering. Along with this, CUDA provides a relatively cheap alternative to supercomputing.

#### CHAPTER 4 IMPLEMENTATIONS OF CUDA-ENABLED FDTD

## 4.1 COMPUTE UNIFIED DEVICE ARCHITECTURE

#### 4.1.1 Hardware

The CUDA model is developed by NVIDIA from its GPU parallel programming development. Currently, it is only supported by the production of NVIDIA GPU G80 and above, including G92, GT200, GF100, GF110 of the Fermi series, etc. The market-oriented Geforce series, the graphics workstation-oriented Quadro series, and the scientific computing-oriented Tesla series graphics cards have all supported CUDA programming development. From G80, GPU began to use unified stream processors to replace the original discrete vertex shaders and pixel shaders. In this thesis, we will use GT520 and GT650 to analyze CUDA architecture and performance.

Within GT520 GPU architecture, GPU is made up of TPCs (Texture Processor Clusters). Three streaming multiprocessors (SM) are most relevant with general-purpose computing. An SM is single-instruction multiple-thread processor architecture. Similar to SIMD, it contains command transmitting units, eight streaming processors or scalar processors, two special function processors (SFP), quick-accessible shared memory, and command and constant caches

Arithmetic operation is basically done within SPs, which contains floating-point and integer processing units and registers. Floating-point FMAD/FMUL/FADD and integer ADD/MUL/CMP/MOVE can thus be performed.

There are 30 SMs and 240 SPs in GT520. The operation frequency of SP within GTX280 graphics card settings is 1296MHz. Through its dual-issue commanding emission mechanism, there can be a floating-point multiply-add operation and a multiply operation within each clock cycle, so its theoretical floating point computing capability is up to

1296MHz×240×3Flops=933120MFlops=933.12GFlops, which indicates the amount of floating point operations per second. In comparison, the floating point operation capability of same-period high-end Intel Harpertown architecture 3.2GHz CPU is just 102GFlops. GPU simplifies the control unit and the cache function, further focusing on the floating point computing power, and is therefore more suitable for intensive computations.

The calculation process requires frequent access to the dynamic random access memory (DRAM), namely PC memory and graphics memory. Therefore, the calculation is closely related to another hardware issue: memory bandwidth. For instance, there are 8 internal storage controllers built in GT200 GPU architecture, and each can control two memory chips of 32 bits, so there are 16 GDDR3 memory chips with 32-bit width and 64MB capacity in total. This gives us a 512-bit overall storage, 1GB capacity, and 2214MHz operating frequency. It can be calculated that the GTX280 graphics memory bandwidth is 512bits×2214MHz/8=141696MB/s=141.696GB/s, while the widespread configuration of personal computers was dual channel DDR2 800MHz memory with the bandwidth of 12.8GB/s during the same period.

The CUDA-supported GPUs are divided into several versions with different computing capabilities based on their fundamental structures. This computing power, however, does not represent the speed of floating-point operations or capacity but the support of some CUDA features. For example, the graphic card GTX280 is under the architecture of GT200, and its computing capability is 1.3. Additional characteristics of computing power versions can be found in [61]. GT520 and GT650 graphic cards' specifications are shown in Table 4.1.1.1.

|                  | GeForce GT 520 | GeForce GTX 650 |  |  |

|------------------|----------------|-----------------|--|--|

| GPU Core Details |                |                 |  |  |

| Core Speed       | 810 MHz        | 1058 MHz        |  |  |

| Architecture     | Fermi GF119    | Kepler GK107    |  |  |

| Notebook GPU            | No           | No            |

|-------------------------|--------------|---------------|

| Release Date            | 14 May 2011  | 01 Sep 2012   |

| GPU Memory              |              |               |

| Memory                  | 1024 MB      | 2048 MB       |

| Memory Speed            | 900 MHz      | 1250 MHz      |

| Memory Bus              | 64 Bit       | 128 Bit       |

| Memory Type             | DDR3         | GDDR5         |

| Memory Bandwidth        | 14.4 GB/sec  | 80 GB/sec     |

| GPU Display             |              |               |

| Shader Processing Units | 48           | 384           |

| Actual Shader           | 96           | 384           |

| Performance             |              |               |

| Technology              | 40 nm        | 28 nm         |

| Texture Mapping Units   | 8            | 32            |

| Texture Rate            | 6.5 GTexel/s | 33.9 GTexel/s |

| Render Output Units     | 4            | 16            |

| Pixel Rate              | 3.2 GPixel/s | 16.9 GPixel/s |

| GPU Display Tech        |              |               |

| DirectX                 | 11           | 11.1          |

| Shader Model            | 5.0          | 5.0           |

| Open GL                 | 4.1          | 4.3           |

| GPU Power Requirements  |              |               |

| Max Power               | 29 Watts     | 64 Watts      |

Table 4.1.1.1: GeForce GT 520 and GTX 650 graphics cards brief information.

# 4.1.2 Programming Model

The development using the CUDA parallel programming no longer needs the aid of graphics API. Its syntax is just an extension of C language, following the C language programming structure and basic grammar. Scientific computing researchers who are familiar with the C language can quickly transit to GPU programming.

In a CUDA parallel programming model, it is assumed that the parallel program is executed on independent physical facilities, which are called Device. The facilities are treated as coprocessors of the Host, which runs the C code. In CUDA, each block of threads can be scheduled on any of the available multiprocessors within a GPU, in any order, concurrently or sequentially, so that a compiled CUDA program can execute on any number of multiprocessors, as illustrated by Figure 3.1.2.1. Only the runtime system needs to know the physical multiprocessor count [61].

CUDA C extends C by allowing the programmer to define C functions, called kernels. When called, they are executed N times in parallel by N different CUDA threads, as opposed to only once like regular C functions. The declaration specifier of \_\_global\_\_ is used to define a kernel, and the number of CUDA threads that execute the kernel for a given call is specified using a new <<<...>>> execution configuration syntax. Each thread that executes the kernel is given a unique thread ID. That ID is accessible within the kernel through the built-in threadIdx variable.

The following code shows how it works:

```

#include <cuda_runtime.h>

// Kernel definition

__global___ void addMatrix(float* A, float* B, float* C) {

int i = threadIdx.x;

C[i] = A[i] + B[i];

}

int main() {

```

```

// Kernel invocation with THREAD_NUM threads

addMatrix<<<1, THREAD_NUM>>>(A, B, C);

...

}

```

Listing 4.1.2.1: Sample code adding two matrices A and B within CUDA.

The CUDA programming hierarchy can be seen in Figure 4.1.2.1. Multiple threads will appear as one-, two-, or three-dimensional groups to make up a block. Respectively, a one-, two-, or three-dimensional thread block will be formed. This provides a natural way to invoke computation across the elements in a domain such as a vector, matrix, or volume.

Figure 4.1.2.1: CUDA programming hierarchy.

(Source: NVIDIA CUDA C programming guide version 4.2, 2012.)

The index of a thread and its thread ID relate to each other in a straightforward way: For a one-dimensional block, they are the same; for a two-dimensional block of size (Dx, Dy), the thread ID of a thread of index (x, y) is (x + y Dx); for a three-dimensional block of size (Dx, Dy, Dz), the thread ID of a thread of index (x, y, z) is (x + y Dx + z Dx Dy). We can see an example of this from Listing 4.1.2.2.

```

global void calculate2D(double**A, double**B,

double**C) {

int j=blockIdx.x*blockDim.x+threadIdx.x;

int k=blockIdx.y*blockDim.y+threadIdx.y;

if (j<MAX VALUE && k<MAX VALUE) {</pre>

A[j][k] = B[j][k] + c0*dt/(2*dy)*(C[j][k]-C[j][k-

1]);

}

. . .

}

int main(){

// Kernel invocation with one block of THREAD NUM *

THREAD NUM * BLOCK NUM threads

calculate2D<<<BLOCK NUM, THREAD NUM, THREAD NUM *</pre>

sizeof(double)>>>(A,B,C);

}

```

Listing 4.1.2.2: Sample code: 2D matrix calculation within CUDA.

A kernel can be executed by multiple, equally-shaped thread blocks, so that the total number of threads is equal to the number of threads per block times the number of blocks. The number of thread blocks in a grid is usually dictated by the size of the data being processed or the number of processors in the system, which it can greatly exceed. Blocks can be organized into a one-dimensional, two-dimensional, or three-dimensional grid of thread blocks, as illustrated by Figure 4.1.2.2.

Figure 4.1.2.2: CUDA grid of thread blocks.

(Source: NVIDIA CUDA C programming guide version 4.2, 2012.)

Thread blocks need to execute independently, and it must be possible to execute them in any order, in parallel or in series. The requirement of independence allows thread blocks to be scheduled in any order, across any number of cores, as shown in Figure 4.1.2.1. This enables programmers to write code that scales with the number of cores. Threads within a block can share data through some shared memory and synchronize their execution to coordinate memory accesses. In this way, they cooperate well. More precisely, we can specify synchronization points in the kernel by calling the \_\_syncthreads() intrinsic function, which acts as a barrier at which all threads in the block must wait before any is allowed to proceed. Researchers simply need to decompose the task to the abstract threads, so the program has very good scalability.

CUDA threads may access data from multiple memory spaces during their execution, as illustrated by Figure 3.3.1. Each thread has private local memory and each block has shared memory visible to all threads of the block and with the same lifetime as the block.

All threads have access to the same global memory. There are also two additional readonly memory spaces accessible by all threads, known as constant and texture memory spaces. Global, constant, and texture memory spaces are optimized for different memory usages. Texture memory also offers different addressing modes, as well as data filtering for some specific data formats.

#### 4.1.3 Software Architecture

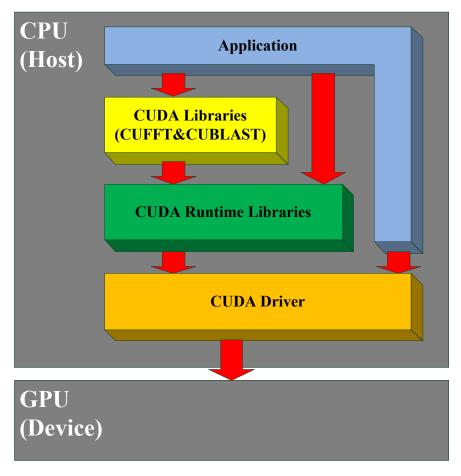

The general software hierarchy of CUDA is shown in Figure 4.1.3.1. Developers can program based on three CUDA APIs. The highest level is two mathematical function libraries encapsulated in a CUDA toolkit: CUFFT (CU Fast Fourier Transform) and CUBLAS (CU Basic Linear Algebra Subroutines). Developers can use these two math libraries to quickly implement many common programming algorithms. In consideration of the versatility, however, they may not be the optimal choice in terms of execution speed.

Figure 4.1.3.1: CUDA software stack.

(Source: http://www.viznet.ac.uk/reports/gpu/7)

Lower than that, there is CUDA Runtime library, which is provided by CUDART dynamic library. All of its APIs have a "cuda" prefix. Runtime offers device management, memory management, workflow management, execution control, texture reference management, and application interface for interoperability with OpenGL and Direct3D, which is the encapsulation based on CUDA Driver library with no special initialization functions. It is done automatically at the first call of Runtime functions.

CUDA Driver API is a handle-based underlying interface provided by NVCUDA dynamic library. All of its APIs have a "cu" prefix. In addition to containing all of the features of Runtime API, Driver API also offers Context management and module management functions. Before calling other Driver API functions, cuInit (unsigned int

Flags) has to be called to initialize everything, create a CUDA context, and associate with the specified devices in the system. Using Driver API to program requires a large amount of code and complex debugging, but in this way some more complicated functions can be implemented through hardware operation. CUDA stipulates that Runtime API and Driver API are mutually exclusive, which means that in any one application, there can only be one of them. Mixed utilization is not allowed.