# PULSE SYNCHRONIZATION AND TIMING RECOVERY IN DIFFERENTIAL CODE-SHIFTED REFERENCE IMPULSE-RADIO ULTRA-WIDEBAND (DCSR IR-UWB) SYSTEM

by

## Tamim Arabi

Submitted in partial fulfillment of the requirements for the degree of Master of Applied Science

at

Dalhousie University Halifax, Nova Scotia April 2013

## DALHOUSIE UNIVERSITY

## DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

The undersigned hereby certify that they have read and recommend to the Faculty of Graduate Studies for acceptance a thesis entitled "Pulse Synchronization and Timing Recovery in Differential Code-Shifted Reference Impulse-Radio Ultra-Wideband (DCSR IR-UWB) System" by Tamim Arabi in partial fulfillment of the requirements for the degree of Master of Applied Science.

|                 | Dated: April 25, 2013     |

|-----------------|---------------------------|

| Co-Supervisors: | Dr. Zhizhang (David) Chen |

|                 | Dr. Hong (Jeffrey) Nie    |

| Readers:        | Dr. Kamal El-Sankary      |

|                 | Dr William Phillins       |

# Dalhousie University

|                                                                                                                                                                                                                                                                 |                                                                     | DATE:                                     | April 25th, 2    | 013         |             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------|------------------|-------------|-------------|

| AUTHOR:                                                                                                                                                                                                                                                         | Tamim Arabi                                                         |                                           |                  |             |             |

| TITLE:                                                                                                                                                                                                                                                          | 2                                                                   | ion and Timing Rec<br>Radio Ultra-Widebar | •                |             |             |

| DEPARTMENT OR SCHOOL: Department of Electrical and Computer Engineering                                                                                                                                                                                         |                                                                     |                                           | gineering        |             |             |

| DEGREE:                                                                                                                                                                                                                                                         | M.A.Sc                                                              | CONVOCATION:                              | October          | YEAR:       | 2013        |

| non-commerc                                                                                                                                                                                                                                                     | s herewith granted to cial purposes, at its di understand that my t | scretion, the above tit                   | tle upon the req | uest of ind | ividuals or |

| The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.                                                                             |                                                                     |                                           |                  |             |             |

| The author attests that permission has been obtained for the use of any copyrighted material appearing in the thesis (other than the brief excerpts requiring only proper acknowledgement in scholarly writing), and that all such use is clearly acknowledged. |                                                                     |                                           |                  |             |             |

|                                                                                                                                                                                                                                                                 |                                                                     | Signatur                                  | e of Author      |             |             |

## Dedication

This thesis is dedicated to my beloved family and to my home country, Syria. May peace prevails there and may the fences choose to sit with us, instead of standing between us.

أُهدي هَذا العَمل لِعائلتي الحَبيبة ولِوَطَني الحَبيب سُورْيَا. فليَعُمَّ السَّلام، ولِتجلس معنا الأسياج بدل أنْ تقِفَ حاجِزاً بينَنا.

## **TABLE OF CONTENTS**

| LIST OF TABLES                          | viii |

|-----------------------------------------|------|

| LIST OF FIGURES                         | ix   |

| ABSTRACT                                | xii  |

| LIST OF ABBREVIATIONS USED              | xiii |

| ACKNOWLEDGMENTS                         | XV   |

| Chapter 1 INTRODUCTION                  | 1    |

| 1.1 Motivation                          | 1    |

| 1.2 Outline                             | 3    |

| Chapter 2 BACKGROUND OF UWB             | 5    |

| 2.1 History of UWB                      | 5    |

| 2.2 Definitions and Concepts            | 5    |

| 2.3 UWB Schemes                         | 9    |

| 2.3.1 Multiband UWB                     | 9    |

| 2.3.2 Impulse Radio UWB                 | 10   |

| 2.4 Advantages of IR-UWB                | 13   |

| 2.5 Applications                        | 15   |

| 2.6 Challenges                          | 16   |

| Chapter 3 IMPULSE RADIO UWB SCHEMES     | 17   |

| 3.1 Rake Receiver                       | 17   |

| 3.2 Transmitted Reference IR-UWB        | 17   |

| 3.3 Frequency-Shifted Reference IR-UWB  | 18   |

| 3.4 CSR IR-UWB                          | 19   |

| 3.4.1 CSR IR-UWB transmitter structure  | 19   |

| 3 4 2 The CSR IR-UWB receiver structure | 20   |

| 3.4.3 Selection of shifting and detection codes | 22 |

|-------------------------------------------------|----|

| 3.5 DCSR IR-UWB                                 | 22 |

| 3.6 Performance Comparison                      | 24 |

| Chapter 4 CURRENT SYSTEM                        | 28 |

| 4.1 DCSR IR-UWB Transmitter Structure           | 28 |

| 4.2 Receiver Structure                          | 32 |

| Chapter 5 SYNCHRONIZATION IN DCSR IR-UWB SYSTEM | 34 |

| 5.1 Non-Coherent Energy Detection               | 34 |

| 5.2 Integrator Circuit as Energy Detector       | 36 |

| 5.2.1 The Integrator                            | 38 |

| 5.2.2 Synchronization                           | 42 |

| 5.3 Implementation and Limitations              | 45 |

| Chapter 6 PULSE SYNCHRONIZATION: NEW PROPOSAL   | 48 |

| 6.1 Introduction                                | 48 |

| 6.2 Design Theory                               | 48 |

| 6.2.1 Synchronization Algorithm                 | 49 |

| 6.2.2 Active Low Pass Filter                    | 50 |

| 6.2.3 Analog-To-Digital Converter               | 52 |

| 6.2.4 FPGA                                      | 53 |

| 6.2.5 VCXO                                      | 55 |

| 6.3 Simulation Results                          | 55 |

| 6.4 Implementation Results                      | 58 |

| 6.4.1 Grounded Co-Planar Waveguides             | 58 |

| 6.4.2 PCB Prototyping and testing results       | 60 |

| 6.4.3 Experimental Test: timing recovery        | 76 |

| 6.5 Conc  | clusion     | 79 |

|-----------|-------------|----|

| Chapter 7 | CONCLUSIONS | 80 |

| 7.1 Futur | re Work     | 81 |

| REFEREN   | CES         | 82 |

## **LIST OF TABLES**

| Table 2.1 FCC emission limits for indoor and outdoor UWB transmission [6]                | 8   |

|------------------------------------------------------------------------------------------|-----|

| Table 3.1 An example of the shifting and detection codes selection from Walsh codes [10] | .22 |

| Table 4.1 Examples for transmitted pulses for different information bits combinations .  |     |

| Table 6.1 the different cases and results in the proposed timing recovery algorithm      | .55 |

## **LIST OF FIGURES**

| Figure 2.1 10-dB Bandwith definition                                                                                                                                      | 6  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.2 FCC Emission Limit for UWB Indoor Systems [5]                                                                                                                  | 7  |

| Figure 2.3 FCC Emission Limit for UWB Outdoor Systems [5]                                                                                                                 | 7  |

| Figure 2.4 MB-OFDM channel allocation versus center frequencies                                                                                                           | 9  |

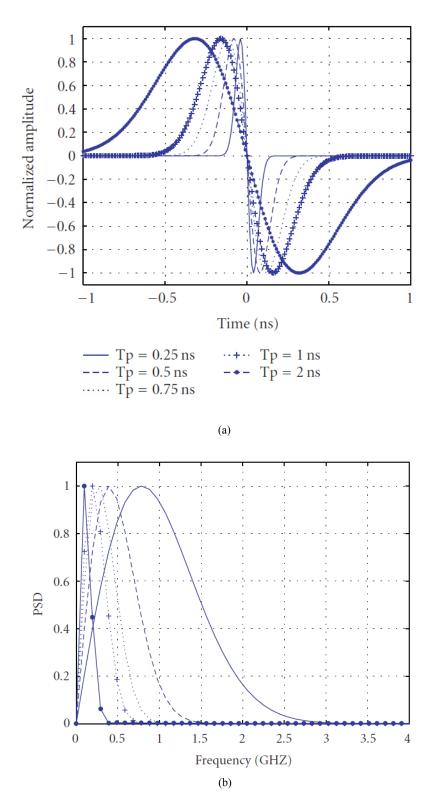

| Figure 2.5 Gaussian Monocycles in (a) time domain, and (b) frequency domain [6]                                                                                           | 11 |

| Figure 2.6 (a) Time domain waveforms and (b) frequency spectrum of $nth$ order Gaussian monocycles, where $tp1=0.7521  ns,  n=2,5,14;  tp2=0.5  ns,  n=2,5$ [8]           | 12 |

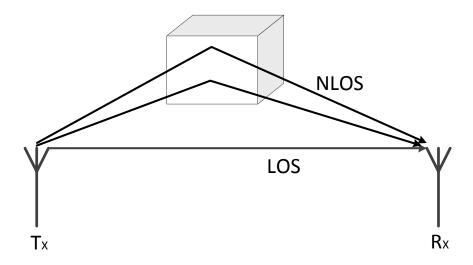

| Figure 2.7 Coexistence of UWB signals with narrowband and wideband signals in the RF spectrum                                                                             |    |

| Figure 2.8 The multi-path phenomenon in wireless links                                                                                                                    | 15 |

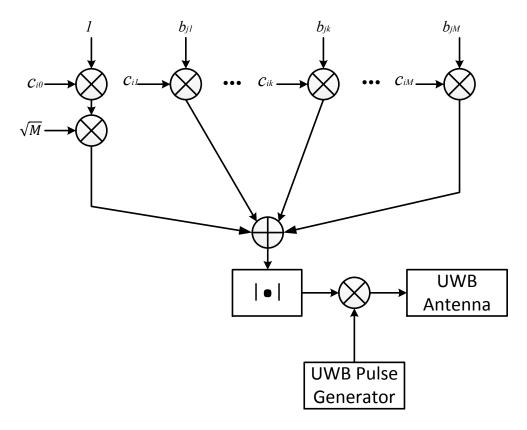

| Figure 3.1 CSR IR-UWB transmitter architecture [10]                                                                                                                       | 20 |

| Figure 3.2 CSR IR-UWB receiver architecture [10]                                                                                                                          | 21 |

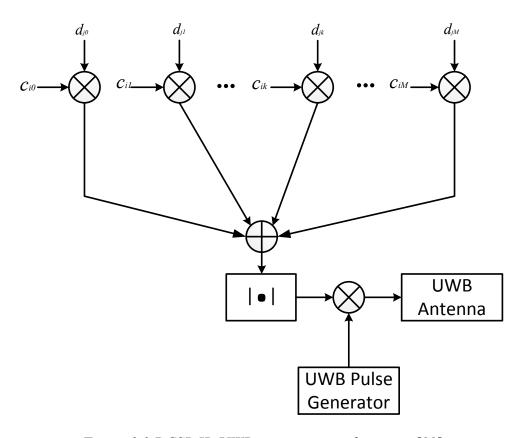

| Figure 3.3 DCSR IR-UWB transmitter architecture [11]                                                                                                                      | 23 |

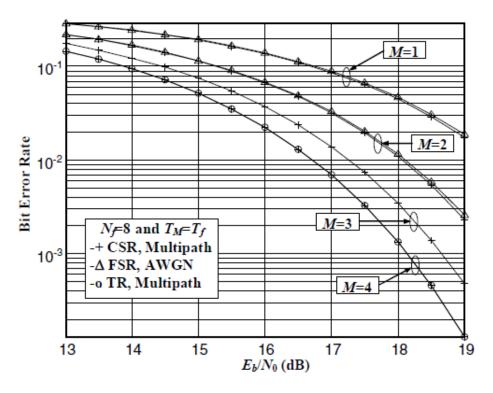

| Figure 3.4 Performance Comparisons of the CSR, TR and FSR transceivers [12]                                                                                               | 25 |

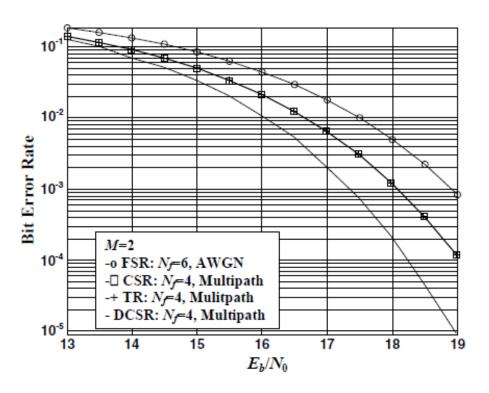

| Figure 3.5 BER performance comparisons when M=2 [13]                                                                                                                      | 27 |

| Figure 3.6 BER performance comparisons when M=3 [13]                                                                                                                      | 27 |

| Figure 4.1 DCSR IR-UWB Transmitter Structure [15]                                                                                                                         | 28 |

| Figure 4.2 Gated pulses with 4.44GHz carrier                                                                                                                              | 29 |

| Figure 4.3 Frequency Spectrum Pulse Response and the FCC Indoor Mask                                                                                                      | 30 |

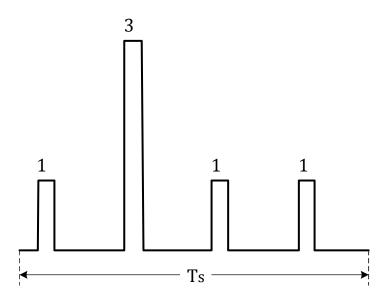

| Figure 4.4 Example of a transmitted symbol: [1 3 1 1]                                                                                                                     | 31 |

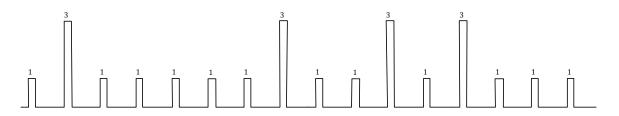

| Figure 4.5 Pulse train with least significant bit first for data bits 11100100 (msb first).                                                                               | 32 |

| Figure 4.6 DCSR IR-UWB receiver architecture                                                                                                                              | 33 |

| Figure 5.1 Block diagram of a basic PLL [18]                                                                                                                              | 35 |

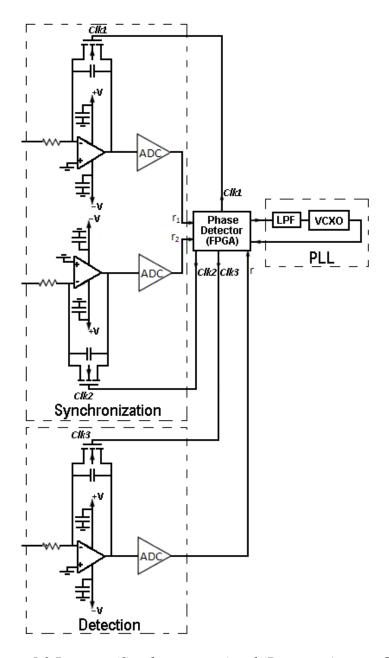

| Figure 5.2 Receiver 'Synchronization' and 'Detection' stages [15]                                                                                                         | 37 |

| Figure 5.3 Op-amp switch-controlled integrator                                                                                                                            | 38 |

| Figure 5.4 Simulation result for the integrator circuit with clock signal (top), input pulse signal (centre), and integrator circuit output (bottom).                     | 40 |

| Figure 5.5 Close-up of the different sections in the integrator circuit response with clock signal (grey), input pulse signal (blue), and integrator circuit output (red) | 41 |

| Figure 5.6 Summary of integrator circuit output results                                                                                                                   | 41 |

| Figure 5.7 Timing diagram of the parallel clocks controlling the three integrator circuits showing their respective integrating and discharging periods | 44 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 5.8 PCB top layer layout for integrator circuit                                                                                                  | 45 |

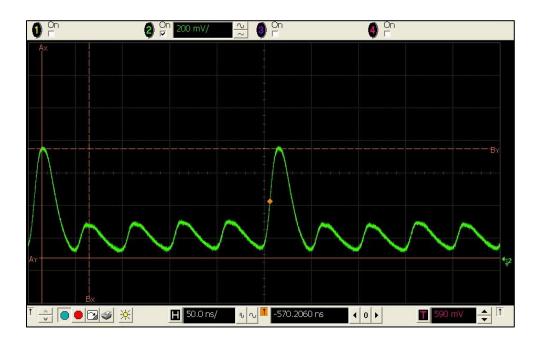

| Figure 5.9 Experimental result for the integrator circuit with inverted low frequency input (3 MHz)                                                     | 46 |

| Figure 5.10 Experimental result for the integrator circuit with high frequency input (20 MHz)                                                           | 47 |

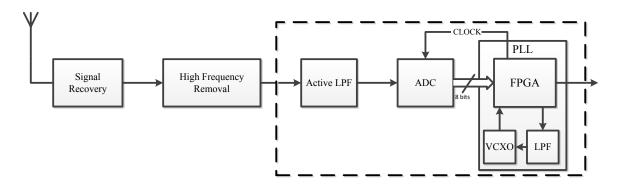

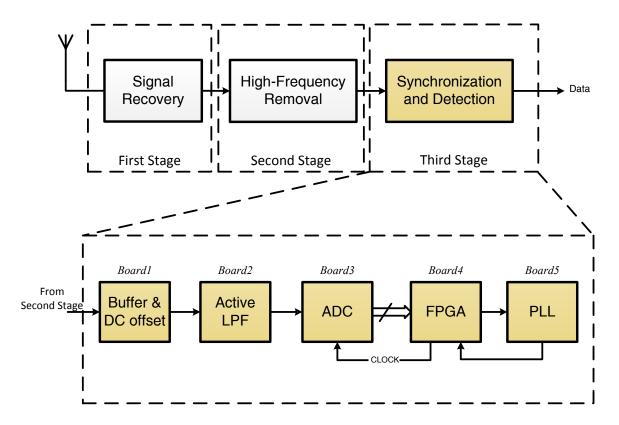

| Figure 6.1 Proposed structure of the DCSR IR-UWB receiver                                                                                               | 49 |

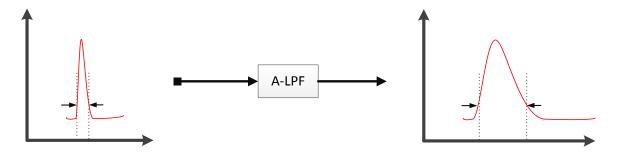

| Figure 6.2 Expansion process using an active LPF                                                                                                        | 49 |

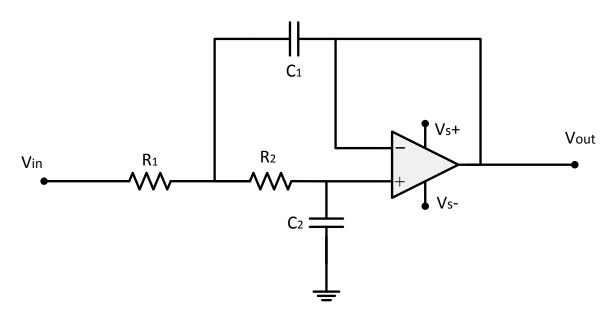

| Figure 6.3 Sallen-Key Low-Pass Filter                                                                                                                   | 51 |

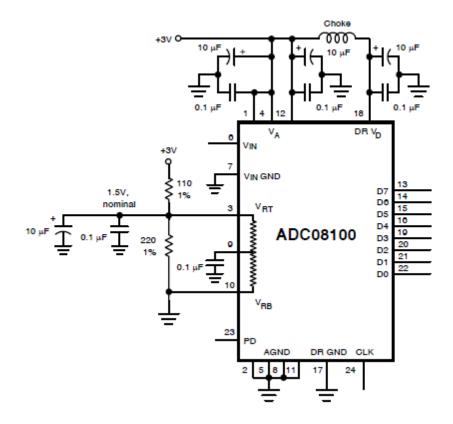

| Figure 6.4 ADC in Reference-Bias Circuit configuration [21]                                                                                             | 53 |

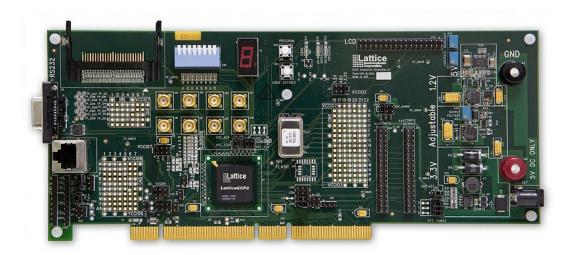

| Figure 6.5 LatticeECP2 Standard Evaluation Board [22]                                                                                                   | 54 |

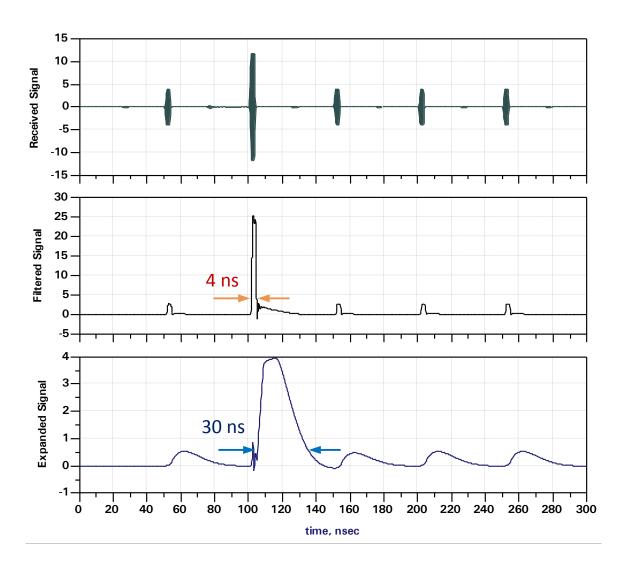

| Figure 6.6 Simulation result showing received signal (top), after high-frequency removal stage (centre), and after ALPF expansion (bottom)              | 56 |

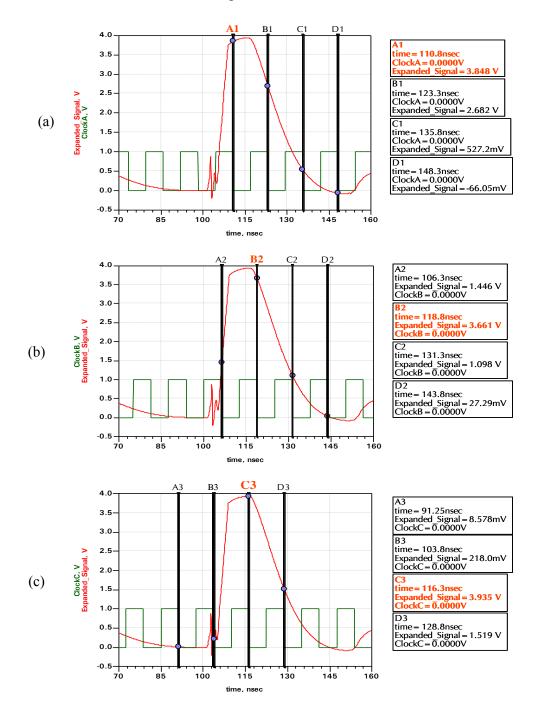

| Figure 6.7 Simulation result showing three possible cases where largest sample is (a) A, (b) B, and (c) C                                               | 57 |

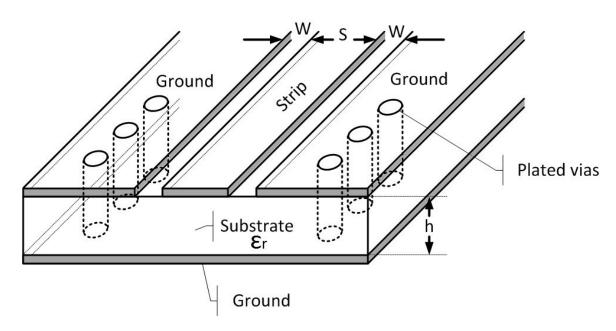

| Figure 6.8 Grounded co-planar waveguide                                                                                                                 | 59 |

| Figure 6.9 The receiver structure in three stages (top) and the building blocks of the third stage (bottom)                                             | 61 |

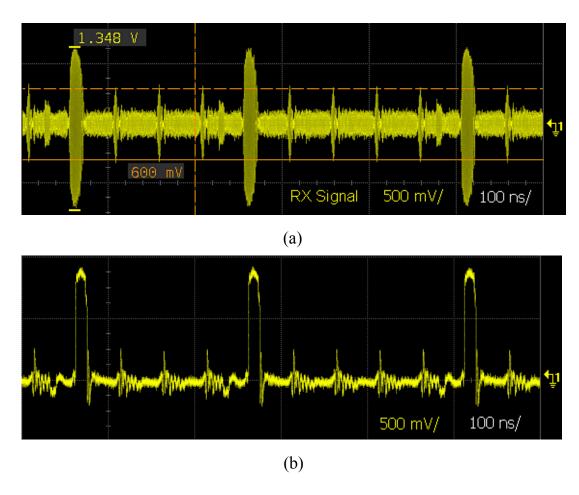

| Figure 6.10 Signal at the receiver (a) before recovery and high-frequency removal stage and (b) after [15]                                              | 62 |

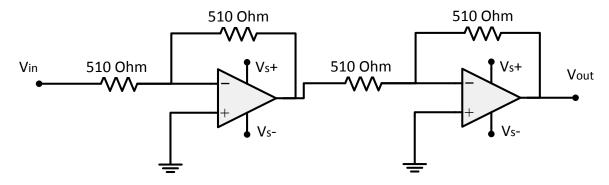

| Figure 6.11 Two-pole active LPF                                                                                                                         | 63 |

| Figure 6.12 PCB top layer layout for two-pole active LPF                                                                                                | 63 |

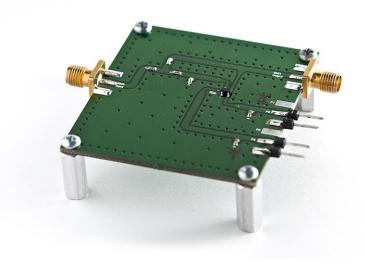

| Figure 6.13 PCB Prototype of the active LPF circuit                                                                                                     | 64 |

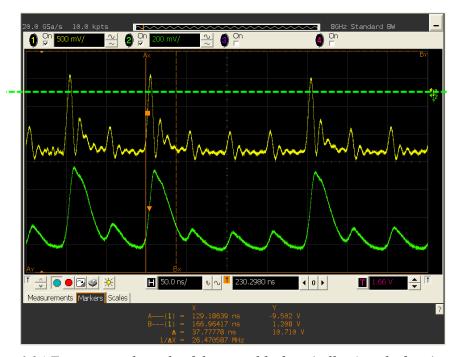

| Figure 6.14 Experimental result of the signal before (yellow) and after (green) the active LPF                                                          | 64 |

| Figure 6.15 Two cascaded op-amp inverters                                                                                                               | 66 |

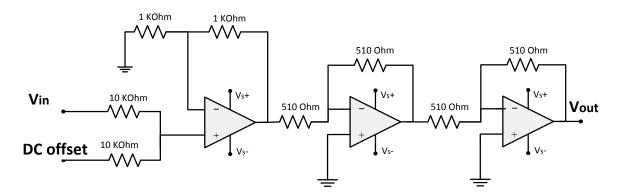

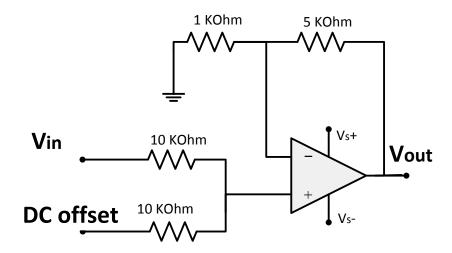

| Figure 6.16 Schematic design for DC buffer with offset circuit                                                                                          | 66 |

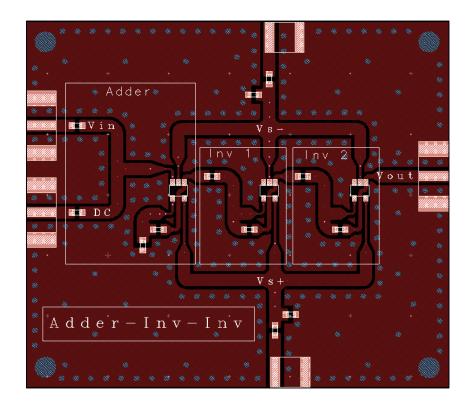

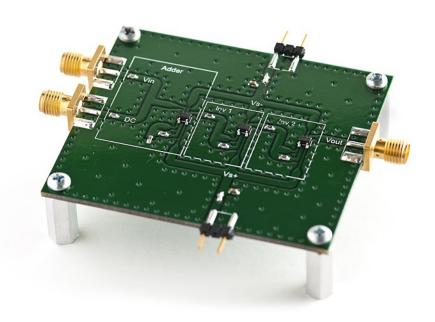

| Figure 6.17 PCB top layer layout for DC buffer offset circuit                                                                                           | 67 |

| Figure 6.18 PCB prototype of the DC buffer offset circuit                                                                                               | 68 |

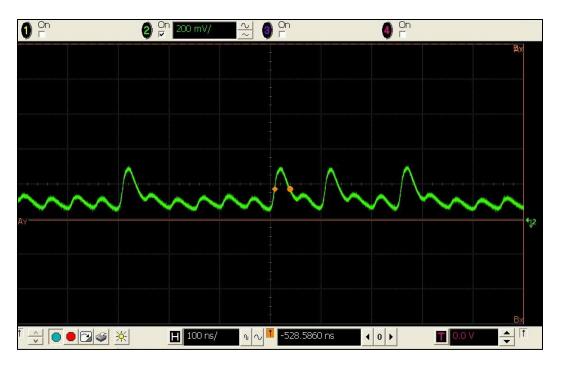

| Figure 6.19 Output signal at the active LPF after adding DC buffer offset circuit                                                                       | 69 |

| Figure 6.20 modified schematic design for buffer with DC offset circuit                                                                                 | 70 |

| Figure 6.21 prototype of the modified buffer with DC offset circuit                                                                                     | 71 |

| Figure 6.22 Improved output signal at the active LPF                                                                                                    | 71 |

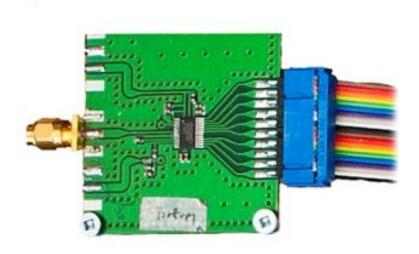

| Figure 6.23 PCB Prototype for the ADC stage [15]                                                                         | 72 |

|--------------------------------------------------------------------------------------------------------------------------|----|

| Figure 6.24 An 80-MHz Sampling clock triggers the ADC to take a sample every 12.5 ns; i.e., four samples from each pulse | 73 |

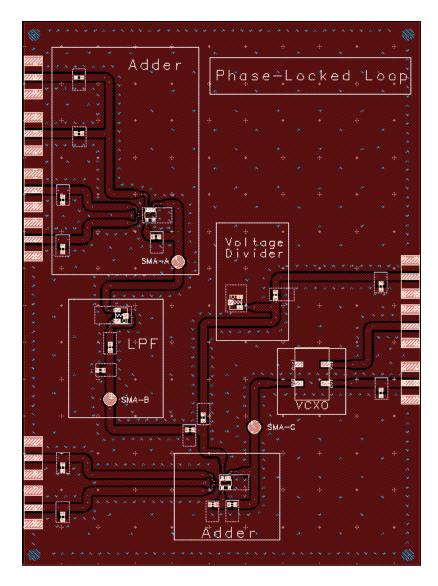

| Figure 6.25 Schematic design for PLL circuit                                                                             | 74 |

| Figure 6.26 PCB top layer layout for the PLL circuit.                                                                    | 75 |

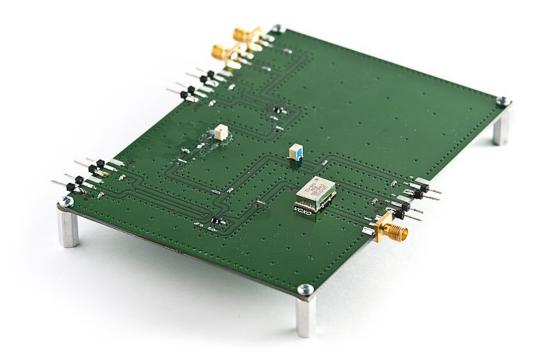

| Figure 6.27 PCB Prototype for the PLL circuit                                                                            | 76 |

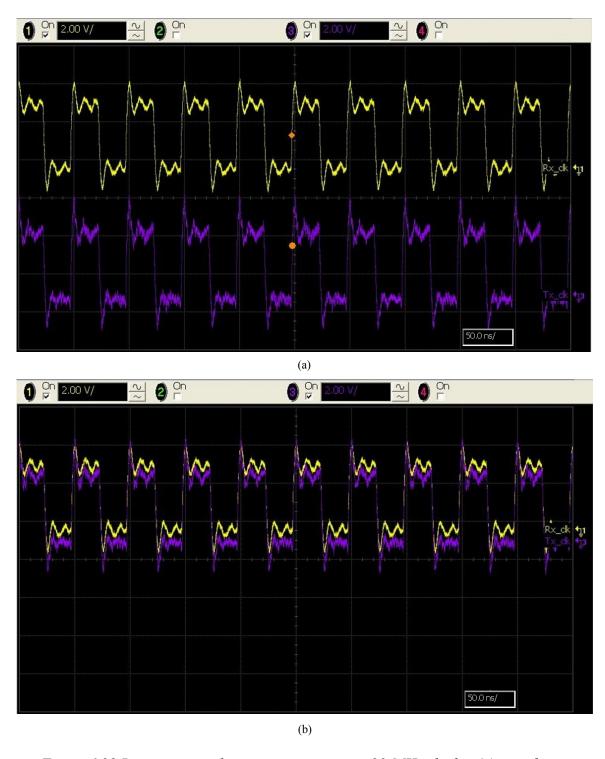

| Figure 6.28 Running a synchronization test on two 20-MHz clocks: (a) out of sync and (b) synchronized                    | 78 |

## **ABSTRACT**

Ultra-wideband (UWB) is a revolutionary radio communication system that utilizes a large portion of the frequency spectrum while maintaining low power levels and high data rates. UWB systems can be used both indoors and outdoors within the power-level masks regulated by the Federal Communications Commission, thus making the technology very versatile. One of the main advantages of UWB is its robustness to multi-path diversity. The technology has attracted the interests of research and industry alike, owing to the possibility of implementing low-power, low-complexity, and low-cost devices.

A widely recognized method of transmitting UWB signals is the use of Impulse Radio technology to transmit information. Impulse Radio Ultra-Wideband (IR-UWB) uses repetitive pulses of very short duration, low duty cycle, and low power levels within FCC regulations. One implementation of IR-UWB pulses in non-coherent transmission is the use of Differential Code-Shifted Reference (DCSR) pulses. In this technique, one of the main challenges at the receiver is pulse-level synchronization that times the received pulses at the right moments for accurate pulse detection.

This thesis will introduce two design proposals in attempt to achieve the pulse synchronization. The first proposal is based on a fast-switch-controlled integrator circuit, while the second focuses on the use of an active low pass filter and phase-locked loop circuits to achieve proper clock timing. Both proposals will be presented, together with schematics, computer-aided simulations, and lab tests results.

#### LIST OF ABBREVIATIONS USED

A/D Analog to Digital

AC Alternating Current

ADC Analog to Digital Converter

ADS Advanced Design System

ALPF Active Low-Pass Filter

AWGN Additive White Gaussian Noise

BER Bit-Error Rate

BPF Band-Pass Filter

BW Bandwidth

CMOS Complementary Metal–Oxide–Semiconductor

CPW Co-Planar Waveguide

CSR Code-Shifted Reference

DC Direct Current

DCSR Differential Code-Shifted Reference

EIRP Effective Isotropic Radiated Power

FCC Federal Communications Commission

FET Field-Effect Transistor

FTT Fast Fourier Transform

FPGA Field Programmable Gate Array

FSR Frequency-Shifted Reference

GCPW Grounded Co-Planar Waveguide

GPS Global Positioning System

HDR High Data Rate

HDTV High-Definition TV

IC Integrated Circuit

IR Impulse Radio

ISI Inter-Symbol Interference

LDR Low Data Rate

LF Loop Filter

LNA Low Noise Amplifier

LOS Line-of-Sight

LPF Low-Pass Filter

MB-OFDM Multi-band Orthogonal Frequency Division Multiplexing

MB Multi-Band

MBOA Multiband OFDM Alliance

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

MPC Multipath Component

NLOS Non Line-of-Sight

OFDM Orthogonal Frequency Division Multiplexing

PC Personal Computer

PCB Printed Circuit Board

PD Phase Detector

PLL Phase-Locked Loop

PRR Pulse Repetition Rate

PSD Power Spectral Density

RF Radio Frequency

RFID Radio-Frequency ID

SMA Subminiature Version A

SMT Surface-Mount Technology

SNR Signal to Noise Ratio

TR Transmitted Reference

UWB Ultra-Wideband

VCO Voltage-Controlled Oscillator

VCXO Voltage-Controlled Crystal Oscillator

VHDL Very-high-speed integrated circuits Hardware Description Language

#### **ACKNOWLEDGMENTS**

I would like to express my deepest gratitude to my supervisor, Dr. Zhizhang Chen, for providing me with the opportunity to conduct my research on this very interesting topic. His encouragement, support, and guidance have helped me in completing this project. I would like to extend my gratitude to my co-supervisor, Dr. Hong Nie, for his constant support and dedication throughout our weekly virtual meetings. I would also like to thank Mr. Blair Macdonald of Cobham Surveillance Ltd. for his valuable input and feedback during this project's early phases.

I would also like to thank my committee members, Dr. Kamal El-Sankary and Dr. William Phillips, for their willing participation in the process, and for the knowledge gained from them.

I would like to thank my colleagues at the RF/Microwave Wireless Research Lab for their support and kindness. Special thanks to Khalid Aldubaikhy for collaborating with me on this project by providing all the coding and algorithms implementation in the FPGA. Thanks to all the faculty and staff within the ECE Department for enriching my experience at Dalhousie.

Finally, I would like to thank my father, Mhd. Sharif Arabi, for his assistance and support; my mother, Diana Al-Ghabra, for being there for me throughout the ups and downs of the years as a grad student; and my brothers and sisters, for their love and support.

## **Chapter 1 INTRODUCTION**

#### 1.1 Motivation

In the communications field, traditional narrowband schemes have been predominant in the past century. Despite their wide prevalence, narrowband systems have been consistently challenged by limitations on their bandwidth and hence data rates. Although pulse-based transmission schemes started already in the late nineteenth century, they were not afforded much attention by research and industry due to the technological limitations of that age. As a result, there was a rapid development of narrowband techniques.

Recently, the ever-increasing demand for higher data rates has led researchers to revisit pulse-based forms of communication. In 2002, the Federal Communications Commission (FCC) released the First Report and Order that laid the ground rules for the commercial use of ultra-wideband communication system. The report also specified what qualifies as a UWB system in terms of bandwidth and transmission power limits. As the pulse-based UWB, or Impulse Radio UWB (IR-UWB), uses short pulses to transmit data, it is superior to narrowband systems in terms of high data rates. Additionally, the short pulses with relatively high periodic frequency make UWB systems highly robust against the multi-path effect. Moreover, low transmit power, low complexity, and low power consumption make impulse-radio ultra-wideband (IR-UWB) a popular choice for researchers and industries involved in the wireless communications field.

The literature presents numerous implementations of the IR-UWB design for non-coherent transceivers. Transmitted Reference (TR) and Frequency-Shifted Reference (FSR) are among the most notable implementations. These transceiver schemes overcome the complexity of channel estimation by transmitting a reference pulse with each data pulse while separating them in time or frequency, respectively.

It was only a matter of time before code-separation of the reference and data pulses were proposed. Code-Shifted Reference (CSR) presented itself as the best alternative to its predecessors, in that CSR overcomes the technical challenges of implying a wideband delay element or separation of the pulses using analog carriers. Because of this, CSR system is low in complexity and provides better performance compared to other systems.

More recently, improvements on the coding algorithms in the CSR system led to the development of the Differential-CSR (DCSR) system, which proved to be superior to the original CSR system and more effective in terms of power consumption. Although an implementation of DCSR transceiver system had been investigated in literature prior to this thesis, there were yet challenges in designing suitable circuits for the synchronization part of the system's receiver. This thesis focuses on that part, and will present design proposals combined with implementation results.

#### 1.2 Outline

This thesis starts in Chapter 1 with a look at the history and background of UWB systems, and their basic definitions and concepts, including the Federal Communications Commission's guidelines. This is followed by introducing the different signaling schemes in UWB systems, with emphasis on the Impulse-Radio scheme. This chapter then specifies the advantages and applications of the IR-UWB systems, and concludes with the current challenges facing the emerging technology.

A thorough investigative review of the evolution of different implementations in the IR-UWB scheme in the literature is presented in Chapter 3. It begins with the methods of using Rake Receiver, Transmitted Reference (TR), Frequency-Shifted Reference (FSR), Code-Shifted Reference (CSR), and emerging variant on the latter, Differentially Code-Shifted Reference (DCSR). The chapter concludes by presenting performance comparisons between above-mentioned methods.

Chapter 4 explains the basic architecture of the DCSR IR-UWB transmitter and receiver and their operation. Included in this chapter is a practical example of the transmitter work and the kind of pulses it produces.

Synchronization in the receiver is introduced in Chapter 5. This chapter presents the design and implementation of the previously proposed, yet not completed, work. It concludes with the limitations of the design proposal.

A genuine design proposal for the synchronization in the receiver is presented in Chapter 6. This chapter provides complete circuits design, schematics, layouts, and PCBs. Computer-aided simulations results are provided, followed with lab experimental testing results. The chapter concludes by providing a proof-of-concept experiment to the design proposal.

Finally, a summary of the research is presented in Chapter 7 and conclusions about this thesis and the research conducted behind it are drawn. This is followed by suggestions to improve the work done and recommendations for any future work on the topic.

## Chapter 2 BACKGROUND OF UWB

## 2.1 History of UWB

Today's wireless communication world is mostly dominated by methods based on the use of sinusoidal waves. However, the primal technique of transmitting information in the early ages of communications was based on pulsed signals [1]. Guglielmo Marconi's first experiments, back in 1894-1896, used spark-gap transmitters to transmit Morse Code messages over a two-mile distance. Despite these early promising beginnings, the limitations on technology in the late nineteenth century and early twentieth century and pressure from industry to develop more reliable communication devices and systems led to the adoption of continuous-wave transmissions.

Almost half a century passed before Marconi's experiments with pulse-based transmission gained interest in technical applications, but for military purposes only. The research and development of impulse radars took place under classified programs. However, the advancement in semiconductor technology in terms of microprocessing and fast switching paved the way for the commercialization of UWB [2].

The shift towards pulse-based communications gained momentum when the Federal Communications Commission (FCC) adopted its First and Order Report in Feb 2002 [3], stating for the first time guidelines allowing intentional emission of UWB signals contained within specified power masks [4]. Therefore, this led to commercial use of UWB technology.

## 2.2 Definitions and Concepts

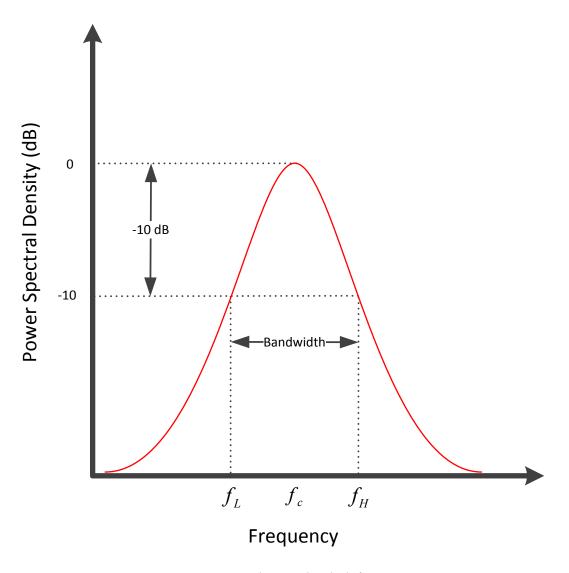

In its report, the FCC stated that UWB signals must have a bandwidth of at least 500 MHz or a fractional bandwidth larger than 20%. Fractional bandwidth  $(B_f)$  is a factor used to categorize signals as ultra-wideband, wideband and narrowband. It is defined as the ratio of the -10dB-point bandwidth (BW) to center frequency  $(f_c)$ , as shown in Equation (2.1).

$$B_f = \frac{BW}{f_c} \times 100\% = \frac{(f_h - f_l)}{(f_h + f_l)/2} \times 100\% = \frac{2(f_h - f_l)}{(f_h + f_l)} \times 100\%$$

(2.1)

where  $f_h$  and  $f_l$  are the highest and lowest cutoff frequencies measured at the -10dB point, respectively. See Figure 2.1.

Figure 2.1 10-dB Bandwith definition

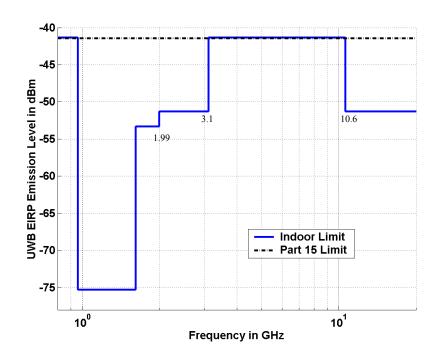

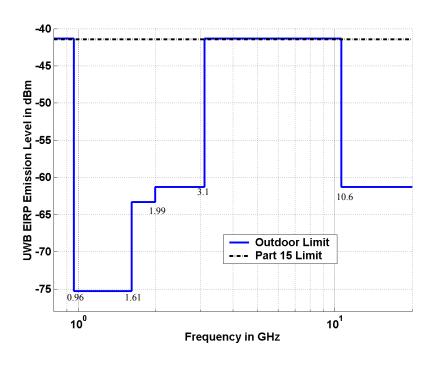

The FCC report also specified upper limits – or masks – on power emission levels for UWB transmission for both indoor and outdoor environments as shown in Figure 2.2 and Figure 2.3, respectively. Table 2.1 shows these levels for each frequency group.

Figure 2.2 FCC Emission Limit for UWB Indoor Systems [5]

Figure 2.3 FCC Emission Limit for UWB Outdoor Systems [5]

Table 2.1 FCC emission limits for indoor and outdoor UWB transmission [6]

| Frequency (GHz) | Indoor EIRP* (dBm/MHz) | Outdoor EIRP<br>(dBm/MHz) |

|-----------------|------------------------|---------------------------|

| 0.96 - 1.61     | -75.3                  | -75.3                     |

| 1.61 – 1.99     | -53.3                  | -63.3                     |

| 1.99 – 3.1      | -51.3                  | -61.3                     |

| 3.1 – 10.6      | -41.3                  | -41.3                     |

| Above 10.6      | -51.3                  | -61.3                     |

\* EIRP: Effective Isotropic Radiated Power

In any case, the maximum transmission power allowed is -41.3dBm/MHz, which translates to  $74 \, nanoWatts/MHz$ . Further reductions in power limits are introduced to protect certain low-power communication systems such as GPS (Global Positioning System) and PCS (Personal Communications Service) leaving a staggering bandwidth of  $7.5 \, GHz$  ( $3.1 \, GHz$  to  $10.7 \, GHz$ ) for UWB applications. If this entire band is optimally utilized, the maximum transmission power ( $P_t$ ) available at the receiver is

$$P_t = 74 \text{ nWatts/MHz} \times 7.5 \text{ GHz} = 0.56 \text{ mWatts}.$$

(2.2)

Such a low transmission power puts UWB systems in the category of unintentional radiators and sets them below the noise floor of a typical narrowband receiver. Thus allowing UWB signals to coexist with current radio receivers with minimal or no interference.

#### 2.3 UWB Schemes

The FCC order did not specify a certain technology for UWB but rather stipulated a minimum bandwidth of 500 MHz and maximum power levels for transmission. This led to two main proposals to access the UWB spectrum: namely, Impulse Radio (IR) and Multi Band (MB). In the following subsections, we will briefly take a look at the MB-UWB scheme, and then thoroughly investigate IR-UWB, which is the scheme this thesis is based on.

#### 2.3.1 Multiband UWB

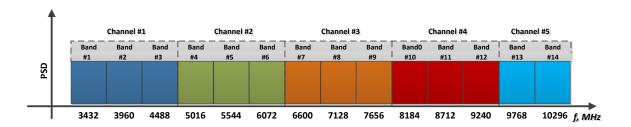

One approach to UWB is the use of the multiband technique. In this approach, the whole 7.5 GHz UWB bandwidth is split into 14 sub-bands (channels) with a respective bandwidth of 528 MHz for each sub band, as shown in Figure 2.4. The first three sub-bands are mandatory for a minimum UWB system design while the other channels are optional for expanded UWB systems.

Figure 2.4 MB-OFDM channel allocation versus center frequencies

In the MB-UWB scheme, systems transmit orthogonal frequency division multiplexing (OFDM) symbols over several sub-bands in a frequency-hopping manner while adhering to the emission power mask as set by the FCC.

Dividing the spectrum into multi bands gives the advantage of avoiding interference with existing transmissions by skipping transmission on a particular band. Another advantage is the relaxed synchronization requirement at the receiver because the pulses are not as narrow as in traditional UWB techniques like Impulse Radio. [2]

Moreover, the channel bandwidth of 528 MHz allows this MB solution to be entirely digitally implemented, allowing for spectrum flexibility using software controls. An all-digital design can be implemented on a single CMOS chip and thus provide efficiency in production times and costs. [1]

Despite its advantages, MB-OFDM scheme suffers some drawbacks. As the demand for higher data rates increases, MB-OFDM systems become more complex due to the need to use higher-order modulation schemes, Fast Fourier Transforms (FFTs), and higher-precision analog-to-digital converters (ADCs), all of which require higher power consumption. [7]

The MB-OFDM proposal is supported by the Multiband OFDM Alliance (MBOA), a consortium of leading consumer electronics and semiconductor companies including, Panasonic, Philips, Sony, and Intel among others.

#### 2.3.2 Impulse Radio UWB

In this scheme, very short pulses are generated to be used for data transmission. Several factors play a role in the parameters chosen to generate these pulses. Some of these factors are: spectral bandwidth, amplitude, and pulse shape.

The spectral bandwidth (BW, Hz) of a pulse is inversely related to the pulse duration in time ( $\tau$ , sec). Figure 2.5 shows this relationship for Gaussian monocycle pulses. This relation can be loosely expressed as:

$$BW \approx \frac{1}{\tau} \tag{2.3}$$

Figure 2.5 Gaussian Monocycles in (a) time domain, and (b) frequency domain [6]

These pulses have durations usually in the range of few nanoseconds, resulting in occupying very large spectrum effectively complying with FCC requirement (>500MHz). Spectral amplitude shouldn't exceed FCC's mask of -41.3dBm/MHz, and hence the choice of pulse voltage level is important.

Pulse-shaping is the collective process that produces pulses with spectral amplitude and bandwidth complying with the FCC emission masks. In IR, the most common method of pulse-shaping is by using Gaussian pulses and its derivatives. Examples of n-order Gaussian monocycle pulses are shown in Figure 2.6, where  $t_p$  parameterizes the effective width of the pulse.

Figure 2.6 (a) Time domain waveforms and (b) frequency spectrum of  $n^{th}$  order Gaussian monocycles, where  $t_{p1}=0.7521~ns,\,n=2,5,14;\,t_{p2}=0.5~ns,\,n=2,5$

## 2.4 Advantages of IR-UWB

Due to the nature of the short pulses used, IR-UWB technology has many advantages compared to existing wireless technologies and MB-UWB technology. The main advantages will be discussed in this section.

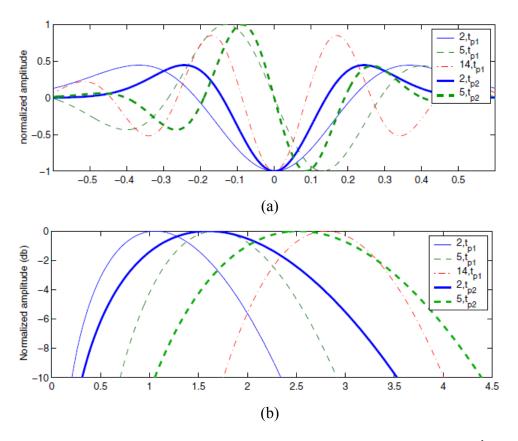

FCC emission mask puts the UWB spectrum below the noise floor (75 nanowatts/MHz), allowing it to co-exist with current radio services with minimal or no interference. Fig... illustrates this point.

Figure 2.7 Coexistence of UWB signals with narrowband and wideband signals in the RF spectrum

Another major advantage of IR-UWB is the improved channel capacity, i.e., high data rates. Channel capacity (C) is expressed in Shannon's communication theory as

$$C = BW \log_2(1 + SNR), \tag{2.4}$$

where BW is the channel bandwidth and SNR is the signal-to-noise ratio. Channel capacity increases with both aforementioned quantities, though more rapidly with the former. The

staggering UWB bandwidth allows for large maximum channel capacity and consequent high data rates.

Another advantage is the ability to work with relatively low signal-to-noise ratio. Referring to Equation (2.4), it can be seen that the channel capacity depends logarithmically on the signal-to-noise ratio. Therefore, in the cases of harsh communication channel environments, UWB systems can work with low SNR while still deliver high data rates. [2]

One of the main advantages of using extremely short pulses with low duty cycle and low power levels is the low probability of interception and detection. This security feature is very important in the exposed wireless medium.

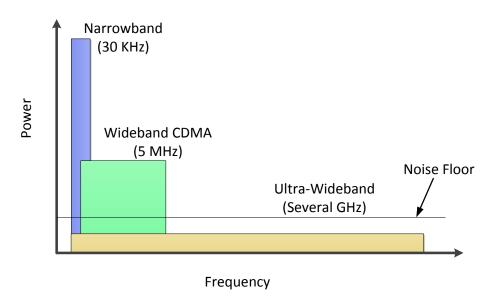

UWB signals in general have the advantage of multipath near-immunity. Multipath is a phenomenon in wireless communication channels caused by multiple reflections of the same transmitted signal from different objects and surfaces. The reflected signals (non line-of sight –NLOS) have different phase than the line-of-sight (LOS) transmitted signals. When NLOS and LOS signals collide at the receiver, the result could be a severely deteriorated signal compared to the original transmitted signal in narrowband due to the continuous waveforms and aggregated out-of-phase signals. Conversely, the short pulses (a few nano-seconds in duration) in IR-UWB leads to very low probability of collision with reflected pulses and thus mitigates multi-path degradation. See Figure 2.8.

Figure 2.8 The multi-path phenomenon in wireless links

## 2.5 Applications

UWB systems are flexible in the trade-off between data rates and range. High data rates (HDR) can be achieved in short range, while longer ranges can be maintained with lower data rates (LDR). This flexibility allows UWB systems to have applications in both categories.

UWB systems are potentially renowned for their high data rates, ranging between 100 *Mbps* – 1 *Gbps* with distances up to 10 meters. Applications in this category include but are not limited to: point-to-point data transfer, as in the case of wireless video streaming between a transmitter (e.g., a video player) and a receiver (e.g., an HDTV monitor); biosensors for hospital patients sending vital signs to a nearby monitor wirelessly; and many consumer electronics products applications.

Applications in the low data rates category include precise location-finding, radio-frequency identification (RFID) tagging and scanning, health monitoring, smart homes, and many other examples [2].

## 2.6 Challenges

IR-UWB systems face many challenges in their receiver architecture, such as detection and synchronization due to the short duration and low power of the pulses, and intersymbol interference (ISI) due to multipath effect. In trying to keep the system simple and avoid channel estimation, many schemes have emerged in the literature with different configurations in the system design. In the following chapter, we take a look at the main schemes that have been developed.

## Chapter 3 IMPULSE RADIO UWB SCHEMES

The receiver's design poses a challenge in the implementation of IR-UWB systems. In this chapter, we take a look at several schemes targeting this challenge that have been proposed in the literature.

#### 3.1 Rake Receiver

When considering UWB transceiver design in multi-path environments, the biggest challenge that arises is the fact that the received signal will be composed of many multi-path components (MPCs). Rake receivers were first proposed for their diversity technique in mitigating multi-path fading effect [6]. The rake receiver structure has a number of "fingers" to capture reflected signals equal to the number of MPCs, with each of these fingers knowing the channel information and including a correlator. Ideally, the number of these fingers would be infinite, but practically they can be limited to select only the strongest MPCs. However, due to pre-required knowledge of the propagation channels and its multi-paths for Rake receivers and the variant nature of UWB systems, rake receivers tend to be complex and thus do not prove promising as a practical choice but a theoretical one.

#### 3.2 Transmitted Reference IR-UWB

The Transmitted-Reference (TR) technique was introduced for its simplicity in avoiding channel estimation requirement. In a TR transmitter, pulses are transmitted in pairs separated by a specific time delay (D) known to both transmitter and receiver. The first pulse is not modulated and is used as a reference to the second, data-modulated, pulse. If D is small enough compared to the coherence time of the channel, it can be said both pulses suffer the same distortion caused by the channel. In this case, the first pulse is used as a reference template for the demodulation of the second pulse at the receiver.

The main advantages of TR systems are that the receivers require no channel estimation and also allow for simple synchronization. The main drawback here is the substantial loss in power; only half of the power is effectively contained in data. Despite the simplicity of a TR receiver, it is still challenged by implementation aspects. In particular, it requires an extremely wide-band delay element, which is difficult to incorporate into low-power integrated systems [9].

## 3.3 Frequency-Shifted Reference IR-UWB

Another scheme introduced is the Frequency-Shifted Reference (FSR) IR-UWB. In FSR, the reference pulse and data pulse are separated in frequency rather than in time, as in TR. Thus, there is no longer a need for a delay element in the receiver. The main motivation behind this scheme is in its relative simplicity in implementing the separation in frequency domain vis-àvis time delay. Multiple data sequences and one reference sequence can be transmitted simultaneously, with each data sequence slightly shifted in frequency. The shift in frequency has to be sufficiently small compared to channel coherent frequency to enable both reference and data sequences to suffer the same channel distortion so that the receiver can detect the data. Correspondingly, at the receiver, the reference pulse sequence will be shifted by the same frequency tones (used at the transmitter) to correlate and to extract the information bits contained in the data pulse sequences. However, the use of analog carriers to enable frequency shifting comes with at a cost; namely, it makes the implementation of the system not only more complex but also affected by frequency offsets (errors) caused by oscillator mismatch between transmitter and receiver. As well, there are phase offsets caused by multipath fading, and amplitude offsets caused by nonlinear amplifiers. As a result, the reference pulse sequence does not provide a suitable template for the data pulse sequence in practice [10].

#### 3.4 CSR IR-UWB

As the two previous schemes introduced reference and data sequences separation in time and frequency domains (TR and FSR, respectively), it was only a matter of time until separation in codes was proposed – Code-Shifted Reference. In CSR scheme, a reference pulse sequence and one or more data pulse sequences are transmitted simultaneously with each sequence coded with specific shifting codes. At the receiver, detection codes are used to extract the information bits from the coded data pulse sequences. Implementing Code shifting instead of time shifting means the CSR-UWB receiver does not require the delay element used in TR-UWB receivers. Moreover, by using digital codes instead of analog carriers as in FSR-UWB, the CSR transceiver avoids the degradations the FSR-UWB system suffers in conjunction of lower system complexity [10].

#### 3.4.1 CSR IR-UWB transmitter structure

The general structure of CSR IR-UWB transmitter is shown in Figure 3.1. The transmitted signal x(t) can be expressed as follows [10]:

$$x(t) = \sum_{j=-\infty}^{\infty} \sum_{i=0}^{N_f - 1} p[t - (jN_f + i)T_f] \left| \sqrt{M}c_{i0} + \sum_{k=1}^{M} b_{jk}c_{ik} \right|,$$

(3.1)

where M is the number of information bits simultaneously transmitted through  $N_f$  frames of UWB pulses;  $T_f$  is the duration between two UWB pulses; p(t) is a UWB pulse with a frequency range from  $W_L$  to  $W_H$  and a duration of  $T_p$  produced by the pulse generator;  $b_{jk}$  is the  $k^{th}$  information bit and is either +1 or -1; and  $c_{ik}$  is the  $i^{th}$  bit of the  $k^{th}$  shifting code.

Figure 3.1 CSR IR-UWB transmitter architecture [10]

The number of information bits M that can be transmitted simultaneously is limited by the number of frames  $N_f$ , i.e., for  $N_f = 2^N$ , M + 1 shifting codes will separate the reference pulse sequence and the M data pulse sequence.

#### 3.4.2 The CSR IR-UWB receiver structure

The general structure of the CSR IR-UWB receiver is shown in Figure 3.2. Basically, the received signal r(t), which is composed of the transmitted signal x(t) and the added channel noise and interferences, passes through a band-pass filter (BPF) to remove any noise and interferences outside the signal frequency range from  $W_L$  to  $W_H$ . The filtered signal,  $\tilde{r}(t)$ , is then squared and integrated from  $(jN_f + i)T_f$  to  $(jN_f + i)T_f + T_M$  to obtain  $r_{ij}$ , where  $T_M$  value ranges from  $T_p$  in the case of an additive white Gaussian noise (AWGN) channel to  $T_f$  in the case of a severe-delay-spread multi-path channel. Subsequently,  $\tilde{r}_{ij}$  are decoded using

M detection codes to extract the M information bits. Equation (3.2) shows the detection codes matrix.

$$\begin{bmatrix}

\tilde{\boldsymbol{c}}_{0} \\

\vdots \\

\tilde{\boldsymbol{c}}_{k} \\

\vdots \\

\tilde{\boldsymbol{c}}_{M}

\end{bmatrix} = \begin{bmatrix}

\tilde{c}_{00} & \cdots & \tilde{c}_{i0} & \cdots & \tilde{c}_{(N_{f}-1)0} \\

\vdots & \ddots & \vdots & \ddots & \vdots \\

\tilde{c}_{0k} & \cdots & \tilde{c}_{ik} & \cdots & \tilde{c}_{(N_{f}-1)k} \\

\vdots & \ddots & \vdots & \ddots & \vdots \\

\tilde{c}_{0M} & \cdots & \tilde{c}_{iM} & \cdots & \tilde{c}_{(N_{f}-1)M}

\end{bmatrix}$$

(3.2)

Figure 3.2 CSR IR-UWB receiver architecture [10]

Finally, signals resulting from the decoding stage are summed independently. The decision to whether the information bits are either '1' or '0' depends on the algebraic sign of the summation result,  $\hat{b}_{jk}$ , such as:

$$\hat{b}_{jk} = \begin{cases} 1, & \text{if } sign(\hat{r}_{jk}) > 0 \\ 0, & \text{if } sign(\hat{r}_{jk}) < 0 \end{cases}$$

(3.3)

## 3.4.3 Selection of shifting and detection codes

The codes selected in [10] to be used for shifting and detection are Walsh codes. Table 3.1 shows an example of the codes that are used in the current CSR IR-UWB system setup.

Table 3.1 An example of the shifting and detection codes selection from Walsh codes [10]

| Code Length | Shifting Codes                                                                                                                                                                             | Detection Codes                                                                             |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|--|

| $N_f = 2$   | $c_0 = [ 1, 1 ]$ $c_1 = [ 1, -1 ]$                                                                                                                                                         | $\tilde{c}_1 = [ 1, -1 \ ]$                                                                 |  |  |

| $N_f = 4$   | $c_0 = [ 1, 1, 1, 1]$ $c_1 = [ 1, -1, 1, -1]$ $c_2 = [ 1, 1, -1, -1]$                                                                                                                      | $\tilde{c}_1 = [1, -1, 1, -1]$ $\tilde{c}_2 = [1, 1, -1, -1]$                               |  |  |

| $N_f = 8$   | $c_0 = [ 1, 1, 1, 1, 1, 1, 1, 1, 1]$ $c_1 = [ 1, 1, 1, 1, 1, 1, 1, 1, 1]$ $c_2 = [ 1, 1, -1, -1, 1, 1, -1, -1]$ $c_3 = [ 1, 1, 1, 1, -1, -1, -1, -1]$ $c_4 = [ 1, -1, -1, 1, 1, 1, 1, -1]$ | $\tilde{c}_2 = [ 1, 1, -1, -1, 1, 1, -1, -1]$ $\tilde{c}_3 = [ 1, 1, 1, 1, -1, -1, -1, -1]$ |  |  |

## 3.5 DCSR IR-UWB

The DCSR IR-UWB system structure in [11] is very similar to its predecessor, CSR IR-UWB, except that data bits  $b_{jk}$  are differentially-encoded to produce  $d_{jk}$  bits which can be defined as:

$$d_{jk} = \begin{cases} 1 & k = 0, \\ \prod_{l=1}^{k} b_{jl} & \forall k \in 1, 2, \dots, M \end{cases}$$

(3.4)

The general structure of DCSR IR-UWB transmitter is shown in Figure 3.3. The following equation defines the transmitted signal x(t) as:

$$x(t) = \sum_{j=-\infty}^{\infty} \sum_{i=0}^{N_f - 1} p[t - (jN_f + i)T_f] \left| \sum_{k=0}^{M} d_{jk} c_{ik} \right|,$$

(3.5)

where M is the number of information bits simultaneously transmitted through  $N_f$  frames of UWB pulses;  $T_f$  is the duration between two UWB pulses; p(t) is a UWB pulse with a frequency range from  $W_L$  to  $W_H$  and a pulse on-time duration of  $T_p$  produced by the pulse generator;  $b_{jk}$  is the  $k^{th}$  information bit and is either +1 or -1; and  $c_{ik}$  is the  $i^{th}$  bit of the  $k^{th}$  shifting code.

Figure 3.3 DCSR IR-UWB transmitter architecture [11]

For a given number of frames  $N_f$ , the number of information bits M that can be transmitted is bound by the limitation [11]:

$$\frac{M(M+1)}{2} \le N_f - 1 \tag{3.6}$$

For M transmitted bits there will be M+1 orthogonal shifting codes used to separate the reference bit from the data bits. Each of these codes has a length of  $N_f$  bits. Throughout this thesis, Walsh codes are used for shifting and detection codes and number of frames used is fixed at  $N_f = 4$ , which means that number of bits to be transmitted simultaneously, M, equals 2: namely,  $b_0$  and  $b_1$ .

# 3.6 Performance Comparison

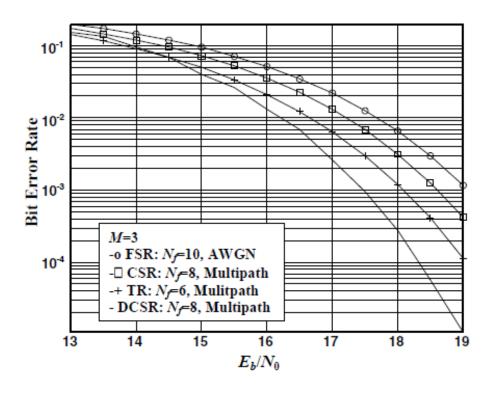

Performance comparisons between the four different IR-UWB transceivers were drawn in [12] and [13]. In [12], the bit-error rate (BER) performance of the code-shifted reference (CSR) transceiver is analyzed and compared with those of the TR and FSR transceivers. Figure 3.4 shows BER comparisons based on computer simulations.

Figure 3.4 Performance Comparisons of the CSR, TR and FSR transceivers [12]

From the above graph, we can see that the TR transceiver shows the best BER performance. The CSR and FSR transceivers can achieve similar performance and this performance increases as the number of information bits M increases. The maximum value of M in the FSR transceiver is limited by the number of analog carriers satisfying some specific relations that has to do with the channel's coherence frequency [14].

This paper shows that, as a low complexity transceiver employing no delay element and no analog carrier, the CSR transceiver can achieve the same BER performance as the TR transceiver and much better than the FSR transceiver.

Bit error rates were estimated and plotted in Figure 3.5 and Figure 3.6 for M=2 and M=3, respectively.

Referring to these performance comparisons figures, we can see that FSR shows the worst BER performance, DCSR the best, and CSR and TR in middle ground with TR slightly outperforming CSR when M=3. For example, at  $E_b/N_0=18$  and M=2, DCSR is less susceptible to BER by 5.5 times compared to CSR and TR, and 25 times compared to FSR.

DCSR also is superior in terms of bit-to-pulse ratio. In terms of power, TR and CSR use half of the available power to transmit the reference pulses only, while DCSR reduces this requirement from 1/2 to 1/(M+1). Both the high-bit-to-pulse ratio and reduced reference pulse power combined allow for the low BER for DCSR systems [13].

Figure 3.5 BER performance comparisons when M=2 [13]

Figure 3.6 BER performance comparisons when M=3 [13]

# Chapter 4 CURRENT SYSTEM

In this chapter, a comprehensive look at the basic structures and functions of the current DCSR IR-UWB system will be provided. The designs are done by previous students in the RF/Microwave research group [15] [16].

### 4.1 DCSR IR-UWB Transmitter Structure

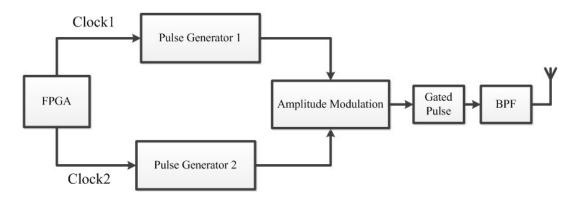

Figure 4.1 shows the block diagram of the DCSR IR-UWB transmitter.

Figure 4.1 DCSR IR-UWB Transmitter Structure [15]

In the first stage, an FPGA (field-programmable gate array) board is programmed to produce two clocks of the same frequency: 20MHz. The clocks are data-modulated by OOK (on-off keying) means. This means when there is a *High* data pulse, *Clock1* produces a pulse with 50% duty cycle, while *Clock2* produces no pulse in the same time period. Consequently, when there is a *Low* pulse; *Clock1* produces no pulse while *Clock2* produces a pulse with 50% duty cycle in the same time period. This will separate the differentially-encoded data *High* pulses from the *Low* ones: *High* pulses will appear in the upper channel, and the *Low* pulses in the lower channel.

In the *Pulse Generator* stage, the modulated clock signals will go through the pulse generation process, where small pulses of 4-ns duration will be produced for every existing clock cycle pulse. The *high* and *low* pulses amplitudes are modified in the following stage:

*Amplitude Modulation*, so that low-to-high amplitude ratio is equal or larger than 1: 3. This is important for code synchronization to work (See subsection 5.1.2 in [15]).

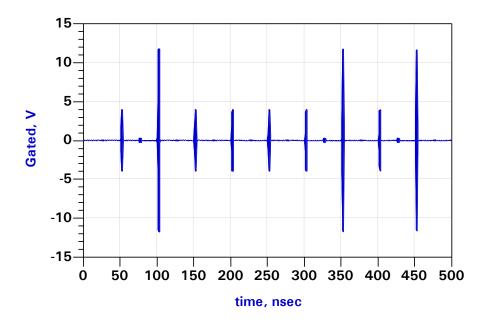

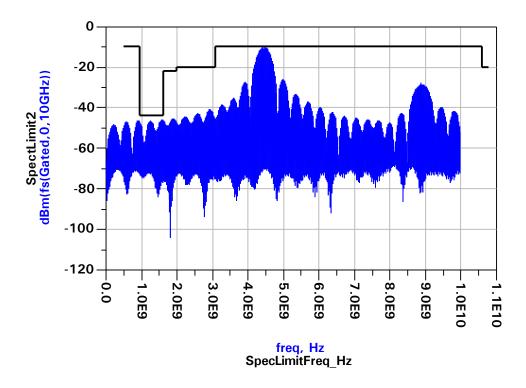

Finally, the pulse train will be multiplied by a carrier sinusoidal signal of 4.44 *GHz*. A sample is shown in Figure 4.2. The carrier is necessary to satisfy FCC power spectral mask (see section 2.2). The frequency spectrum of the sample signal is shown in Figure 4.3. As can be seen, the gated signal spectrum falls within the FCC mask outlines, although it has been shifted to suit the signal transmission. To demonstrate, an example is given below.

Figure 4.2 Gated pulses with 4.44GHz carrier

Figure 4.3 Frequency Spectrum Pulse Response and the FCC Indoor Mask

For: Number of frames  $N_f = 4$ , number of information bits M = 2, information bits  $b_1 = 0$  ('-1') and  $b_2 = 0$  ('-1'), there will be M+1=3 shifting codes of  $N_f = 4$  length each, or  $[1 \times 4]$ . Referring to the transmitter configuration in Figure 3.3, differentially encoded bits  $d_{ji}$  become:

$$d_{j0} = 1$$

$d_{j1} = b_{j1} = -1$

$d_{j2} = (b_{j1})(b_{j2}) = (-1)(-1) = 1$

Shifting codes (from Table 3.1):

$$c_0 = [ 1, 1, 1, 1]$$

$c_1 = [ 1, -1, 1, -1]$

$$c_2 = [1, 1, -1, -1]$$

Finding transmitted signal x(t):

$$(d_0)(c_0) = [ 1][ 1, 1, 1, 1] = [ 1, 1, 1, 1] + (d_1)(c_1) = [-1][ 1, -1, 1, -1] = [-1, 1, -1, 1] + (d_2)(c_2) = [ 1][ 1, 1, -1, -1] = [ 1, 1, -1, -1] = [ 1, 3, -1, 1],$$

Hence,

$$x(t) = |[1, 3, -1, 1]| = [1, 3, 1, 1]$$

This result can be represented by four pulses, creating a symbol of duration  $T_s$  as seen in Figure 4.4.

Figure 4.4 Example of a transmitted symbol: [1 3 1 1]

If we extend this data-encoding process to other possible combinations of data bits we will get the resulting transmitted pulses x(t) which can be summarized in Table 4.1 for two bits. Figure 4.5 shows the resulting pulse train corresponding to data stream of 11100100 (MSB<sup>1</sup> first).

Table 4.1 Examples for transmitted pulses for different information bits combinations

| Information Bits $b_1b_2$ | x(t) |    |    |    |    |

|---------------------------|------|----|----|----|----|

| 00                        | [    | 1, | 3, | 1, | 1] |

| 01                        | [    | 1, | 1, | 1, | 3] |

| 10                        | [    | 1, | 1, | 3, | 1] |

| 11                        | [    | 3, | 1, | 1, | 1] |

Figure 4.5 Pulse train with least significant bit first for data bits 11100100 (msb first)

## 4.2 Receiver Structure

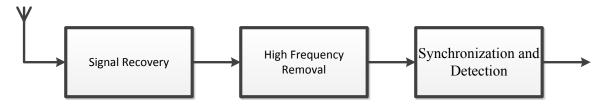

In the receiver-end, as illustrated in Figure 4.6, the received signal first passes through a signal recovery stage. Here, a series of cascaded band-pass filters, followed by an attenuator and a low noise amplifier, filter the signal from any channel noise outside the signal bandwidth, while attenuating and amplifying it. This is followed by the high frequency (radio frequency - RF) removal stage, which is done by mixing the RF signal with another

32

<sup>&</sup>lt;sup>1</sup> MSB: Most significant bit

copy of itself. Unwanted harmonics can be removed later via a low-pass filter. The next stage in this receiver is to pass the baseband signal through the synchronization stage and, eventually, the data detection stage. In the synchronization stage, a circuitry provides the means of synchronizing a local clock from a local oscillator to match the received baseband signal pulse frequency thus achieving synchronization and allowing for the detection stage to detect incoming pulses. By distinguishing *High* and *Low* pulses, this stage produces a digital output mimicking the original signal digital pulse stream. The digital pulse stream will then be fed to a local FPGA for any required digital signal processing.

The above was a description of the receiver in a nutshell. In the next chapter, we will look more closely at the pulse synchronization and detection stages.

Figure 4.6 DCSR IR-UWB receiver architecture

# Chapter 5 SYNCHRONIZATION IN DCSR IR-UWB SYSTEM

In order to provide a low complex receiver in non-coherent systems, an energy detection technique of any sort must be utilized in the synchronization stage. An extracting and decoding process can start after the timing information is recovered.

Synchronization, in general, can be defined as coordinating a transmitter and a receiver to work in unison by timekeeping. In any communication system, synchronization between the receiver and the transmitter is a cornerstone of the receiver's design. Synchronization happens on two levels: time and frame. In the current DCSR IR-UWB system, frame-level synchronization is achieved with the implementation of the shifting and detection codes and its goal is to match the receiver's detection codes with the transmitter's shifting codes, thus enabling correct detection of the transmitted information bits [16]. Details about frame (code) synchronization are not within scope of this thesis.

Time synchronization, or pulse synchronization, on the other hand, is the process of identifying where the detected pulses start and end. A low-complex, non-coherent receiver implementing energy detection as a method for synchronization will be utilized here for its low complexity and hence relative low cost.

# **5.1 Non-Coherent Energy Detection**

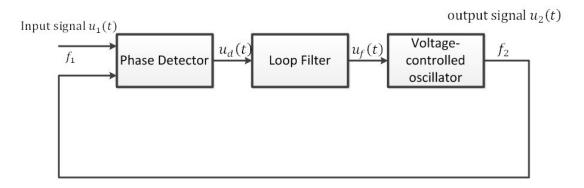

In non-coherent synchronization and detection, receivers work independently from transmitters and with no prior knowledge of channel parameters (channel estimation) [17]. The main part of synchronization in a non-coherent receiver is the Phase-Locked Loop (PLL). PLL is a circuit with of a closed-loop feedback system that synchronizes a voltage-controlled oscillator (VCO) output signal to the input (data) signal in frequency as well as in phase. When synchronized, or locked, the phase error between the VCO output signal and the data input signal is zero or minimal [18]. As seen in Figure 5.1, the three main stages in a PLL are:

-Phase Detector (PD): The PD compares the phase of the VCO output signal  $u_2(t)$  with that of the input (reference) signal  $u_1(t)$  and produces an output signal  $u_d(t)$  that is proportional to the phase error  $\theta_e$ . There are different ways to implement a PD that generally fall into two categories: analog and digital methods.

-Loop Filter (LF): The LF filters out the AC component of  $u_d(t)$  and allows only the DC component to pass as  $u_f(t)$ , which in turn controls the VCO.

-Voltage-controlled oscillator (VCO): The VCO oscillates at frequency  $f_2$ , which is comprised of center frequency  $f_0$  and a voltage-controlled frequency.

Figure 5.1 Block diagram of a basic PLL [18]

Basically, if the VCO center frequency matches the input frequency  $f_1$ , the PD will produce a zero output. The LF will also produce zero output and the VCO output frequency  $f_2$  will remain unchanged and will reflect the input signal frequency; achieving synchronization state. If the input signal frequency changes at any given time, the PD will produce a non-zero output which after filtering, will drive the VCO output frequency up or down, depending on the initial change. The new VCO output will cause the PD to produce an output with a smaller phase error  $\theta_e$ . After some delay, the phase error converges to zero, reaching a 'locking' in the PLL, from which synchronization occurs.

In the next section, we will look at the first approach in implementing the concept of the PLL for synchronization in the current UWB system.

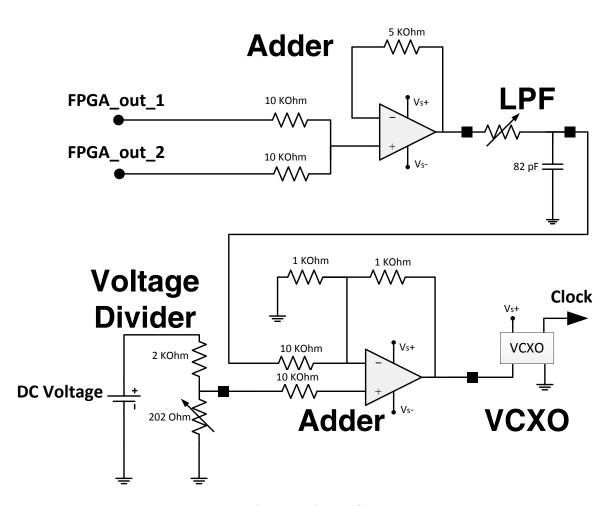

# 5.2 Integrator Circuit as Energy Detector

Based on the concept of a PLL, a circuit is designed to achieve synchronization and detection. This circuit, shown in Figure 5.2, is divided into two stages: synchronization and detection. In each stage, there are several closely identical integrator circuits (Figure 5.3): two for synchronization stage and one for detection stage, each followed by an ADC (Analog to Digital Converter,) and then connected to an FPGA, a loop filter (LF), and a VCXO (voltage-controlled crystal oscillator) to complete the PLL structure.

Figure 5.2 Receiver 'Synchronization' and 'Detection' stages [15]

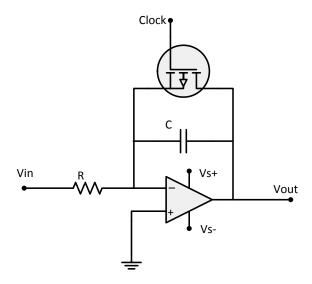

Figure 5.3 Op-amp switch-controlled integrator

## 5.2.1 The Integrator

The building block of the receiver's synchronization and detection board in this design is the operational amplifier integrator circuit, shown in Figure 5.3. The output of this circuit is given by:

$$V_{out} = -\frac{1}{R.C} \int_{0}^{t} V_{in} dt, \qquad (5.1)$$

where the integrating time window is controlled by a MOSFET switch connected in parallel to the feedback capacitor, which, in turn, is controlled by an external clock. An FPGA (Field-programmable gate array) generates this clock with the desired frequency from a local VCXO.

To explain how this integrator works, the following are a computer-run simulation and accompanying results using the Advanced Design Systems 2009 Update 1 software tool.

In this example, for input signal  $V_{in}$  in the integrator circuit shown in Figure 5.3, we use as an impulse p(t) of duration  $T_p = 4 ns$ , and period  $T_f = 50 ns$  (or 20-MHz pulse-repetition frequency), and an amplitude of 2 *Volts*.

$$V_{in}(t) = \sum_{k=-\infty}^{+\infty} 2 p(t - k \times 50 \times 10^{-9})$$

(5.2)

The switch used is an n-channel enhancement-mode MOSFET (Zetex, ZVN4106F [19]). The clock signal applied at the MOSFET's gate has a frequency of 20 MHz. An enhancement mode MOSFET means the n-channel is normally narrow and becomes *enhanced* when a voltage is applied at the Gate (positive in the case of n-type). In other words, when the clock signal applied at the Gate ( $V_{GS}$ ) is low, the switch is "OFF", effectively blocking any current flow which will allow the capacitor to charge in the presence of an input signal (at the source), or else keep the initial charge in the integrator capacitor. However, when  $V_{GS}$  clocks high, the MOSFET switches "ON" with very low Drain-Source on-resistance  $R_{DS(on)} = 5\Omega$  (for  $V_{GS} = 5V$ ). This will allow the capacitor to discharge. The speed at which the capacitor discharges depends on its capacitance value and the equivalent resistance at which it is connected. Since the goal is to discharge as quickly as possible, a 250 pF-capacitor is an appropriate value to start at. The time constant  $\tau$  is:

$$\tau = R_{DS(on)}$$

.  $C = 5\Omega \times 0.25 \text{ nF} = 1.25 \text{ ns}$  (5.3)

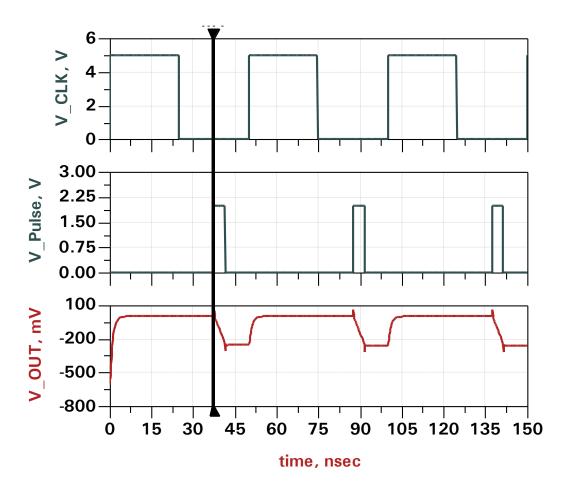

Figure 5.4 Simulation result for the integrator circuit with clock signal (top), input pulse signal (centre), and integrator circuit output (bottom).

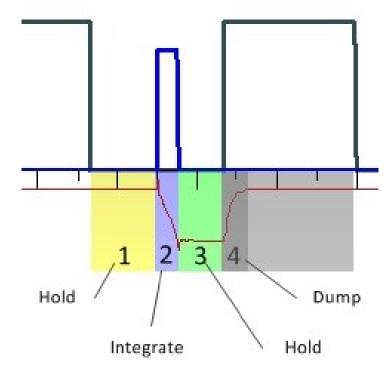

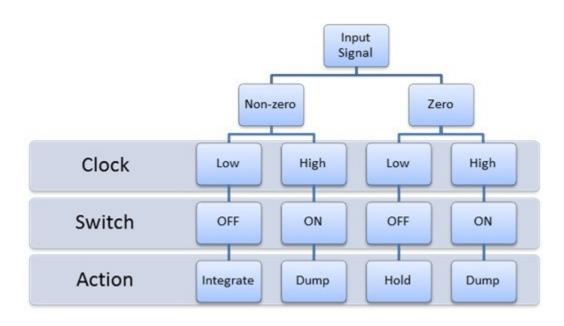

Looking at the results in Figure 5.4 and the close-up at one of the pulse responses in Figure 5.5, different segments in the response can be seen, namely: *integrate* (clock: low, switch: OFF, non-zero input), *hold* (clock: low, switch: OFF, zero input), and *dump* (clock: high, switch: ON, regardless of input). From a close look at the dumping region (segment 4), we find the time constant is 1 ns. These steps are summarized in Figure 5.6.

Figure 5.5 Close-up of the different sections in the integrator circuit response with clock signal (grey), input pulse signal (blue), and integrator circuit output (red)

Figure 5.6 Summary of integrator circuit output results

### 5.2.2 Synchronization

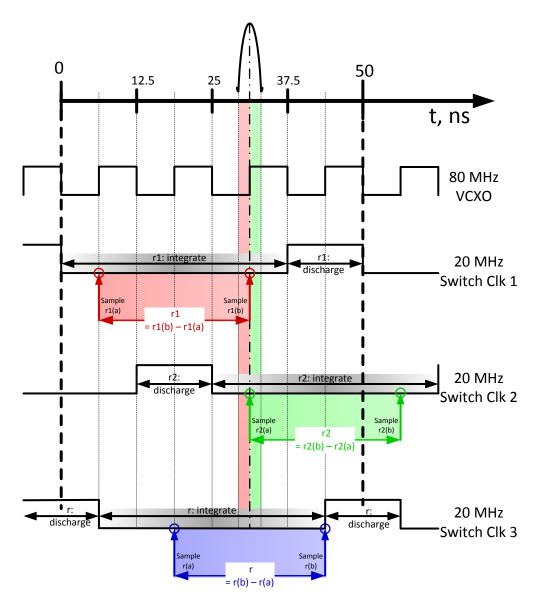

Synchronization at the receiver is needed to achieve proper detection. In simple terms, it means producing a local clock that has the same frequency and phase of the received signal frame. At "locking", this clock will then be used to properly detect the energy in received pulses by the third integrator circuit. Two of the previously discussed integrator circuits will work on a received signal at the same time while connected in parallel. In this stage, the two integrators will integrate the received signal x(t) at two different intervals, or time windows, producing two signals  $r_1(t)$  and  $r_2(t)$ , from the first and second integrator, respectively. The output signals  $r_1(t)$  and  $r_2(t)$  are then sampled using an ADC (analog-to-digital converter) at specific times, as triggered by the falling edge of a sampling clock of 20 MHz, also generated from the FPGA. Two samples from each signal will be taken during each integrating period (when the switch clock is low), specifically 6.25 ns into the integration process and 6.25 ns before it ends. This will produce two samples during any integration period, namely r1(a) and r1(b) for r1(t), and r2(a) and r2(b) for r2(t). The samples will be converted to digital numbers and sent to the FPGA. A subtraction process will occur inside the FPGA to determine the absolute difference representing the two integrated portions of the pulse:

$$r1 = r1(b) - r1(a) \tag{5.4}$$

$$r2 = r2(b) - r2(a) \tag{5.5}$$

The second part in a PLL is to compare the inputs, so a comparison logic process in the FPGA will compare r1 and r2 and produce an output depending on the result. Thus, the different cases that can occur are:

- r1 > r2: This happens when the local clock is *slow* compared to the received signal and will prompt the FPGA to produce a positive (or *high*) output voltage, driving the VCXO frequency *up* to 'catch up' with the received signal frequency.

- r1 < r2: This happens when the local clock is *fast* compared to the received signal and will prompt the FPGA to produce a zero (or *low*) output voltage, driving the VCXO frequency *down* to 'converge' to the received signal frequency.

• r1 = r2: This happens when both the local clock and the received signal have the same frequency and phase. Since the received signal has the frequency of the transmitter clock, we say in this case that the receiver is *synchronized*, or *in-sync*, with the transmitter. This state is also known as *locking*.

In the *locking* state, the receiver is synchronized with the transmitter; thus, the third integrator output (r3), after the same previous process of sampling and subtraction, represents the correct energy content in the frame, hence the pulse. Subsequent steps, such as code-level synchronization, decoding, data representation, etc., can now take place digitally. These steps are beyond the scope of this thesis.

For illustration purposes, Figure 5.7 shows a typical received signal at the input level of the detection board. The signal repetition rate is  $20 \, MHz$ , i.e., one impulse every  $50 \, ns$ . The switch clock frequency is  $20 \, MHz$ . The figure shows the different periods at which each integrator r1, r2, and r3 will process the signal.

Figure 5.7 Timing diagram of the parallel clocks controlling the three integrator circuits showing their respective integrating and discharging periods

# 5.3 Implementation and Limitations

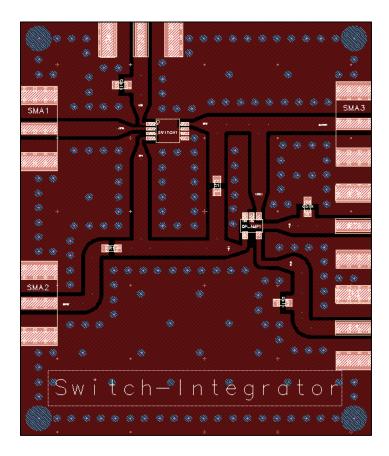

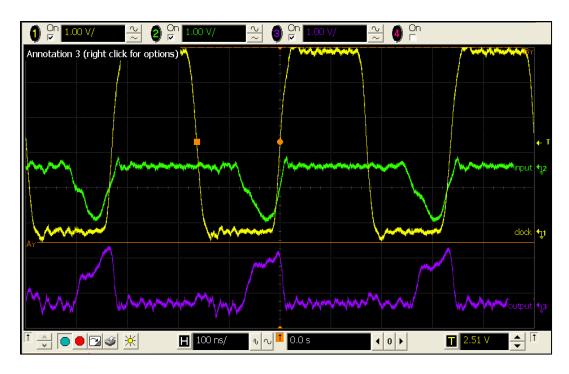

The integrator circuit described in the previous section was constructed on a printed circuit board, as seen in Figure 5.8 (more on PCB design and fabrication in the next chapter.) An experimental test was run on one integrator circuit to test its functionality. All experimental results were taken with Agilent Infiniium DSO81204B oscilloscope. When tested with a pulse train input signal with a low frequency of 3 *MHz* from a signal generator, the result (seen in Figure 5.9) proved similar to that of the simulation; albeit in this test an inverted input was used.

Figure 5.8 PCB top layer layout for integrator circuit

Figure 5.9 Experimental result for the integrator circuit with inverted low frequency input (3 MHz)

Next in this test, the input frequency is increased to resemble that of the real system frequency, i.e., 20 *MHz*, and now is generated from an FPGA. The integrator circuit ceased to give acceptable results, as shown in Figure 5.10. Clearly, the circuit fails to follow the expected behavior of integration. This is due to the MOSFET switch limited capabilities in terms of switching times.

Figure 5.10 Experimental result for the integrator circuit with high frequency input (20 MHz)

Further tests and modifications on input resistor and charging capacitor values resulted only in minor improvements on the capacitor's charging and discharging time, but not enough to make plausible improvements when applying typical UWB-like signals at the input. It has become clear that a different approach had to be sought. A new, genuine, design proposal to the receiver's synchronization stage is introduced in the next chapter.

# Chapter 6 PULSE SYNCHRONIZATION: NEW PROPOSAL

### 6.1 Introduction

In the previous chapter, the design approach to synchronization using integrator circuits was investigated. It was shown that lab tests proved such design efficiency falls short in signals with high, UWB-like, frequencies. In this chapter, a new design approach is proposed, together with simulation tests, physical implementation, and lab tests.

# **6.2 Design Theory**

The limiting factor in the previous design was the speed at which the MOSFET switch could work. Switches are not yet fast enough to work with UWB pulses which are typically in the range of a few nano-seconds. However, since each pulse in DCSR IR-UWB takes up only a small fraction of the frame time period (ideally a 4-ns pulse in a time frame of 50 ns), the duty cycle is very low:

%D.

$$C. = \frac{T_{ON}}{T_{ON} + T_{OFF}} \times 100\% = \frac{4 \text{ ns}}{50 \text{ ns}} \times 100\% = 8\%.$$

(6.1)

The vast unused frame time can be utilized to expand or relax the pulse over the pulse period. If this can be achieved, then pulse-tracking, detection, and synchronization become easier processes in terms of speed. This design, as the previous one, implements PLL in concept to achieve synchronization. After pulse expansion, samples can be taken by an ADC to be evaluated in the FPGA to provide the PD (phase difference) part of the PLL. The last component of the PLL remains the same as before: a VCXO controlling the sampling clock frequency. A block diagram of this design proposal is shown in Figure 6.1.

Figure 6.1 Proposed structure of the DCSR IR-UWB receiver

## 6.2.1 Synchronization Algorithm

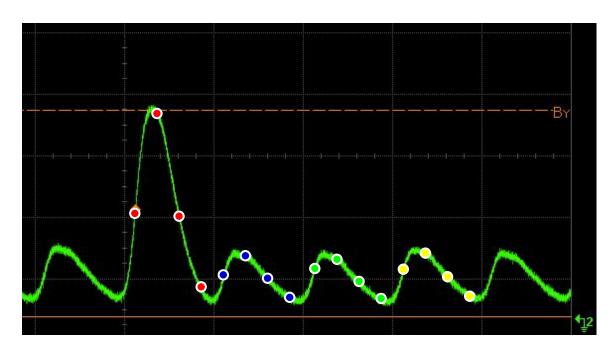

After the received signal goes through signal recovery and high frequency removal stages, it undergoes an expansion process, as shown in Figure 6.1. However, pulses amplitudes ratios are not affected by the expansion process. This is important, as data information is encoded partly in the position of the *high* pulse relative to the other surrounding three *low* pulses (See Table 4.1).

Figure 6.2 Expansion process using an active LPF

The expanded pulses can be sampled effectively with relative ease as compared to original narrow pulses used in the previous approach. Sampling can be done using an ADC similar to the one used in the previous design. To control the ADC sampling process, a clock is generated by the local FPGA with the initial frequency closely matching one quarter of that of the input signal. This clock will trigger the ADC to sample each pulse at four times and convert the samples into digital format. The samples are then stored in the FPGA and then compared to find the sample with the highest value. When the sample with the highest value

is identified, it is then compared against a default sample position. As a result, a decision will be made regarding whether to produce *high* voltage to drive up the VCXO sampling frequency, *low* voltage to drive it down, or *in-the-middle* voltage to maintain it. After some iterations of feedback and frequency adjustment in the PLL, synchronization between the frequency and phase of the received signal and the local oscillator will be reached. The PLL is said to be *locked* in this case.

#### **6.2.2 Active Low Pass Filter**

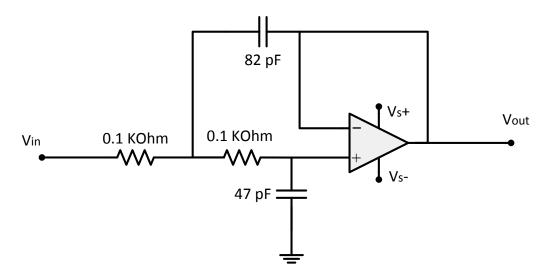

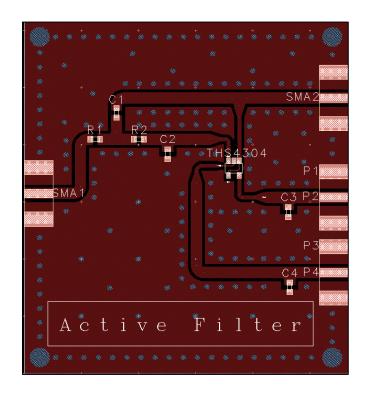

In order to achieve the required signal expansion, active low pass filters (ALPF) are considered for this purpose. ALPFs come in different designs and configurations, but operational amplifiers active filters are of interest for this design, since op-amps have already been used elsewhere in this system and proved efficient. Widely used *Sallen-Key Low Pass Filter*, shown in Figure 6.3, is a good candidate for this design for many reasons. Mainly, the amplifier in this filter works basically as a buffer. This is a good feature since the gain-bandwidth requirement is not of great importance because, as mentioned earlier, signal amplification is not important at this point. Another good point that makes this filter a good choice is that signal phase is maintained throughout the filter.

The filter is comprised of an Op-Amp filter, two capacitors,  $C_1$  and  $C_2$ , and two resistors,  $R_1$  and  $R_2$ . The values of the capacitors and resistors determine the frequency response of the filter. The goal is to expand (widen) the pulse duration from about 4ns to about 35ns, measured near the base.

The cut-off frequency  $f_c$  of the filter in Figure 6.3 is given by:

$$f_c = \frac{1}{2\pi\sqrt{R_1R_2C_1C_2}} \tag{6.2}$$

Figure 6.3 Sallen-Key Low-Pass Filter

Simulations using Advanced Design Systems<sup>2</sup> software showed that the optimum cut off frequencies for best results fall broadly in the range 25-40 MHz (more on simulation results in section 6.3). A frequency of 25.63 MHz was chosen because it allows for convenient choices of resistor and capacitor values in terms of availability. These values are:

$$R_1 = 0.100 k\Omega,$$

$C_1 = 82 pF,$

$R_2 = 0.100 k\Omega,$  and

$C_2 = 47 pF$

Hence, center frequency is:

$$f_c = \frac{1}{2\pi\sqrt{100 \times 100 \times 82p \times 47p}} = 25.63 \, MHz \tag{6.3}$$

<sup>&</sup>lt;sup>2</sup> ADS-2009-Update1

The op-amp used in this filter is a Texas Instrument wideband operational amplifier (THS4304) [20]. An SPICE model of this op-amp is used in computer simulations, as will be shown in section 6.3.

### 6.2.3 Analog-To-Digital Converter

The ADC (analog-to-digital converter) used in this design is an 8-Bit, 20 *Msps* to 100 *Msps*, A/D converter from Texas Instrument (ADC08100) [21].

The 'reference-bias' configuration in Figure 6.4 is used in this design with a single power supple of +3V and GND (ground) connection.

The ADC is controlled by the sampling clock  $CLK_s$  with a frequency  $f_s$  of 80 MHz. This will trigger sampling at the falling edges of the clock, taking samples from the filtered signal with intervals 12.5 ns apart. The ADC08100 has a conversion rate of 20 Msps to 100 Msps, so the required 80 Msps is well within its capacity. The samples taken will be then converted by the ADC to digital numbers of 8 bits each, which then leaves the ADC on an 8-pins parallel output bus at the subsequent rising edge of the clock.

Figure 6.4 ADC in Reference-Bias Circuit configuration [21]

## **6.2.4 FPGA**